RZ/A2M SUB Board RTK79210XXB00000BE 2. Function specifications

R20UT4398EJ0100 Rev.1.00 2-37

2018.10.11

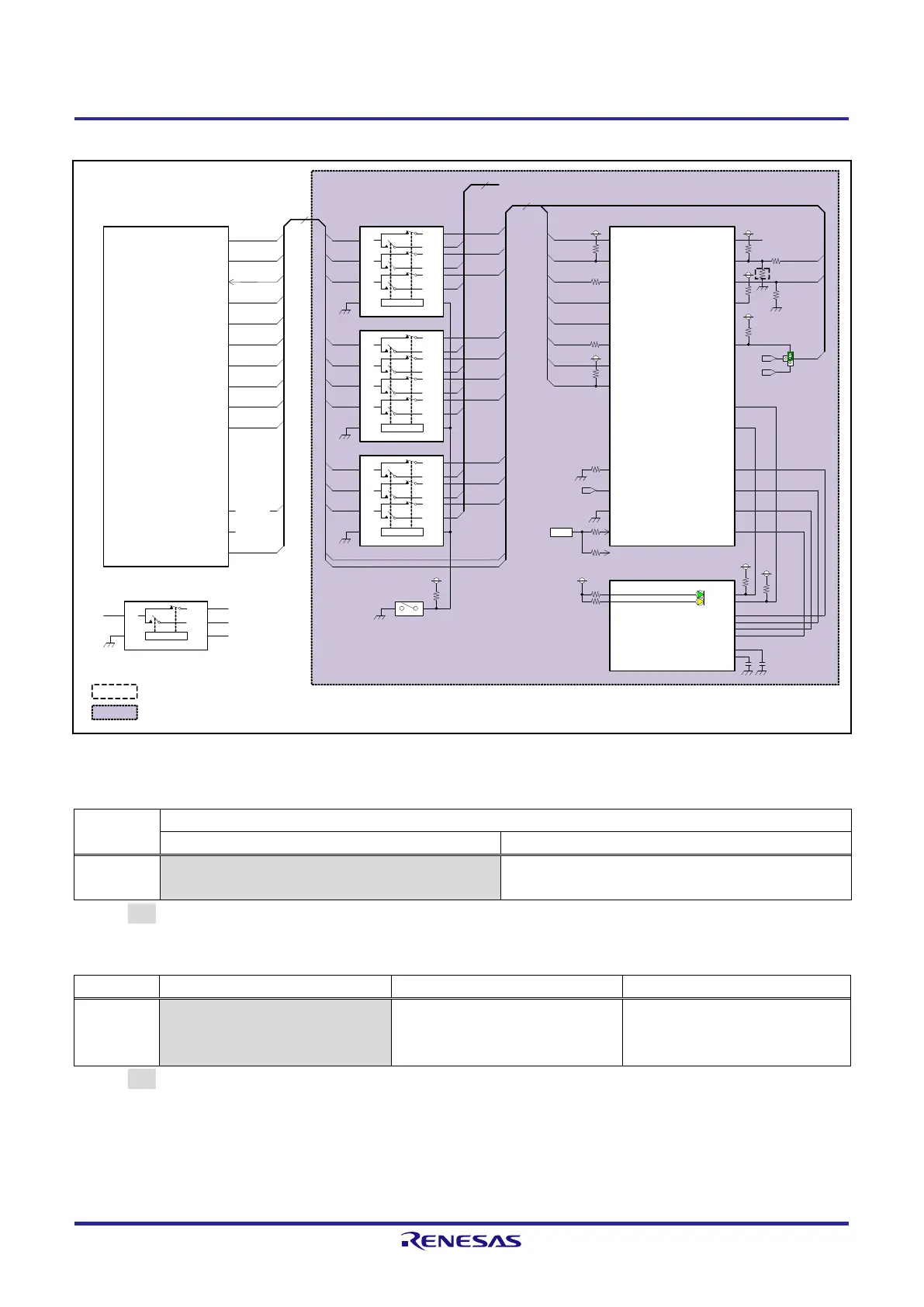

Figure 2.13.1 LAN Interface (Channel 0) Block Diagram

Table 2.13.2 Function Setting Table of DIP Switch SW6-4 for System Setting

P6_[3 :0] and PE_[6 :0] are used as Ethernet PHY1

control pins.

P6_[3 :0] and PE_[6 :0] are used as CEU pins.

(default setting)

[Note] indicates setting functions.

Table 2.13.3 Function Setting Table of Jumper JP1

PJ_1 is used as Ethernet PHY1

signal interrupt pin.

PJ_1 is used as Ethernet PHY2

signal interrupt pin.

PJ_1 is used as IRQ0 switch

(SW3) interrupt pin.

(default setting)

[Note] indicates setting functions.

PE_1

12

P6_1

PE_0

PE_6

P6_3

PE_3

PE_4

PE_2

PE_5

P6_2

Ether1 / CEU(U13)

RXER

RXD0

RXD1

REFCLK

Ether1 / CEU(U16)

MUXOE# S

3A

3B1

3B2

2A

2B1

2B2

1A

1B1

1B2

MUXOE# S

4A

4B1

4B2

3A

3B1

3B2

2A

2B1

2B2

1A

1B1

1B2

Ether1 / CEU(U18)

MUXOE# S

3A

3B1

3B2

2A

2B1

2B2

1A

1B1

1B2

ON(L):A=B1, OFF(H):A=B2

TXD1

TXD0

TXDEN

12

10

To CEU I/F

P6_3

P6_2

P6_1

PE_3

PE_1

PE_2

PE_0

PE_4

PE_5

CRSDV

MDC

MDIO

MDC

TXD[1:0]

TXDEN

REFCLK

RXD1

RXER

CRSDV

RES#

3.3V

INT#

INT#

【A】

RXD0

3.3V

NC

3.3V

CLK

50MHz

(X4)

To EthernetPHY2

3.3V

DIP

SW6-4

RJ45(CN8)

3.3V

NC

3.3V

WOL#

RZ/A2M (U1)

PE_1 / ET0_RXD0/RMII0_RXD0 /

VIO_D7

PE_2 / ET0_RXD1/RMII0_RXD1 /

VIO_D6

PE_3 / ET0_RXER/RMII0_RXER /

VIO_D5

PE_4 / ET0_CRS/RMII0_CRSDV /

VIO_D4

PE_5 / ET0_MDC / VIO_D3

PE_6 / ET0_MDIO / VIO_D2

PE_0 / ET0_RXCLK/REF50CK0 /

VIO_FLD

P6_3 / ET0_TXD1/RMII0_TXD1 /

VIO_HD

P6_2 / ET0_TXD0/RMII0_TXD0 /

VIO_VD

P6_1 / ET0_TXEN/RMII0_TXDEN /

VIO_CLK

PL_0 / MD_CLKS / IRQ4

PJ_1 / IRQ0 (DSTBY release)

WOL#

ON

WOL#

IRQ0

WOL2

TD+

TD-

RD+

RD-

CT1

CT2

LED-G

LED-Y

EthernetPHY1(U27)

MDC

MDIO

MDI+[0]

MDI-[0]

Transmit output

Receive input

MDI+[1]

MDI-[1]

TXD[1:0]

RXD[1]

TXC

TXEN

CRS_DV

RXER / FXEN

LED0 / PHYAD[0]

INTB

LED1 / PHYAD[1]

RXD[0]

LI/O/PD (1:Fiber, 0:UTP)

LI/PU

RXD[3] / CLK_CTL

LI/O/PD (1:REFCLK input, 0:output)

LI/PD

LI/O/PD (1:WOL, 0:LED)

RXDV

LI/O/PD (1:RMII, 0:MII)

PHYRSTB

CKXTAL1

CKXTAL2

RXD[2]

PMEB

TXD[3:2]

COL

RXC

TXER

IO/PD

I/PU

I/PD

I/PD

IO/PU

O/PD

O/PD

O/OD

I/PD

O/PD

I/PD

O/PD

O/PD

RSET

3.3V

1

3

PE_6

MDIO

3.3V

3.3V

Note: Red text indicates a function used.

:Indicates a function not implemented.

:Indicates a SUB board.

JP1

JP2

2.49k±1%

PD_0

(IRQ input # / system

setting selection)

【C】

MUXOE# S

1A

1B1

1B2

【C】

L:A=B1, H:A=B2

IRQ input /

System settings (U6)

【A】

【B】

INT#

【B】

To CPU board SW1

Low

Loading...

Loading...