SDP3B FlashDisk Product Manual

SanDisk SDP3B FlashDisk Product Manual © 1998 SANDISK CORPORATION40

4.4.2 Configuration Option Register (Address

200h in Attribute Memory)

The Configuration Option Register is used to

configure the cards interface, address decoding and

interrupt and to issue a soft reset to the SDP3B

FlashDisk.

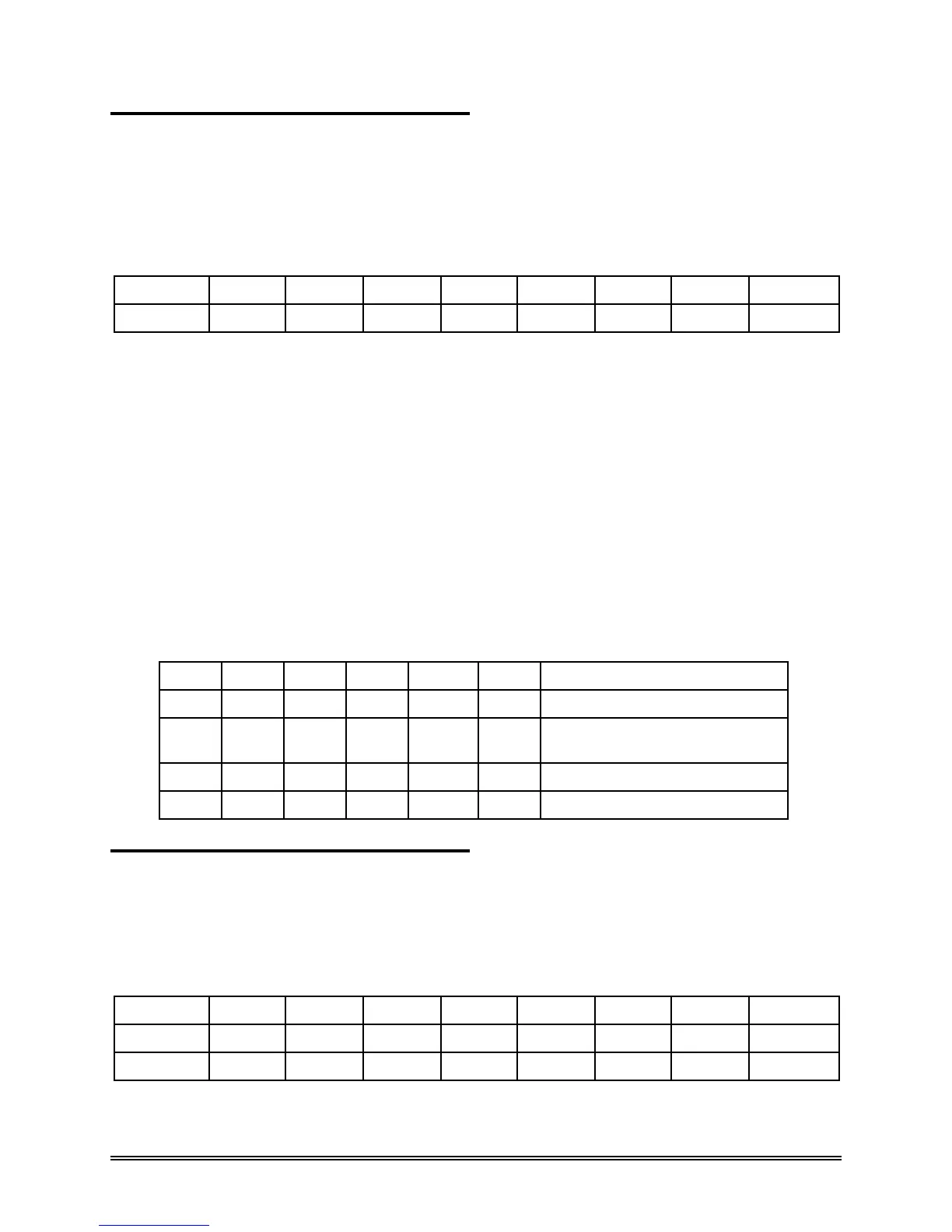

Operation D7 D6 D5 D4 D3 D2 D1 D0

R/W SRESET LevlREQ Conf5 Conf4 Conf3 Conf2 Conf1 Conf0

SRESET Soft Reset - Setting this bit to one (1), waiting the minimum reset width time and returning to zero

(0) places the SDP3B FlashDisk in the Reset state. Setting this bit to one (1) is equivalent to

assertion of the +RESET signal except that the SRESET bit is not cleared. Returning this bit to

zero (0) leaves the SDP3B FlashDisk in the same un-configured, Reset state as following power-

up and hardware reset. This bit is set to zero (0) by power-up and hardware reset. Using the

PCMCIA Soft Reset is considered a hard Reset by the ATA Commands. Contrast with Soft Reset

in the Device Control Register.

LevlREQ This bit is set to one (1) when Level Mode Interrupt is selected, and zero (0) when Pulse Mode is

selected. Set to zero (0) by Reset.

Conf5 - Conf0 Configuration Index. Set to zero (0) by reset. It's used to select operation mode of the SDP3B

FlashDisk as shown below.

Note: Conf5 and Conf4 are reserved and must be written as zero (0).

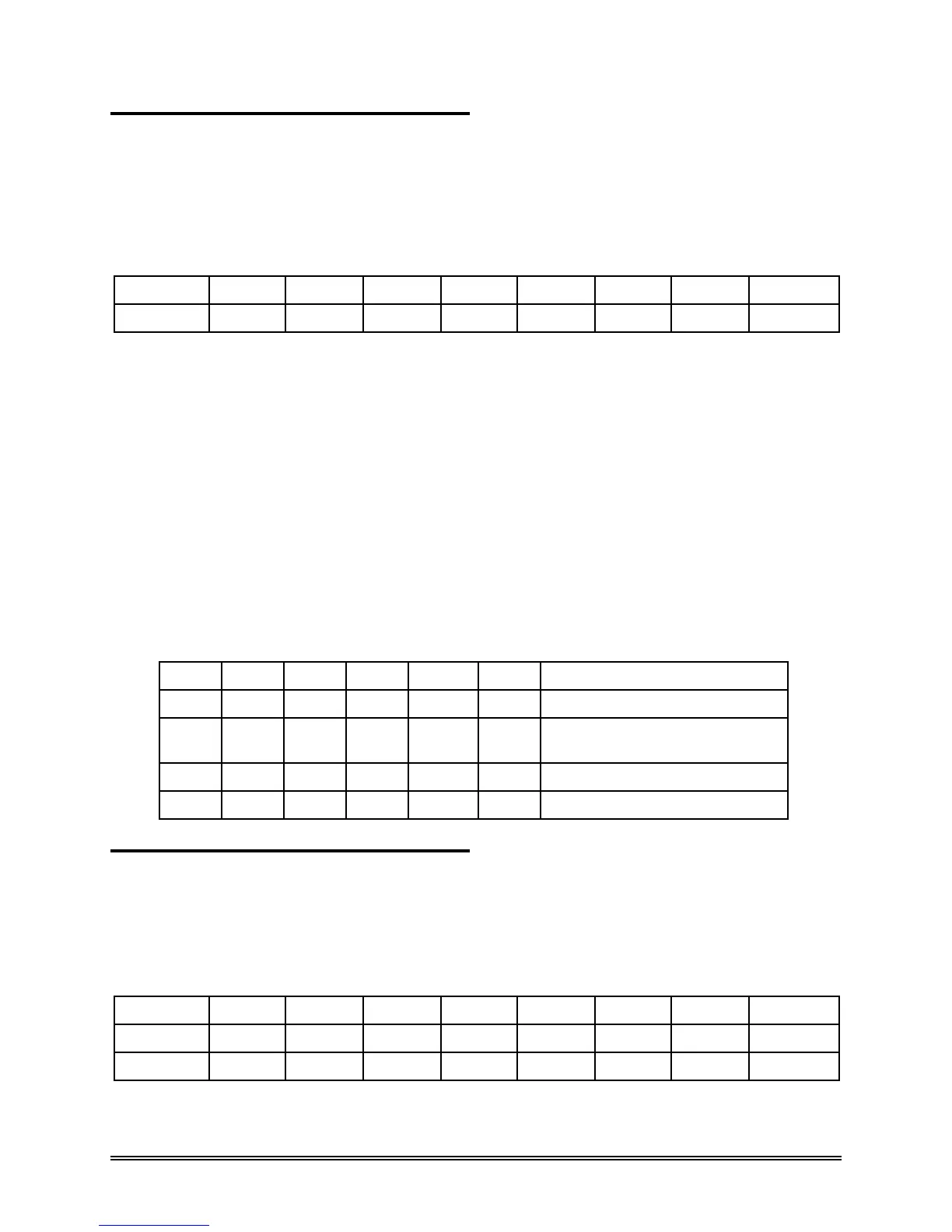

Table 4-13 Card Configurations

Conf5 Conf4 Conf3 Conf2 Conf1 Conf0 Disk Card Mode

0 0 0 0 0 0 Memory Mapped

0 0 0 0 0 1 I/O Mapped, Any 16 byte system

decoded boundary

0 0 0 0 1 0 I/O Mapped, 1F0-1F7/3F6-3F7

0 0 0 0 1 1 I/O Mapped, 170-177/376-377

4.4.3 Card Configuration and Status Register

(Address 202h in Attribute Memory)

The Card Configuration and Status Register

contains information about the Card’s condition.

Card Configuration and Status Register Organization:

Operation D7 D6 D5 D4 D3 D2 D1 D0

Read Changed SigChg IOis8 0 0 PwrDwn Int 0

Write 0 SigChg IOis8 0 0 PwrDwn 0 0

Loading...

Loading...