SDP3B FlashDisk Product Manual

SanDisk SDP3B FlashDisk Product Manual © 1998 SANDISK CORPORATION46

5.0 ATA Drive Register Set Definition and Protocol

The SDP3B FlashDisk can be configured as a high

performance I/O device through:

a.) Standard PC-AT disk I/O address spaces

1F0h-1F7h, 3F6h-3F7h (primary); 170h-

177h, 376h-377h (secondary) with IRQ 14

(or other available IRQ).

b.) Any system decoded 16 byte I/O block

using any available IRQ.

c.) Memory space.

The communication to or from the SDP3B

FlashDisk is done using the Task File registers

which provide all the necessary registers for

control and status information. The PCMCIA

interface connects peripherals to the host using

four register mapping methods. The following is a

detailed description of these methods:

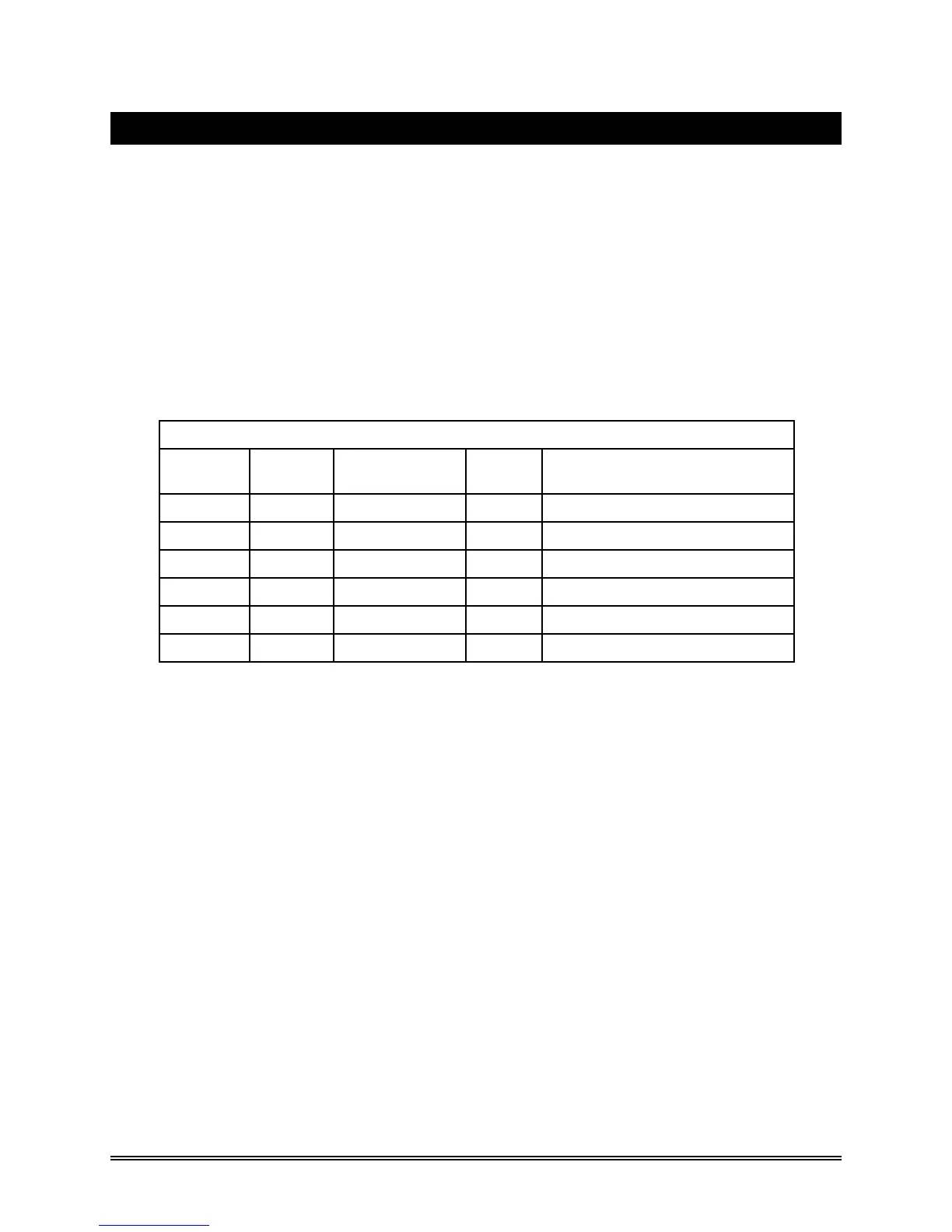

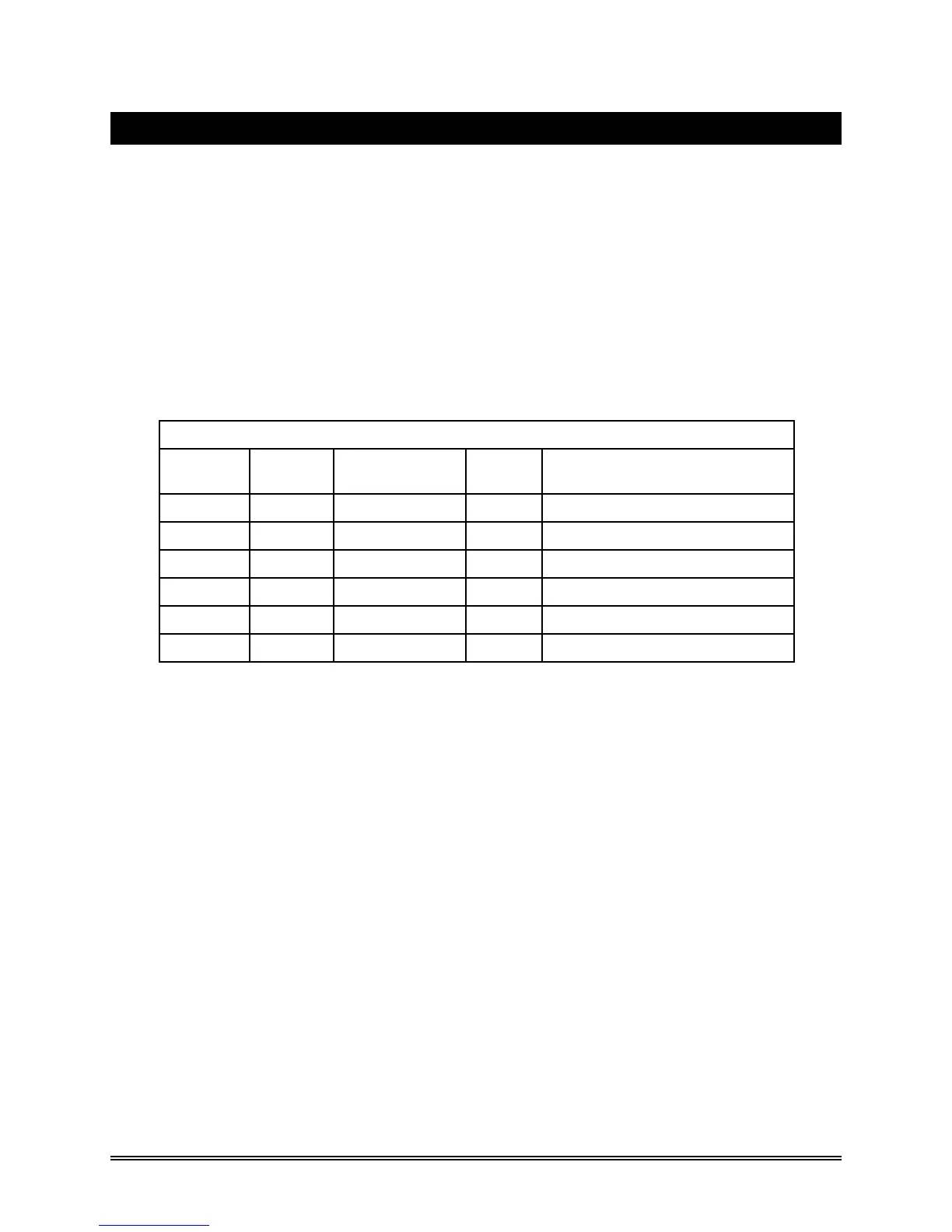

Table 5-1 I/O Configurations

Standard Configurations

Config

Index

IO or

Memory

Address Drive # Description

0 Memory 0-F, 400-7FF 0 Memory Mapped

1 I/O XX0-XXF 0 I/O Mapped 16 Contiguous Registers

2 I/O 1F0-1F7, 3F6-3F7 0 Primary I/O Mapped Drive 0

2 I/O 1F0-1F7, 3F6-3F7 1 Primary I/O Mapped Drive 1

3 I/O 170-177, 376-377 0 Secondary I/O Mapped Drive 0

3 I/O 170-177, 376-377 1 Secondary I/O Mapped Drive 1

Loading...

Loading...