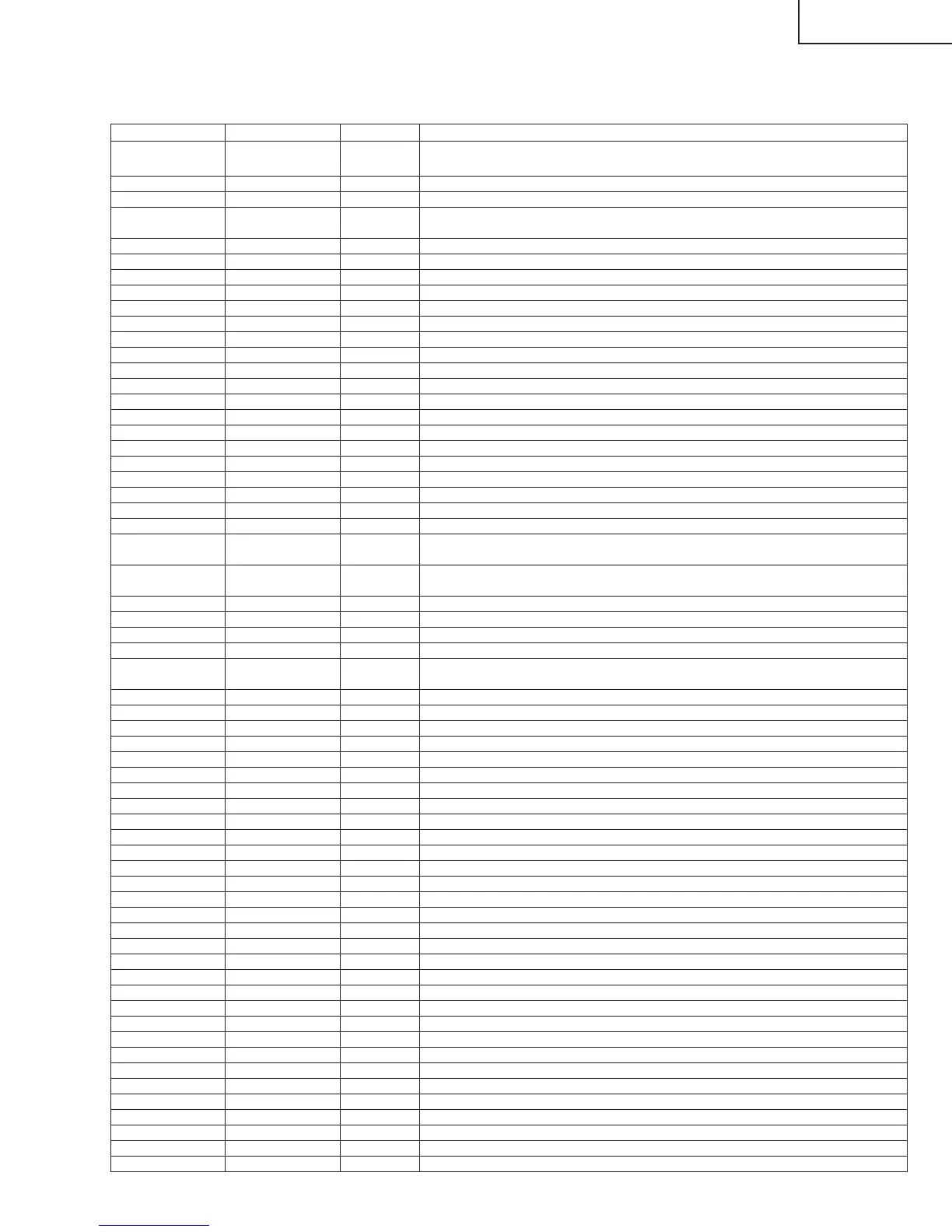

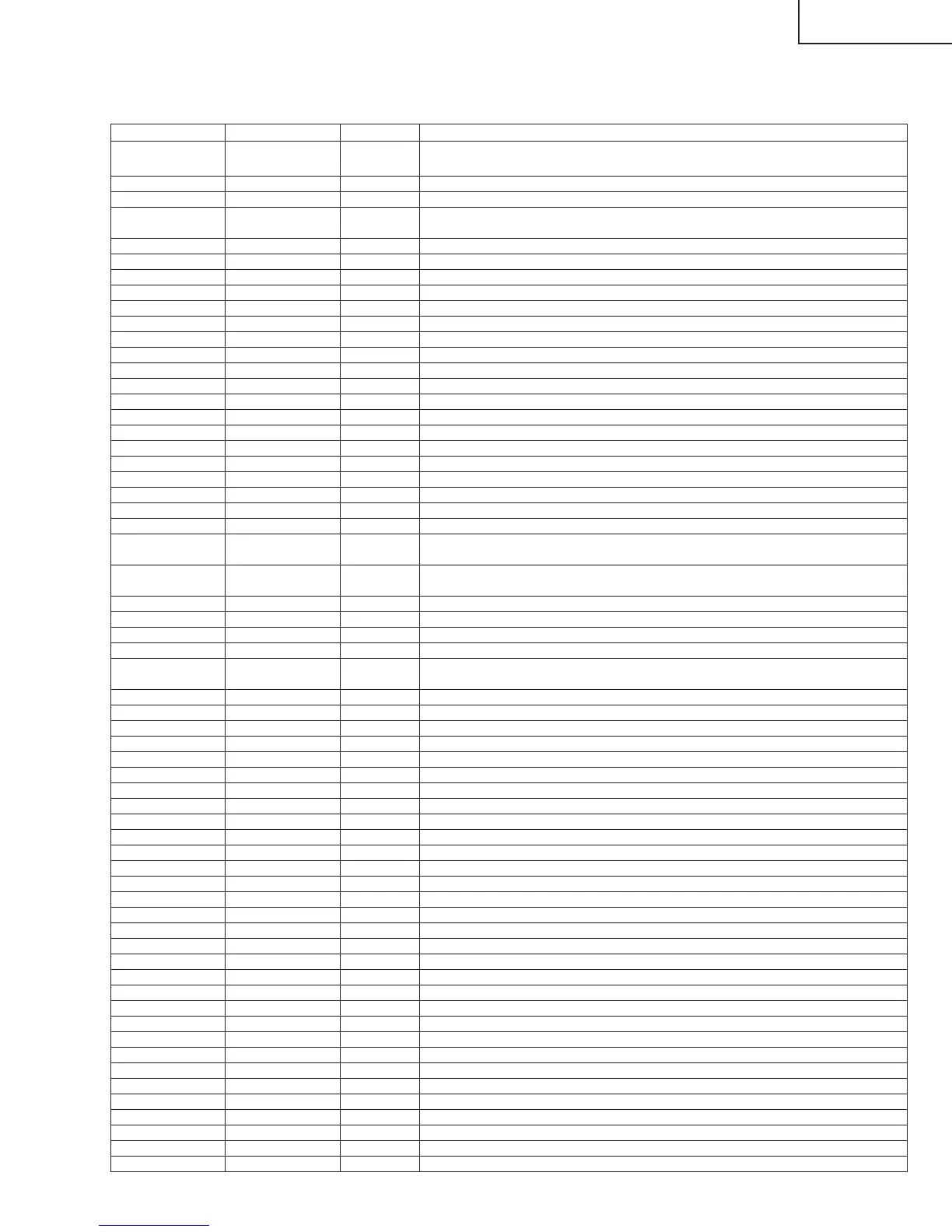

49

LC-30HV4E

Pin No. Pin Name Type Description

34, 36-44, D[15:0] I/O Data bus D [15:0]

46, 48-52

23-26, 28, 30-32 D[23:16/PTA[7:0] I/O Data bus D [23:16] / I/O port A [7:0]

13-18, 20, 22 D[31:24/PTB[7:0] I/O Data bus D [31:24] / I/O port B [7:0]

86, 84, 82, 78-72, A[25:0] O Address bus A [15:0]

70-68-60, 56-53

96 CS0 O Chip select 0/

98 CS2/PTK[0] O/(I/O) Chip select 2 / I/O port K [0]

99 CS3/PTK[1] O/(I/O) Chip select 3 / I/O port K [1]

100 CS4/PTK[2] O/(I/O) Chip select 4 / I/O port K [2]

101 CS5/CE1E/PTK[3] O/(I/O) Chip select 5 / CE1 (area 5SPCMIA)/O port K [3]

102 CS6/CE1B O Chip select 6 / CE1 (area 6SPCMIA)

87 BS/PTK[4] O/(I/O) Bus cycle start signal / I/O port K [4]

118 RAS3U/PTE[2] O/(I/O) RAS (area 3DRAM, SDRAM upper 32MB address) / I/O port E [2]

106 RAS3L/PTJ[0] O/(I/O) RAS (area 3DRAM, SDRAM upper 32MB address) / I/O port J [0]

119 RAS2U/PTE[1] O/(I/O) RAS (area 2DRAM, SDRAM upper 32MB address) / I/O port E [1]

107 RAS2L/PTJ[1] O/(I/O) RAS (area 2DRAM, SDRAM upper 32MB address) / I/O port JE [1]

108

CASLL/CAS/PTJ[2]

O/(I/O) D7-D0 CAS (DRAM)/CAS (SDRAM) / I/O port J [2]

110 CASLH/PTJ[3] O/(I/O) D15-D18 CAS (DRAM) / I/O port J [3]

112 CASHL/PTJ[4] O/(I/O) D23-D16 CAS (DRAM) / I/O port J [4]

113 CASHH/PTJ[5] O/(I/O) D31-D24 CAS (DRAM) / I/O port J [5]

116 CAS2L/PTE[6] O/(I/O) D31-D24 CAS (DRAM) / I/O port J [5]

117 CAS2H/PTE[3] O/(I/O) D31-D24 CAS (DRAM) / I/O port J [5]

89 WE0/DQMLL O D7-D0 selection signal/DQM (SDRAM)

90 WE1/DQMLU/WE O D7-D0 selection signal/DQM (SDRAM)

91 WE2/DQMUL/ O/(I/O) D23-D16 selection signal/DQM (SDRAM)/PCMCIA I/O port K [6]

ICIORD/PTK[6]

92 WE3/DQMUU/ O/(I/O) D31-D24 selection signal/DQM (SDRAM)/PCMCIA I/O write I/O port K [7]

ICIOWR/PTK[7]

93 RD/WR O Read/Write switch signal

88 RD O Read strobe

105 CKE/PTK[5] O/(I/O) CK enable (for SDRAM only) / I/O port K [5]

123 WAIT I Hardware wait request

11-8 IRL[3:0]/IRQ[3:0]/ I Hardware wait request

PTH[3:0]

12 IRQ4/PTH[4] I External interrupt request / I/O port H [4]

7 NMI I Non-maskable interrupt request

160 IRQOUT O Interrupt request output

182 WAKEUP/PTD[3] O/(I/O) Standby mode interrupt request output / I/O ports D [3]

159 TCLK/PTH[7] I/O TMU/RTC clock I/O / I/O port H [7]

191 DREQ0/PTD[4] I DMA request 0 / I/O port D [4]

114 DACK0/PTD[5] O/(I/O) DMA ACK 0 / I/O port D [5]

192 DREQ1/PTD[6] I DMA request 0 / I/O port D [6]

115 DACK1/PTD[7] O/(I/O) DMA ACK 1 / I/O port D [7]

189 DRAK0/PTD[1] O/(I/O) DMA ACK 1 / I/O port D [7]

190 DRAK1/PTD[0] O/(I/O) DMA ACK 0 / I/O port D [0]

171 RxD0/SCPT[0] I Receive data 0/SCI input port [0]

164 TxD0/SCPT[0] O Send data 0/SCI output port [0]

165 SCK0/SCPT[1] I/O Serial clock 0/SCI I/O port [1]

172 RxD1/SCPT[2] I Receive data 0/SCI input port [2]

166 TxD1/SCPT[2] O Send data 0/SCI output port [2]

167 SCK1/SCPT[1] I/O Serial clock 1/SCI I/O port [3]

174 RxD2/SCPT[4] I Receive data 0/SCI input port [4]

168 TxD2/SCPT[4] O Send data 2/SCI output port [4]

169 SCK2/SCPT[5] I/O Serial clock 2/SCI I/O port [5]

170 RTS2/SCPT[6] O/(I/O) Send request 2/SCI I/O port [6]

176

CTS2/IRQ5/SCPT[7]

I Send clear 2/enternal interrupt request/SCI input port [7]

104 CE2B/PTE[5] O/(I/O) PC card 0 chip enable 2 / I/O port E [5]

126 IOIS16/PTG[7] I Write protect/input port G [7]

103 CE2A/PTE[[4] O/(I/O) PC card 1 chip enable 2 / I/O port E [4]

146, 149 CAP[1:2] –– PLL external capacitor pin [1:2]

156 EXTAL I External clock/crystal oscillator input

155 XTAL O Crystal oscillator output

162 CKIO I/O System clock I/O

5 EXTAL2 I RTC crystal oscillator input

4 XTAL O RTC crystal oscillator output

ËRH-iX3270CEZZ (ASSY:IC10001)

32-bit RISC Micro Processor

» Pin mapping

Loading...

Loading...