Si5338-RM

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com 25

Rev. 1.4 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • 2021

9.7. Output Clock Invert

An output configured as CMOS/SSTL/HSTL will have both of its outputs (A/B) in phase by default, but, by using the

invert bits, one or both outputs can be inverted. The invert feature allows a CMOS/SSTL/HSTL output to have

complimentary outputs. Differential outputs (LVPECL, LVDS, HCSL, CML) are always complimentary even when

inverted.

Upon power up or a soft_reset, the Si5338 synchronizes the output clocks. With normal output polarity (no output

clock inversion), the Si5338 synchronizes the output clocks to the falling, not rising, edge. Synchronization at the

rising edge can be done by inverting all the clocks that are to be synchronized.

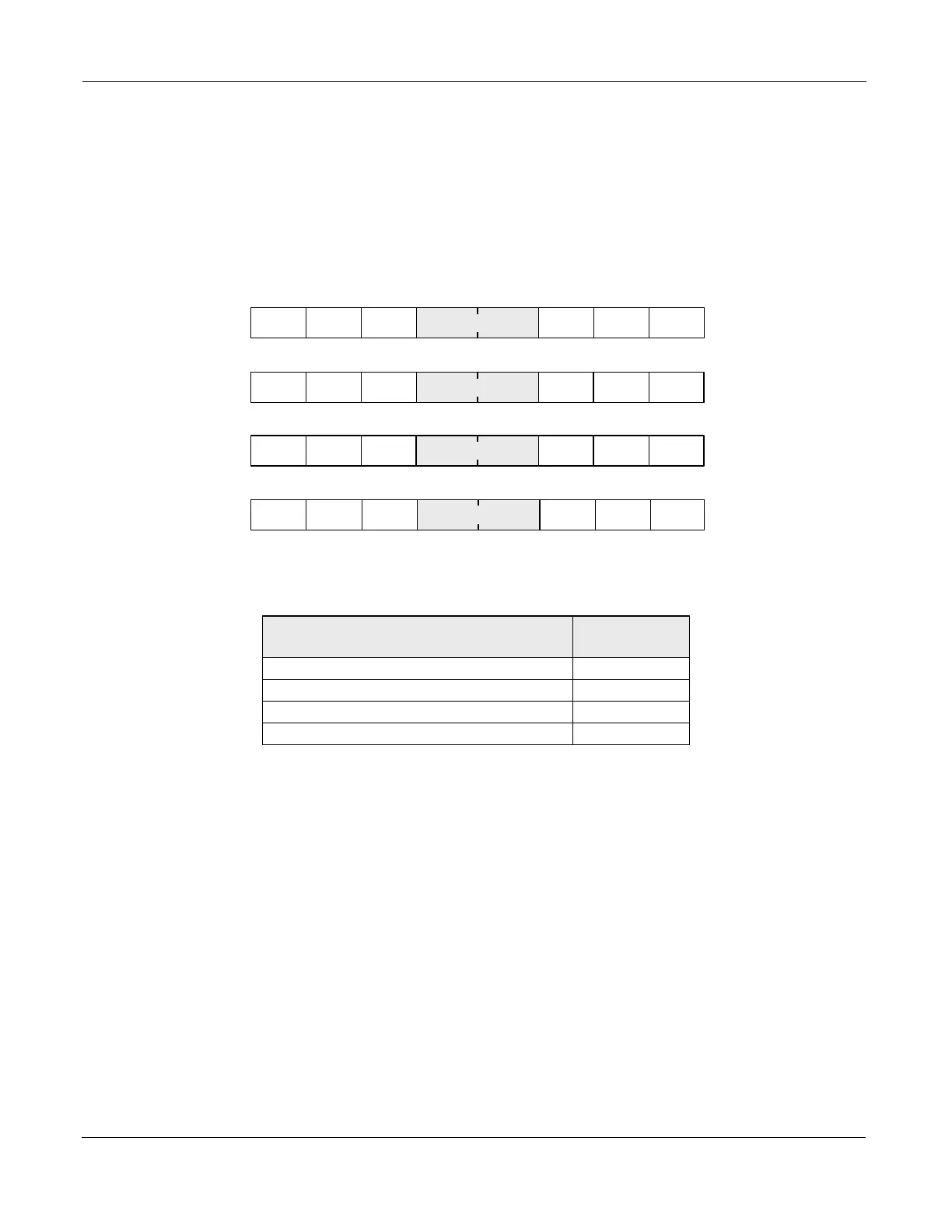

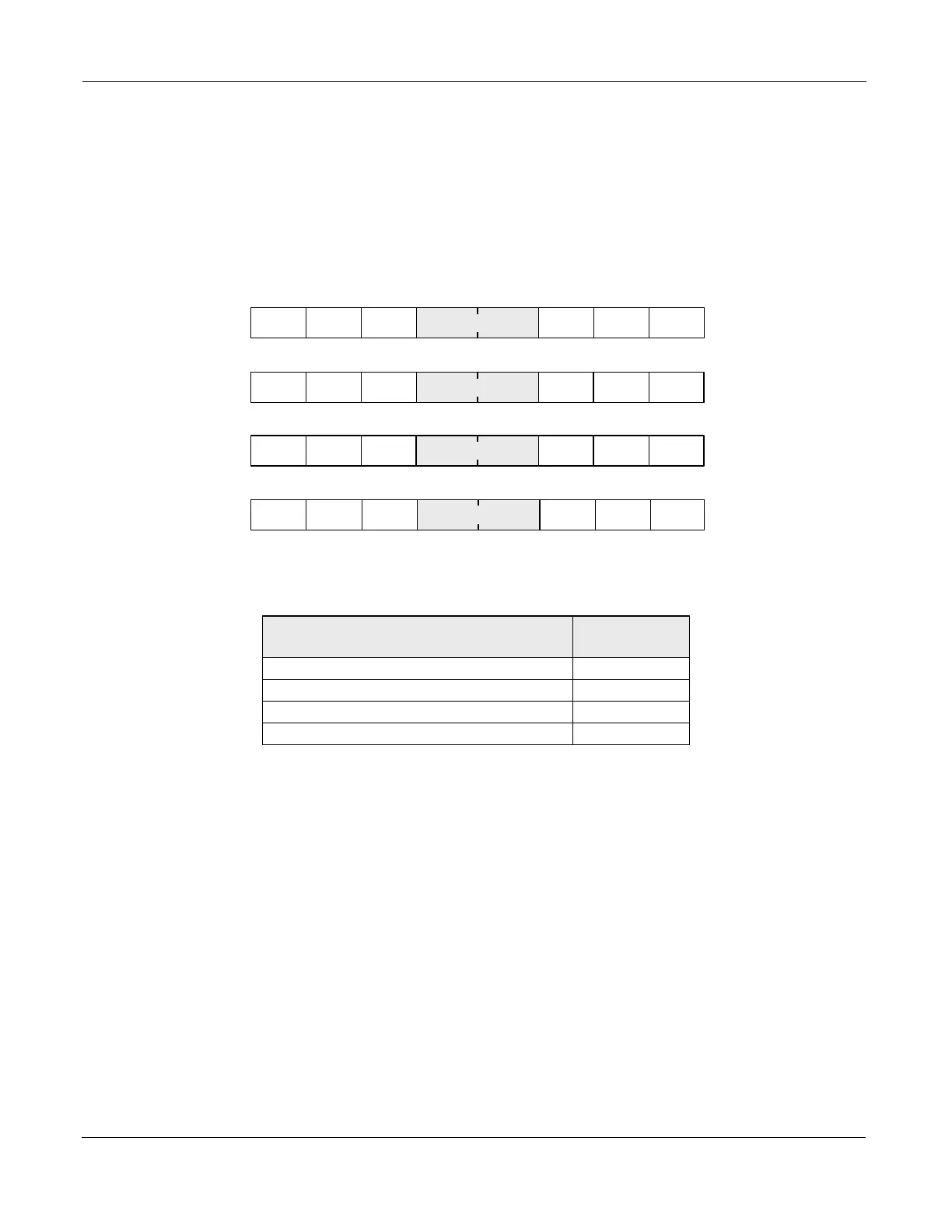

Figure 16. Setting Output Clock Inversion

DRVx_INV[1:0]

x=0,1,2,3

01

10

11

Invert A side (CMOS/SSTL/HSTL only)

Inversion

Invert B side (CMOS/SSTL/HSTL only)

Invert both A and B sides

00

No inversion

36[7:0]

01234567

37[7:0]

38[7:0]

39[7:0]

DRV0_INV[1:0]

01234567

DRV1_INV[1:0]

01234567

DRV2_INV[1:0]

01234567

DRV3_INV[1:0]

Loading...

Loading...