Si5338-RM

26 Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

Rev. 1.4 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • 2021

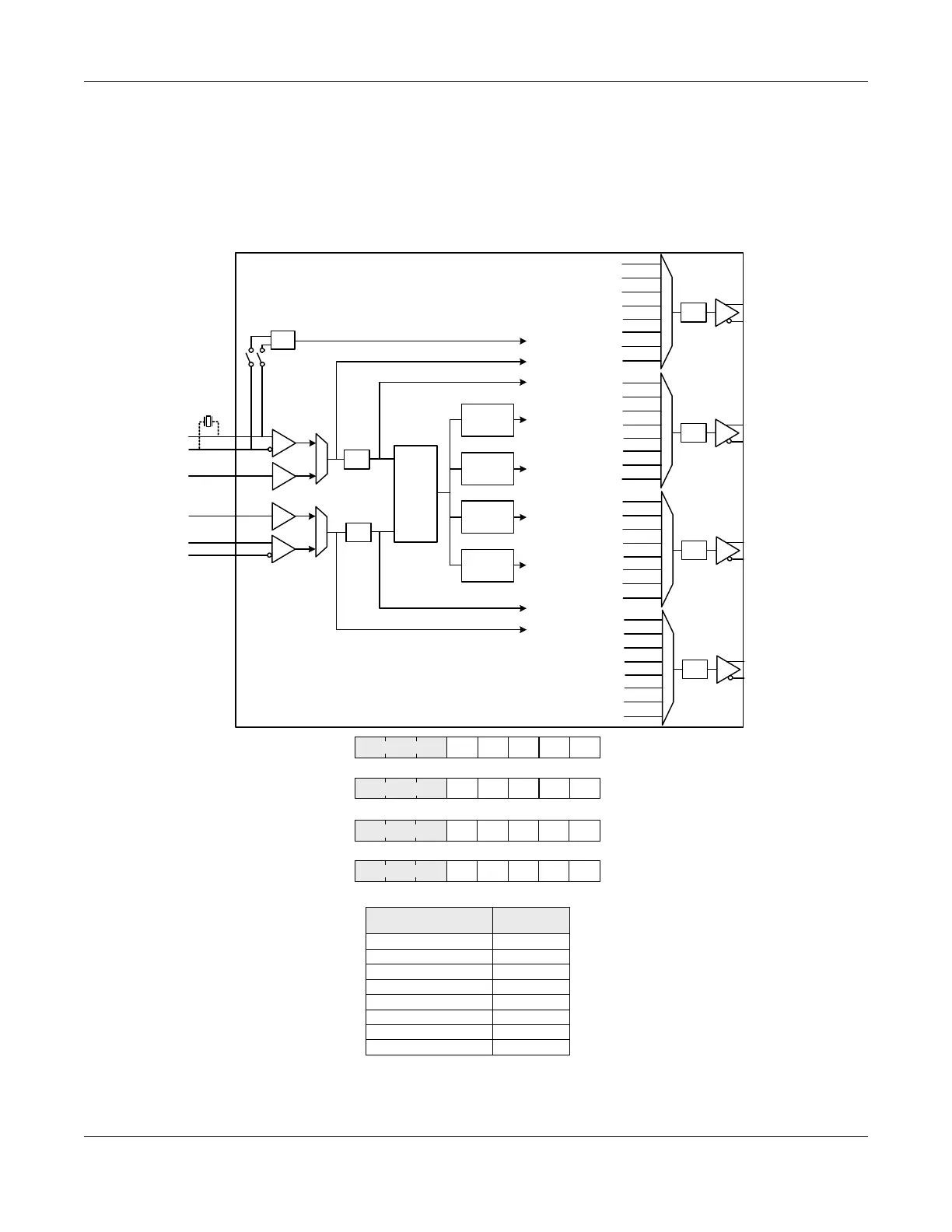

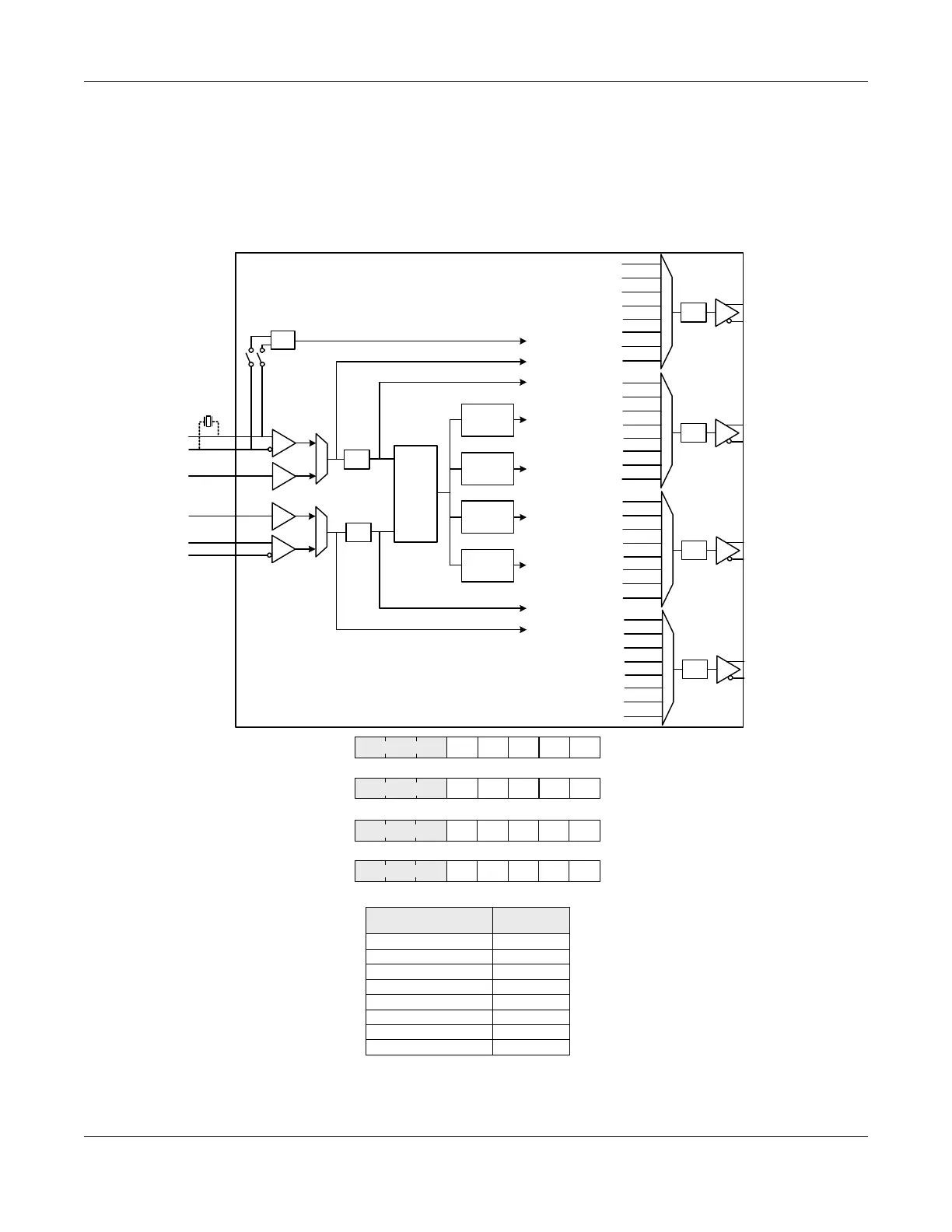

9.8. Output Clock Select

The source of each of the clock outputs (CLKx) can be selected as shown in Figure 17. This level of flexibility

allows the drivers to output any of the synthesized clocks (MSx) or bypass the PLL and output any of the input

clocks directly. This allows the Si5338 to operate as a PLL, a clock buffer, or a combination of both. Any active

output buffer that does not receive its clock from the PLL should have its disable state (“9.6. Output Drive State

When Disabled”) set to “always on”. The register settings are shown in Figure 17.

Figure 17. Selecting the Output Clock Source

32[7:0]

01234567

33[7:0]

01234567

34[7:0]

01234567

31[7:0]

R0DIV_IN[2:0]

01234567

R2DIV_IN[2:0]

R1DIV_IN[2:0]

R3DIV_IN[2:0]

RxDIV_IN[2:0]

x=0,1,2,3

001

010

011

100

101

refclk (p1div_in)

Selected Source

divfbclk (p2div_out)

divrefclk (p1div_out)

xoclk

M0

110

Mn

111

No clock

000

fbclk (p2div_in)

÷P1

IN3

IN2

IN1

Osc

Optional

XTAL

÷P2

IN4

IN6

IN5

refclk

fbclk

divfbclk

Si5338

xoclk

divrefclk

PLL

M0

M1

M2

M3

xoclk

refclk

divrefclk

fbclk

divfbclk

M0

M0

÷R0

xoclk

refclk

divrefclk

fbclk

divfbclk

M0

M1

÷R1

xoclk

refclk

divrefclk

fbclk

divfbclk

M0

M2

÷R2

xoclk

refclk

divrefclk

fbclk

divfbclk

M0

M3

÷R3

MultiSynth

÷MS0

MultiSynth

÷MS1

MultiSynth

÷MS2

MultiSynth

÷MS3

CLK0A,B

CLK1A,B

CLK2A,B

CLK3A,B

noclk

noclk

noclk

noclk

Loading...

Loading...