– 9 –

SECTION 4

DIAGRAMS

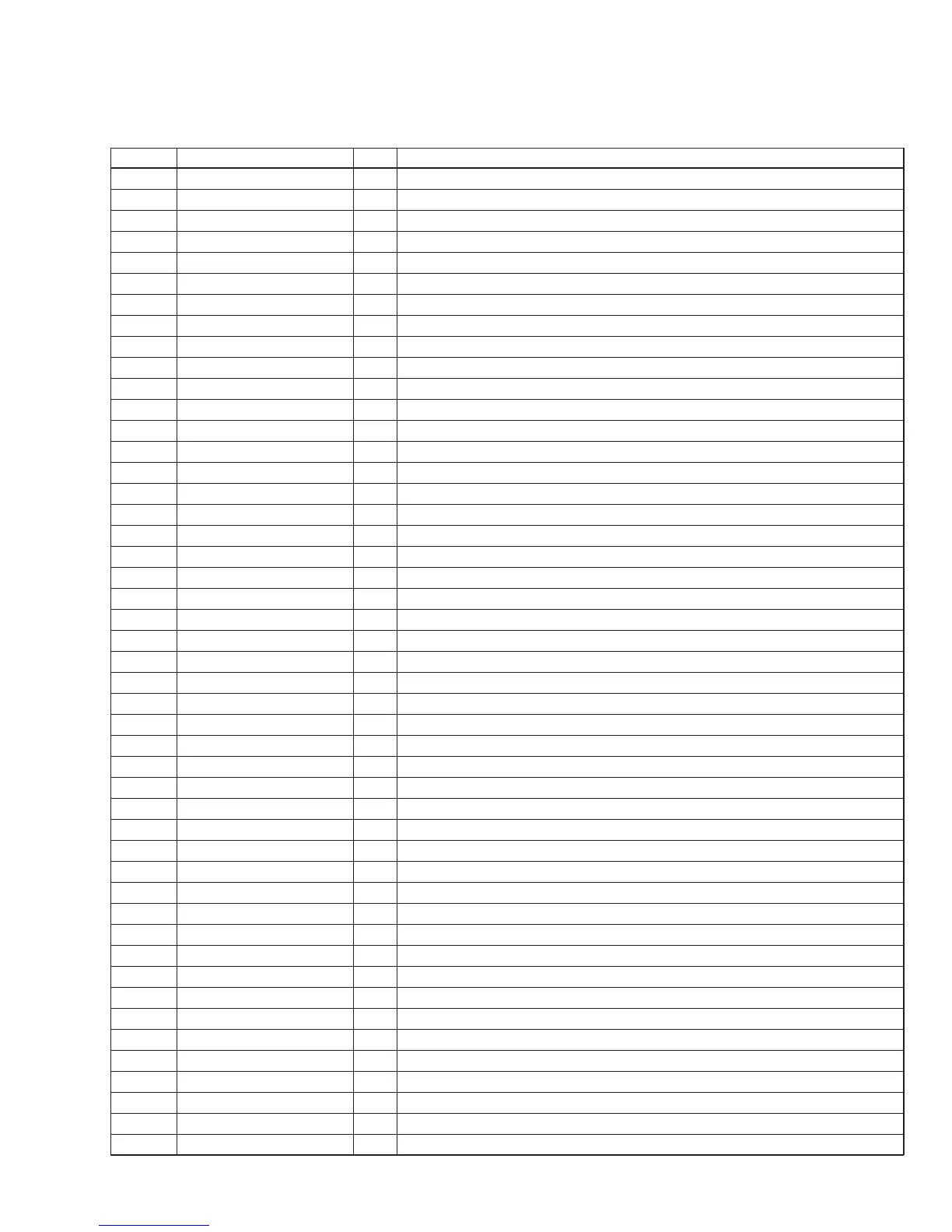

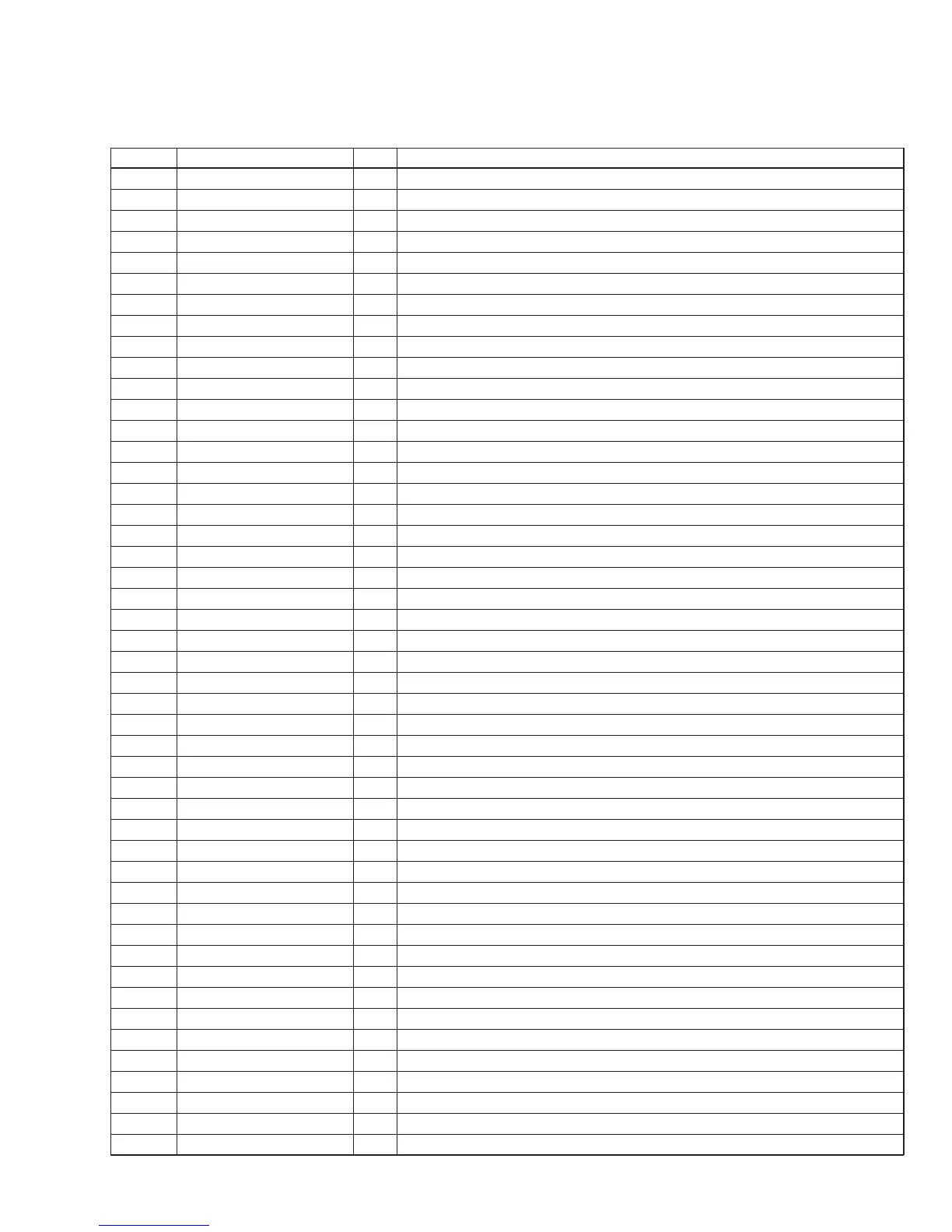

4-1. IC PIN FUNCTIONS

• IC101 CXD2545Q (DIGITAL SERVO & DIGITAL SIGNAL PROCESSOR)

Pin No. Pin Name I/O Function

1 SRON O Sled drive output (Not used.)

2 SRDR O Sled drive output

3 SFON O Sled drive output (Not used.)

4 TFDR O Tracking drive output

5 TRON O Tracking drive output (Not used.)

6 TRDR O Tracking drive output

7 TFON O Tracking drive output (Not used.)

8 FFDR O Focus drive output

9 FRON O Focus drive output (Not used.)

10 FRDR O Focus drive output

11 FFON O Focus drive output (Not used.)

12 VCOO O VCO output for analog EFM PLL. (Not used.)

13 VCOI I VCO input for analog EFM PLL. (Ground)

14 TEST I TEST pin connected normally to Ground.

15 DVSS — Digital Ground

16 TES2 I TEST pin connected normally to Ground.

17 TES3 I TEST pin connected normally to Ground.

18 PDO O Charge-pump output for analog EFM PLL. (Not used.)

19 VPCO O Charge-pump output for variable pitch PLL. (Not used.)

20 VCKI I Clock input from variable pitch external VCO. (Ground)

21 AVD2 — Analog power supply

22 IGEN I Power supply pin for operational amplifiers.

23 AVS2 — Analog Ground

24 ADIO I (Not used.)

25 RFC O (Not used.)

26 RFDC I RF signal input

27 TE I Tracking error signal input

28 SE I Sled error signal input

29 FE I Focus error signal input

30 VC I Center voltage input pin

31 FILO O Filter output for master PLL.

32 FILI I Filter input for master PLL.

33 PCO O Charge-pump output for master PLL.

34 CLTV I Control voltage input for master VCO.

35 AVS1 — Analog Ground

36 RFAC I EFM signal input

37 BIAS I Asymmetry circuit constant current input

38 ASYI I Asymmetry comparate voltage input

39 ASYO O EFM full swing output

40 AVD1 — Analog power supply

41 DVDD — Digital power supply

42 ASYE I Asymmetry circuit ON/OFF

43 PSSL I Audio data output mode selection input. (Ground)

44 WDCK O 48-bit slot D/A interface. Word clock

45 LRCK O 48-bit slot D/A interface. LR clock

46 DATA O DA 16 output when PSSL=1. 48-bit slot serial data when PSSL=0.

47 BCLK O DA 15 output when PSSL=1. 48-bit slot data when PSSL=0.

Loading...

Loading...