– 75 –

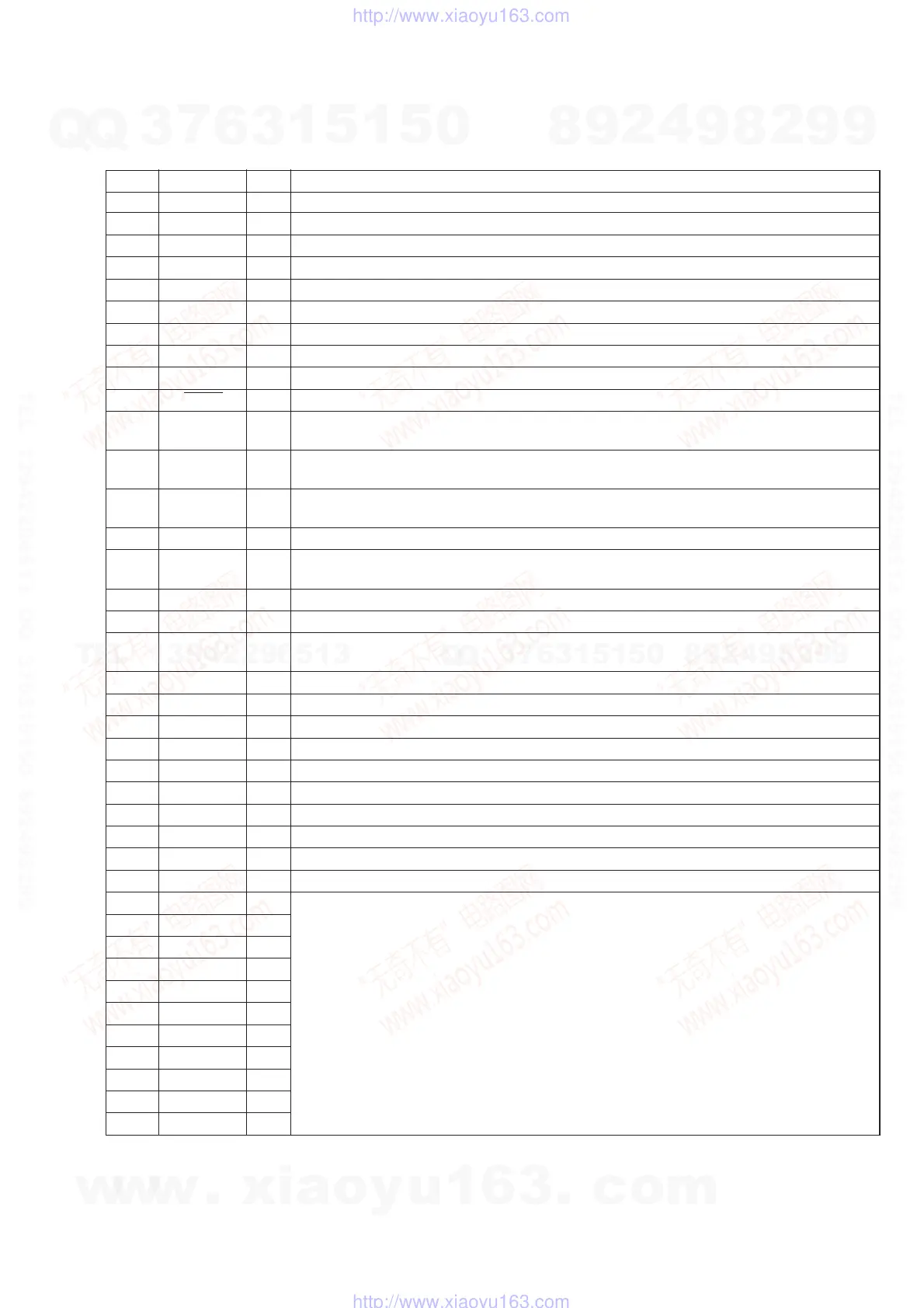

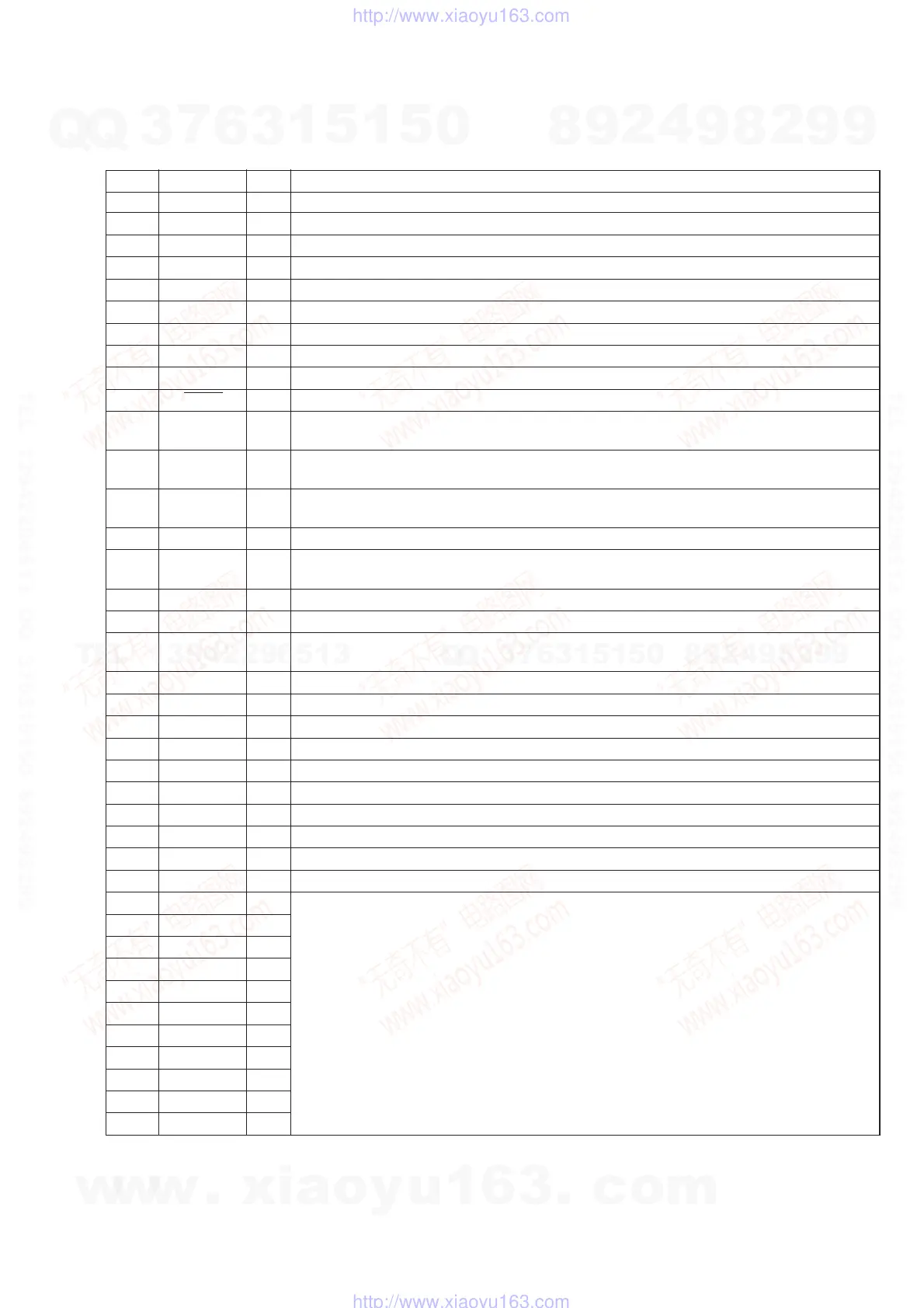

• BD (MD) BOARD IC121 CXD2652AR

• (DIGITAL SIGNAL PROCESSOR, DIGITAL SERVO PROCESSOR, EFM/ACIRC ENCODER/DECODER, SHOCK

• PROOF MEMORY CONTROLLER, ATRAC ENCODER/DECODER, 2M BIT D-RAM)

Pin No. Pin Name I/O Function

1 MNT0 (FOK) O Focus OK signal output to the MD system controller (IC316) “H” is output when focus is on

2

MNT1 (SHCK)

O Track jump detection signal output to the MD system controller (IC316)

3

MNT2 (XBUSY)

O Monitor 2 signal output to the MD system controller (IC316)

4

MNT3 (SLOC)

O Monitor 3 signal output to the MD system controller (IC316)

5 SWDT I Writing data signal input from the MD system controller (IC316)

6 SCLK I Serial clock signal input from the MD system controller (IC316)

7 XLAT I Serial latch signal input from the MD system controller (IC316)

8 SRDT O (3) Reading data signal output to the MD system controller (IC316)

9 SENS O (3) Internal status (SENSE) output to the MD system controller (IC316)

10 XRST I Reset signal input from the MD system controller (IC316) “L”: reset

11 SQSY O

Subcode Q sync (SCOR) output to the MD system controller (IC316)

“L” is output every 13.3 msec Almost all, “H” is output

12 DQSY O

Digital In U-bit CD format subcode Q sync (SCOR) output to the MD system controller (IC316)

“L” is output every 13.3 msec Almost all, “H” is output

13 RECP I

Laser power selection signal input from the MD system controller (IC316)

“H”: recording mode, “L”: playback mode

14 XINT O Interrupt status output to the MD system controller (IC316)

15 TX I

Recording data output enable signal input from the MD system controller (IC316)

Writing data transmission timing input (Also serves as the magnetic head on/off output)

16 OSCI I System clock signal (512Fs=22.5792 MHz) input terminal

17 OSCO O System clock signal (512Fs=22.5792 MHz) output terminal

18 XTSL I

Input terminal for the system clock frequency setting

“L”: 45.1584 MHz, “H”: 22.5792 MHz (fixed at “H” in this set)

19 RVDD — Power supply terminal (+3.3V) (digital system)

20 RVSS — Ground terminal (digital system)

21 DIN I Digital audio signal input terminal when recording mode (for optical in)

22 DOUT O Digital audio signal output terminal when playback mode (for optical out) Not used

23 ADDT I Recording data input from the A/D, D/A converter (IC201)

24 DADT O Playback data output to the A/D, D/A converter (IC201)

25 LRCK O L/R sampling clock signal (44.1 kHz) output to the A/D, D/A converter (IC201)

26 XBCK O Bit clock signal (2.8224 MHz) output to the A/D, D/A converter (IC201)

27 FS256 O Clock signal (11.2896 MHz) output to the A/D, D/A converter (IC201)

28 DVDD — Power supply terminal (+3.3V) (digital system)

29 A03 O

30 A02 O

31 A01 O

32 A00 O

33 A10 O

34 A04 O Address signal output to the external D-RAM (IC124)

35 A05 O

36 A06 O

37 A07 O

38 A08 O

39 A11 O

* I (A) for analog input, O (3) for 3-state output, and O (A) for analog output in the column I/O.

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...