56

HCD-VM330AV

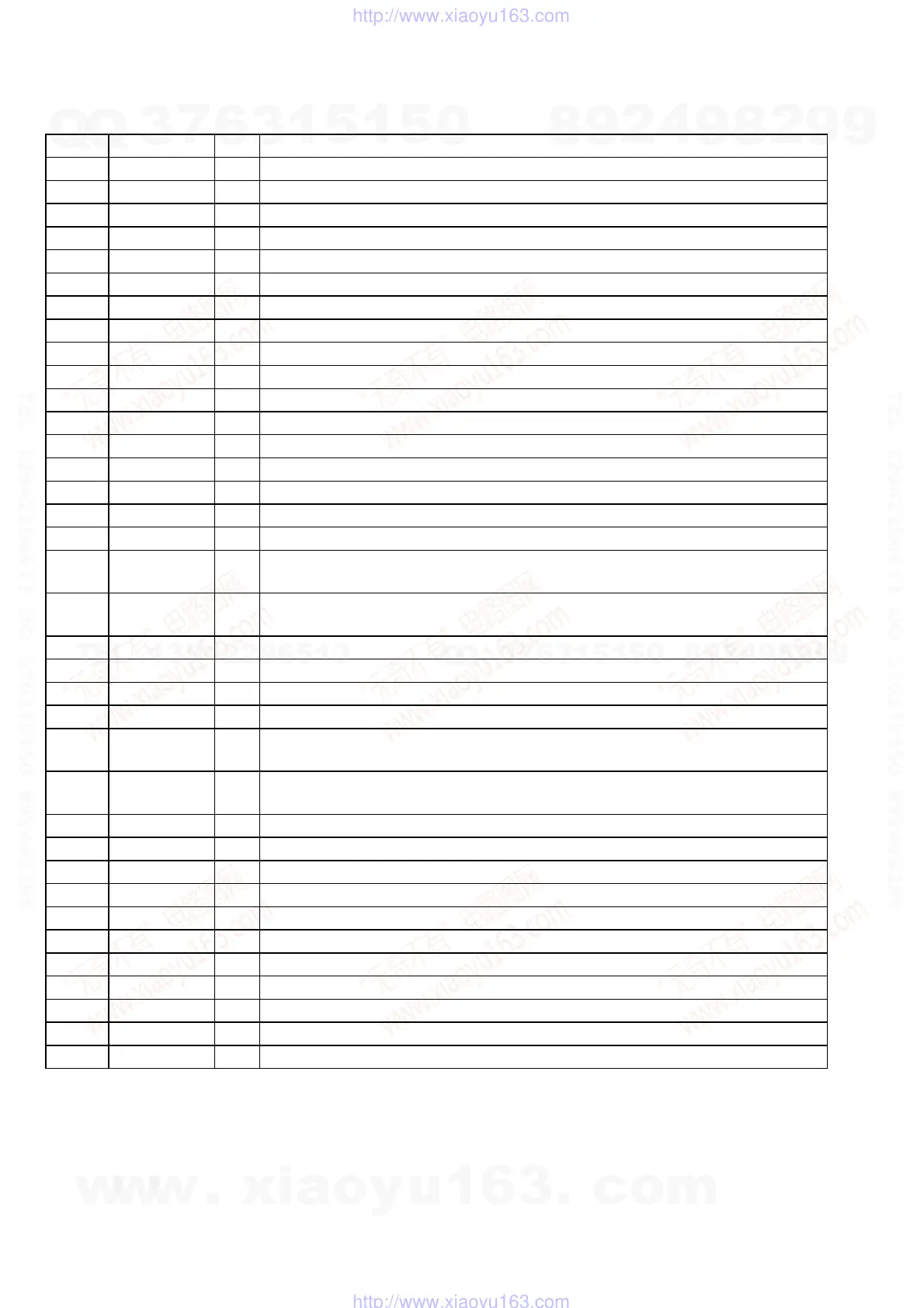

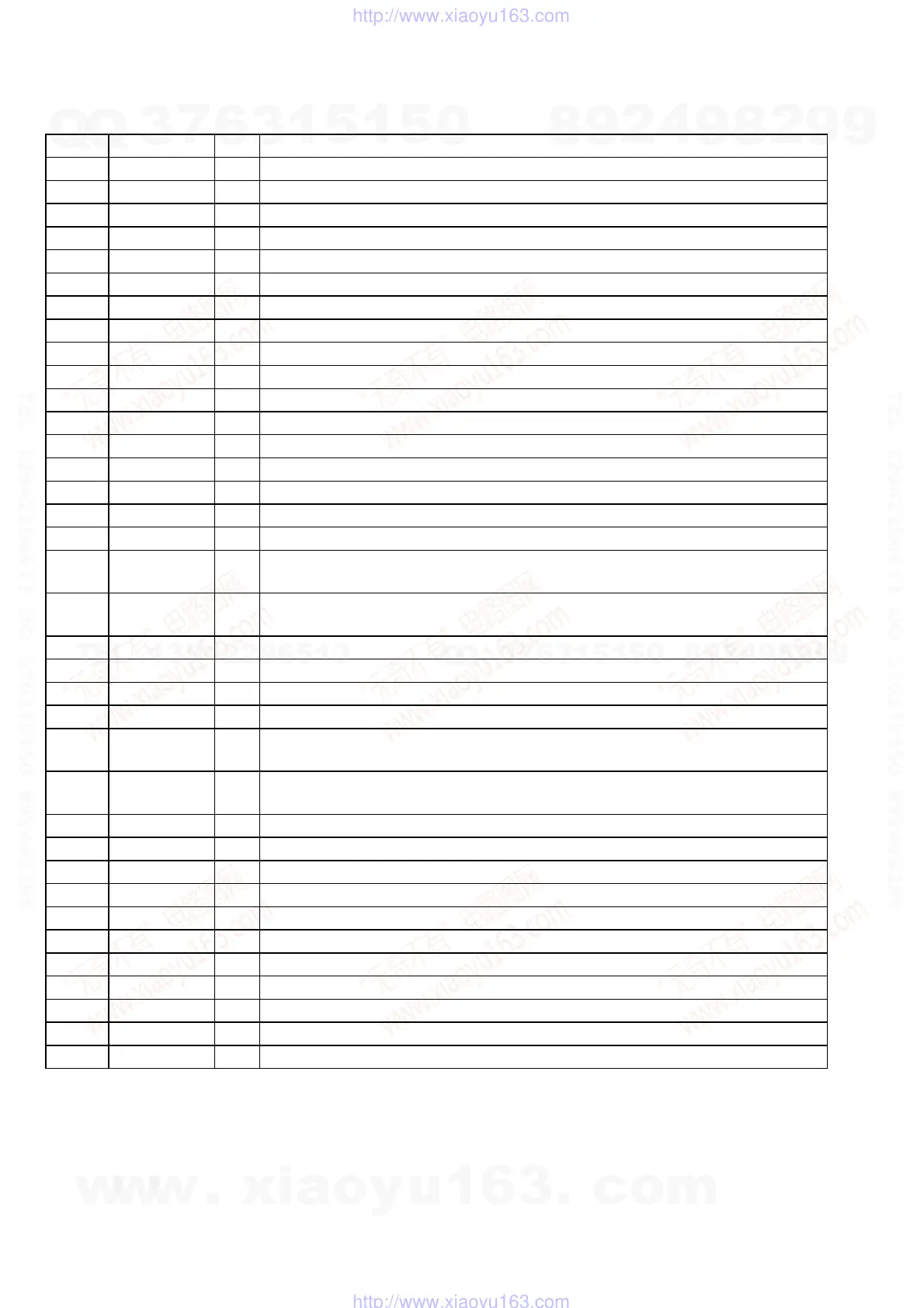

Pin No. Pin Name I/O Description

45 AVSS0 —

Ground terminal (analog system)

46 IGEN I

Stabilized current input for operational amplifiers

47 AVDD0 —

Power supply terminal (+3.3V) (analog system)

48 ASYO O

EFM full-swing output terminal

49 ASYI I

Asymmetry comparator voltage input terminal

50 RFAC I

EFM signal input from the CXA2581N (IC103)

51 AVSS1 —

Ground terminal (analog system)

52 CLTV I

Internal VCO control voltage input

53 FILO O

Filter output for master PLL

54 FILI I

Filter input for master PLL

55 PCO O

Charge pump output for master PLL

56 AVDD1 —

Power supply terminal (+3.3V) (analog system)

57 BIAS I

Asymmetry circuit constant current input terminal

58 VCTL I

VCO control voltage input terminal for the wideband EFM PLL Not used (fixed at “H”)

59 V16M O

VCO oscillation output terminal for the wideband EFM PLL Not used (open)

60 VPCO O

Charge pump output terminal for the wideband EFM PLL Not used (open)

61 DVDD2 —

Power supply terminal (+3.3V) (digital system)

62 ASYE I

Asymmetry circuit on/off control signal input terminal “L”: off, “H”: on

Not used (fixed at “H”)

63 MD2 I

Digital out on/off control signal input from terminal

“L”: digital out off, “H”: digital out on Not used (fixed at “H”)

64 DOUT O

Digital audio signal output to the OPTICAL OUT (IC361)

65 LRCK O

L/R sampling clock signal (44.1 kHz) output to the CL680T (IC505)

66 PCMD O

Serial data output to the CL680T (IC505)

67 BCLK O

Bit clock signal (2.8224 MHz) output to the CL680T (IC505)

68 EMPH O

“L” is output when playback disc is emphasis off

“H” is output when playback disc is emphasis on Not used (open)

69 XTSL I

System clock frequency setting signal input from the video CD controller (IC502)

“L”: 16.9344 MHz, “H”: 33.8688MHz

70 DVSS2 —

Ground terminal (digital system)

71 XTAI I

System clock (33.8688 MHz) input from the D/A converter (IC509)

72 XTAO O

System clock output terminal (33.8688 MHz) Not used (open)

73 SOUT O

Serial data output terminal Not used (open)

74 SOCK O

Serial data reading clock signal output terminal Not used (open)

75 XOLT O

Serial data latch pulse signal output terminal Not used (open)

76 SQSO O

Subcode Q data output to the video CD controller (IC502)

77 SQCK I

Subcode Q data reading clock signal input from the video CD controller (IC502)

78 SCSY I

Input terminal for resynchronism of guard subcode sync (S0+S1) Not used (fixed at “L”)

79 SBSO O

Subcode serial data output terminal Not used (open)

80 EXCK I

Subcode serial data reading clock signal input terminal Not used (open)

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...