59

HCD-VM330AV

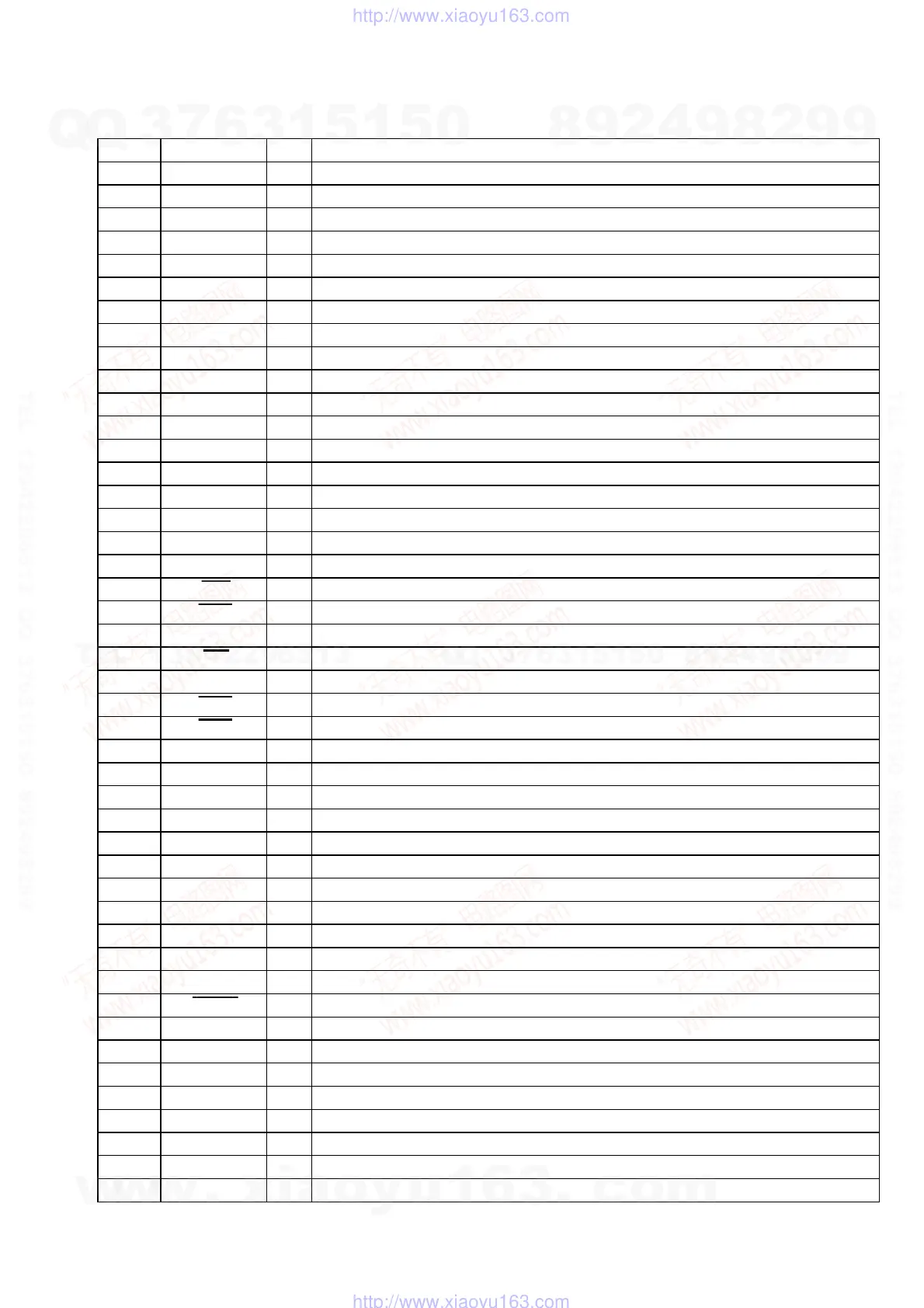

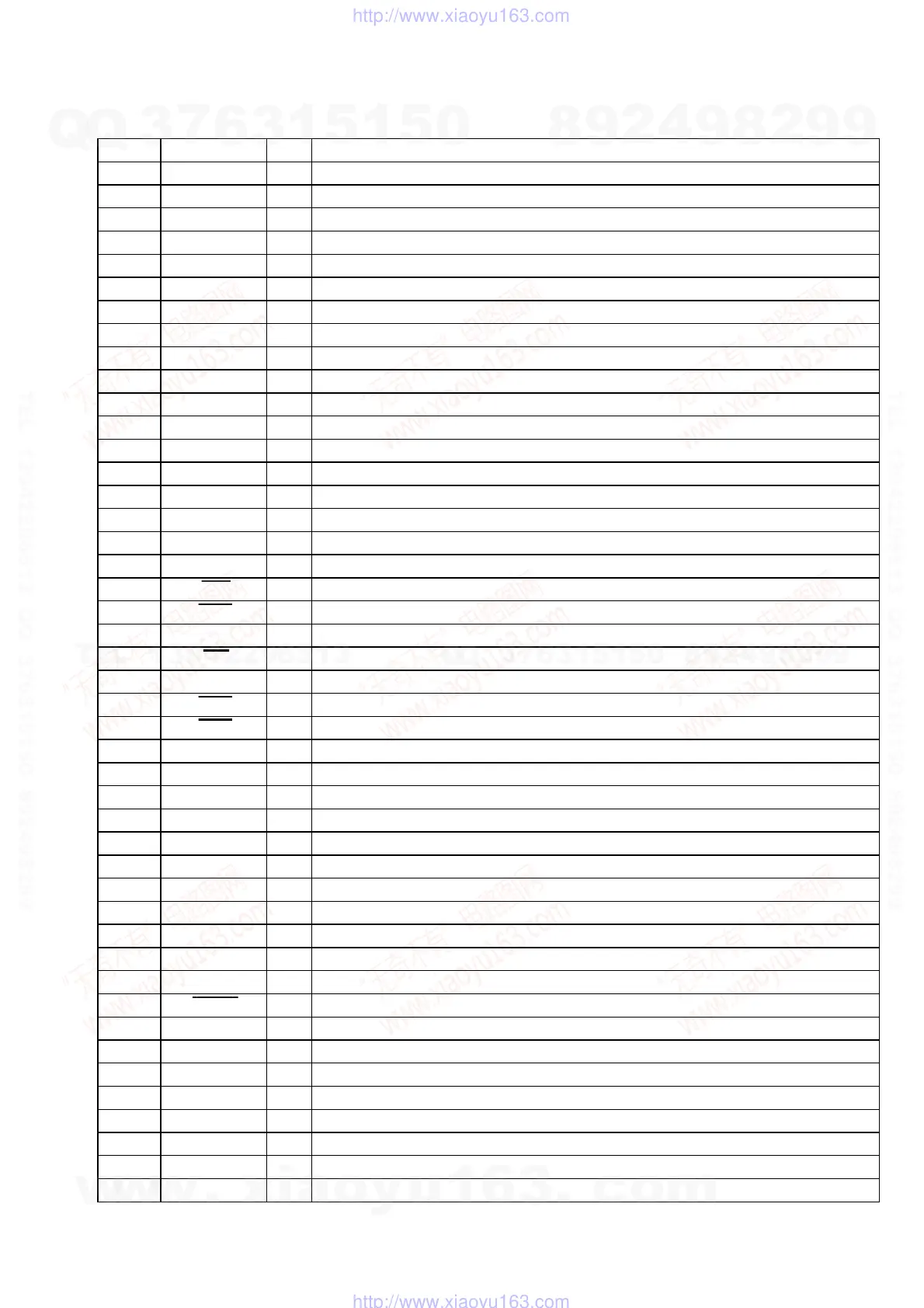

• VIDEO BOARD IC505 CL680T-D1 (MPEG VIDEO/AUDIO DECODER, VIDEO SIGNAL PROCESSOR)

Pin No. Pin Name I/O Description

1NCO

Not used (open)

2VSS—

Ground terminal

3 CD-BCK I

CD decode bit clock signal (2.8224 MHz) input from the CXD3068Q (IC101)

4 CD-DATA I

CD decode data input from the CXD3068Q (IC101)

5 CD-LRCK I

CD decode L/R sampling clock signal (44.1 kHz) input from the CXD3068Q (IC101)

6 CD-C2PO I

CD decode C2 error data input from the CXD3068Q (IC101)

7 to 9 NC O

Not used (open)

10 to 15 MD0 to MD5 I/O

Two-way data bus with the D-RAM (IC507) Data input from the program ROM (IC510)

16 VSS —

Ground terminal

17 MD6 I/O

Two-way data bus with the D-RAM (IC507) Data input from the program ROM (IC510)

18 VDD3 —

Power supply terminal (+3.3V)

19 MD7 I/O

Two-way data bus with the D-RAM (IC507) Data input from the program ROM (IC510)

20 VSS —

Ground terminal

21 MD8 I/O

Two-way data bus with the D-RAM (IC507) Data output to the program ROM (IC510)

22 VDD3 —

Power supply terminal (+3.3V)

23 to 28 MD9 to MD14 I/O

Two-way data bus with the D-RAM (IC507) Data output to the program ROM (IC510)

29 MD15 I/O

Two-way data bus with the D-RAM (IC507)

30 to 36 NC O

Not used (open)

37 MCE O

Chip enable signal output to the program ROM (IC510)

38 MWE O

Write enable signal output to the D-RAM (IC507)

39 VSS —

Ground terminal

40 CAS O

Column address strobe signal output to the D-RAM (IC507)

41 VDD3 —

Power supply terminal (+3.3V)

42 RAS0 O

Row address strobe signal output to the D-RAM (IC507)

43 RAS1 O

Row address strobe signal output terminal Not used (open)

44, 45 MA10, MA9 O

Address signal output to the program ROM (IC510)

46 MA8 O

Address signal output to the D-RAM (IC507) and program ROM (IC510)

47 VSS —

Ground terminal

48 MA7 O

Address signal output to the D-RAM (IC507) and program ROM (IC510)

49 VDD3 —

Power supply terminal (+3.3V)

50 to 52 MA6 to MA4 O

Address signal output to the D-RAM (IC507) and program ROM (IC510)

53 VSS —

Ground terminal

54 MA3 O

Address signal output to the D-RAM (IC507) and program ROM (IC510)

55 VDD3 —

Power supply terminal (+3.3V)

56 to 58 MA2 to MA0 O

Address signal output to the D-RAM (IC507) and program ROM (IC510)

59 PGIO7 I/O

Not used (open)

60 RESET I

Reset signal input from the video CD controller (IC502) “L”: reset

61 VDDMAX-IN I

Fix the maximum input voltage each input terminal and in/out terminal

62 to 64 NC O

Not used (open)

65 AGND-DAC —

Ground terminal (for D/A converter)

66 AVDD-DAC —

Power supply terminal (+3.3V) (for D/A converter)

67 COMPOS OUT O

Composite video signal output terminal Not used (open)

68 AGND-DAC —

Ground terminal (for D/A converter)

69 Y-OUT O

Luminance video signal output to the Y amplifier (IC303)

70 AVDD-DAC —

Power supply terminal (+3.3V) (for D/A converter)

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...