Hardware layout and configuration UM1974

46/82 DocID028599 Rev 7

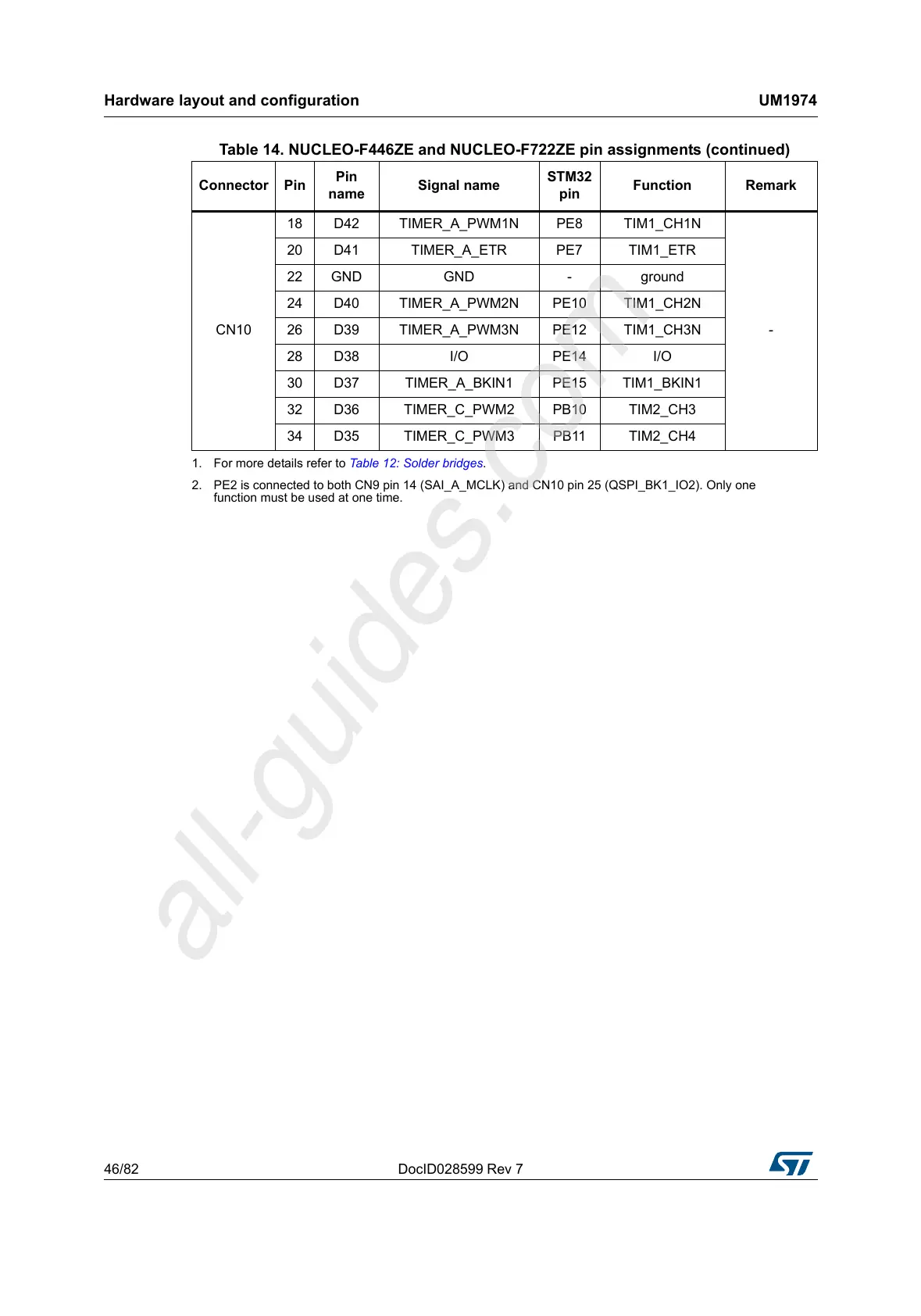

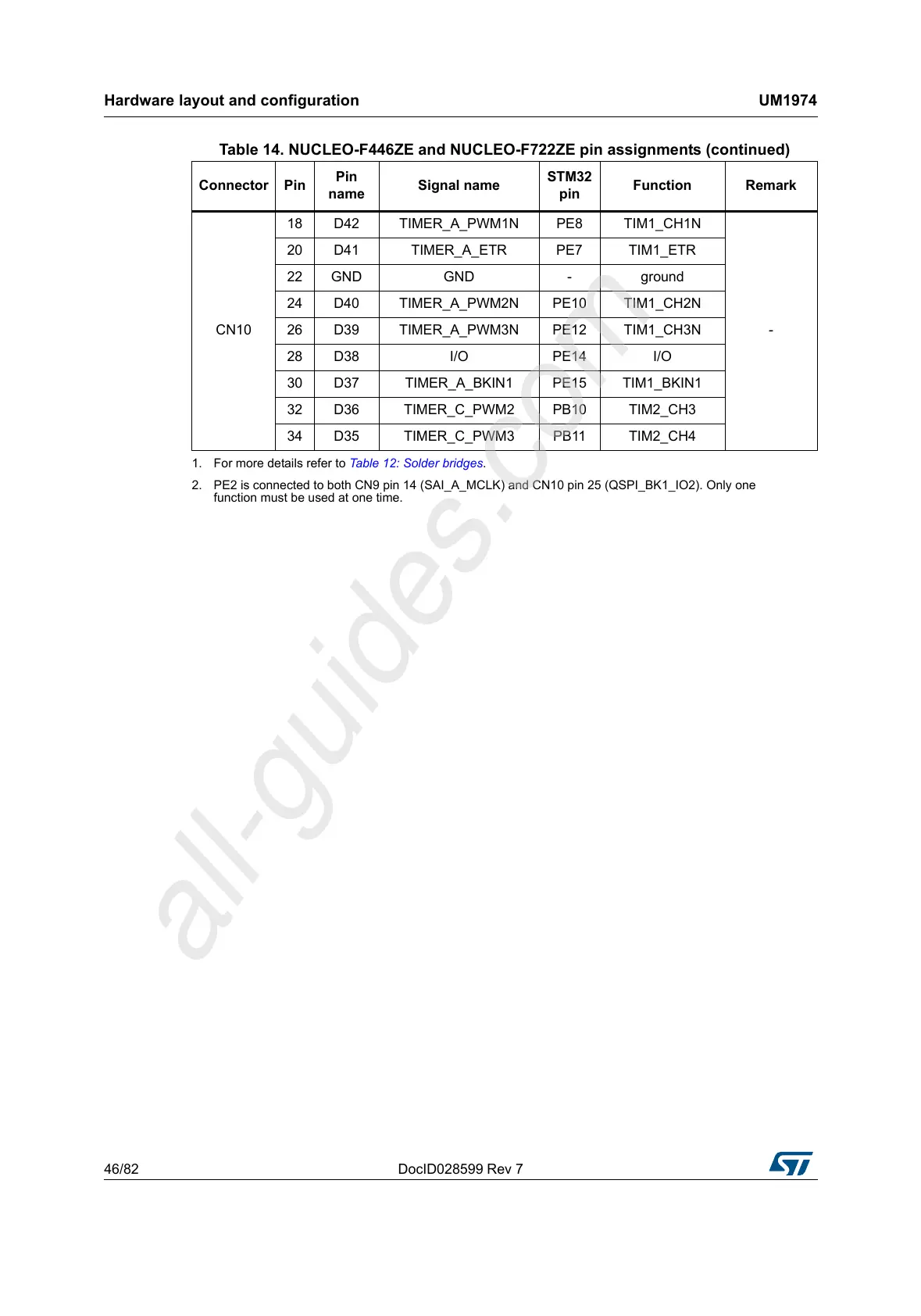

CN10

18 D42 TIMER_A_PWM1N PE8 TIM1_CH1N

-

20 D41 TIMER_A_ETR PE7 TIM1_ETR

22 GND GND - ground

24 D40 TIMER_A_PWM2N PE10 TIM1_CH2N

26 D39 TIMER_A_PWM3N PE12 TIM1_CH3N

28 D38 I/O PE14 I/O

30 D37 TIMER_A_BKIN1 PE15 TIM1_BKIN1

32 D36 TIMER_C_PWM2 PB10 TIM2_CH3

34 D35 TIMER_C_PWM3 PB11 TIM2_CH4

1. For more details refer to Table 12: Solder bridges.

2. PE2 is connected to both CN9 pin 14 (SAI_A_MCLK) and CN10 pin 25 (QSPI_BK1_IO2). Only one

function must be used at one time.

Table 14. NUCLEO-F446ZE and NUCLEO-F722ZE pin assignments (continued)

Connector Pin

Pin

name

Signal name

STM32

pin

Function Remark

Loading...

Loading...