DocID030511 Rev 1 9/69

UM2198 Hardware layout and configuration

68

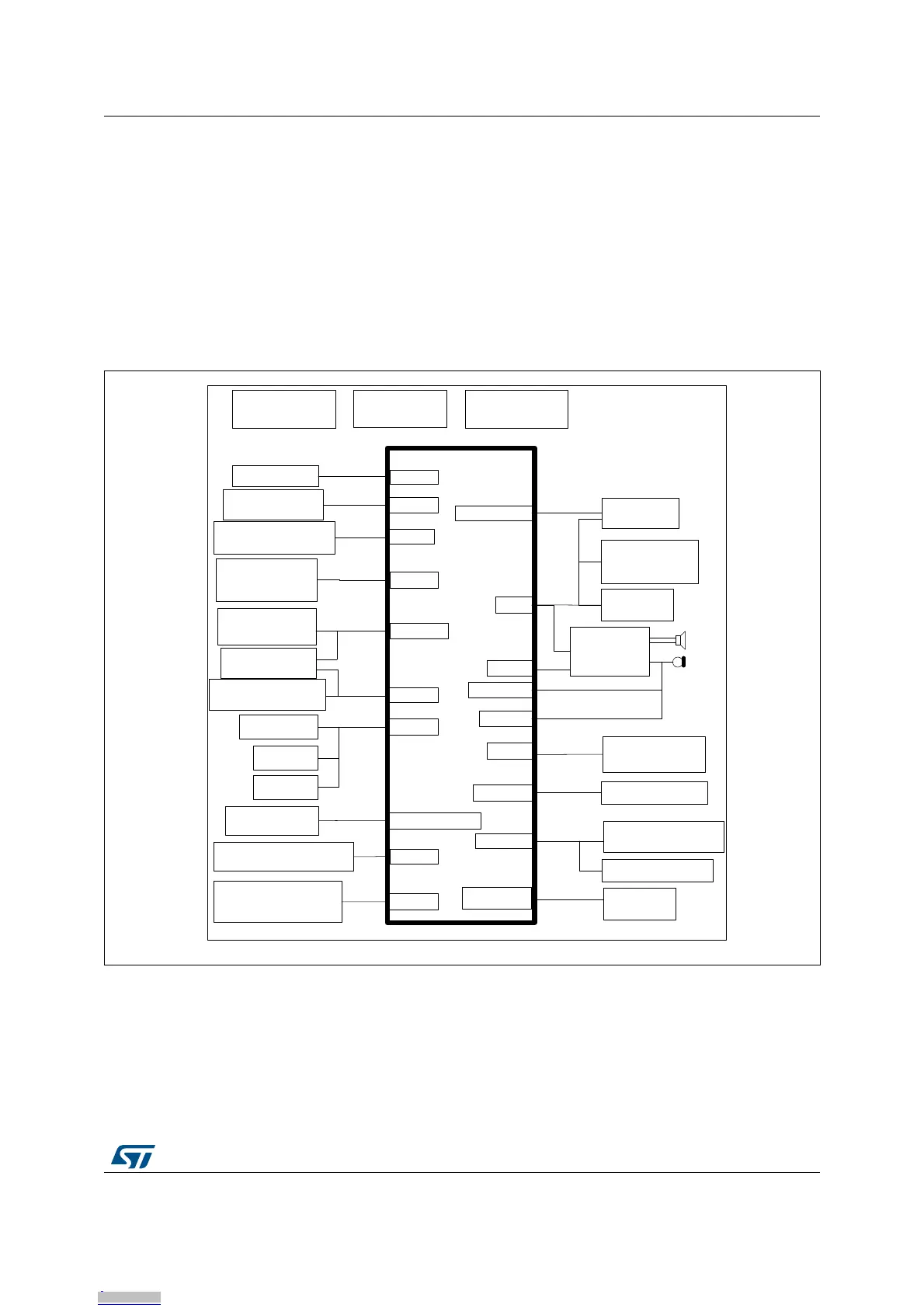

8 Hardware layout and configuration

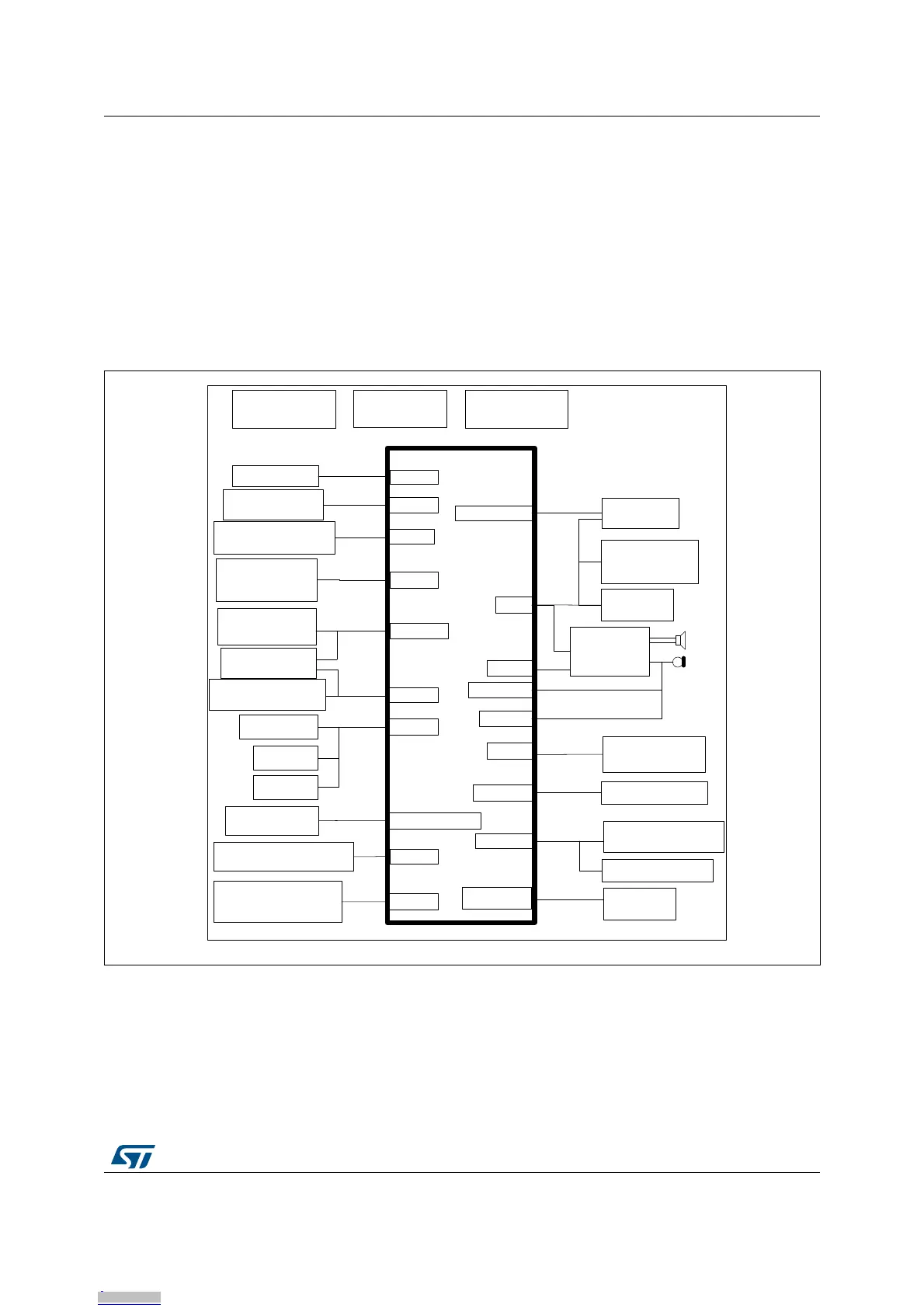

The STM32H743I-EVAL Evaluation board is designed around the STM32H743XIH6

(240+25-pin TFBGA package) microcontroller. The hardware block diagram (see Figure 2)

illustrates the connection between STM32H743XIH6 and the peripherals (SDRAM, SRAM,

NOR Flash,

Twin Quad-SPI Flash, color LCD, USB OTG connectors, USART, Ethernet,

Audio, FD-CAN, microSD 3.0 card and embedded ST-LINK). Figure 3 helps users to locate

these features on the Evaluation board. The mechanical dimensions of the board are

showed in Figure 4.

Figure 2. Hardware block diagram

06Y9

670+;,+

9EDWWHU\

$XGLR'$&

DQG

$PSOLILHU

57&

3+<DQG(WKHUQHW

FRQQHFWRU

-7$*DQG7UDFH

FRQQHFWRU

'$3

56'%

FRQQHFWRU

.+]FU\VWDO

9%$7

67/,1.9

,&

86%FRQQHFWRU

6:DQG7UDFH

FRQQHFWRU

73,8

9*$

/&'

50,,

6$,

,&

FRQQHFWRU

/&'5*%

0);

-R\VWLFN/('

PLFUR6'FDUG

&$1FRQQHFWRU

)'&$1

.H\:DNHXSDQG

7DPSHUEXWWRQV

*3,2

3RWHQWLRPHWHU

$'&

6'00&

+63+<DQG86%

FRQQHFWRU

27*

125)ODVK

65$0

)0&

6'5$0

463,

*E\WH7ZLQ

463,)ODVK

27*)6

86%

FRQQHFWRU

8$57

')6'0

3'0

93RZHU

6XSSO\

93RZHU

6XSSO\

96'

3RZHU6XSSO\

Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.

Loading...

Loading...