New DMA2D features to support Intel 8080 displays AN4943

16/22 DocID029937 Rev 2

5.2 DMA2D reordering features

The DMA2D output FIFO bytes can be reordered to support the display frame buffer update

through a parallel interface (FSMC) directly from the DMA2D. The user can do combination

of reordering operations to get the right byte endianness aligned with the display color

coding.

5.2.1 Red and blue swap

The red and blue components can be swapped, this is done by setting the RBS bit in the

DMA2D_OPFCCR register.

This feature exists on the STM32L4 Series and STM32L4 Plus Series.

5.2.2 Byte swap

The MSB and the LSB bytes of a half-word are swapped in the output FIFO. This is done by

setting the SB bit in the DMA2D_OPFCCR register.

This feature is present only on the STM32L4 Plus Series.

Table 5 shows the swap operations required to match the LCD display color coding

depending on the display color depth and the bus interface width.

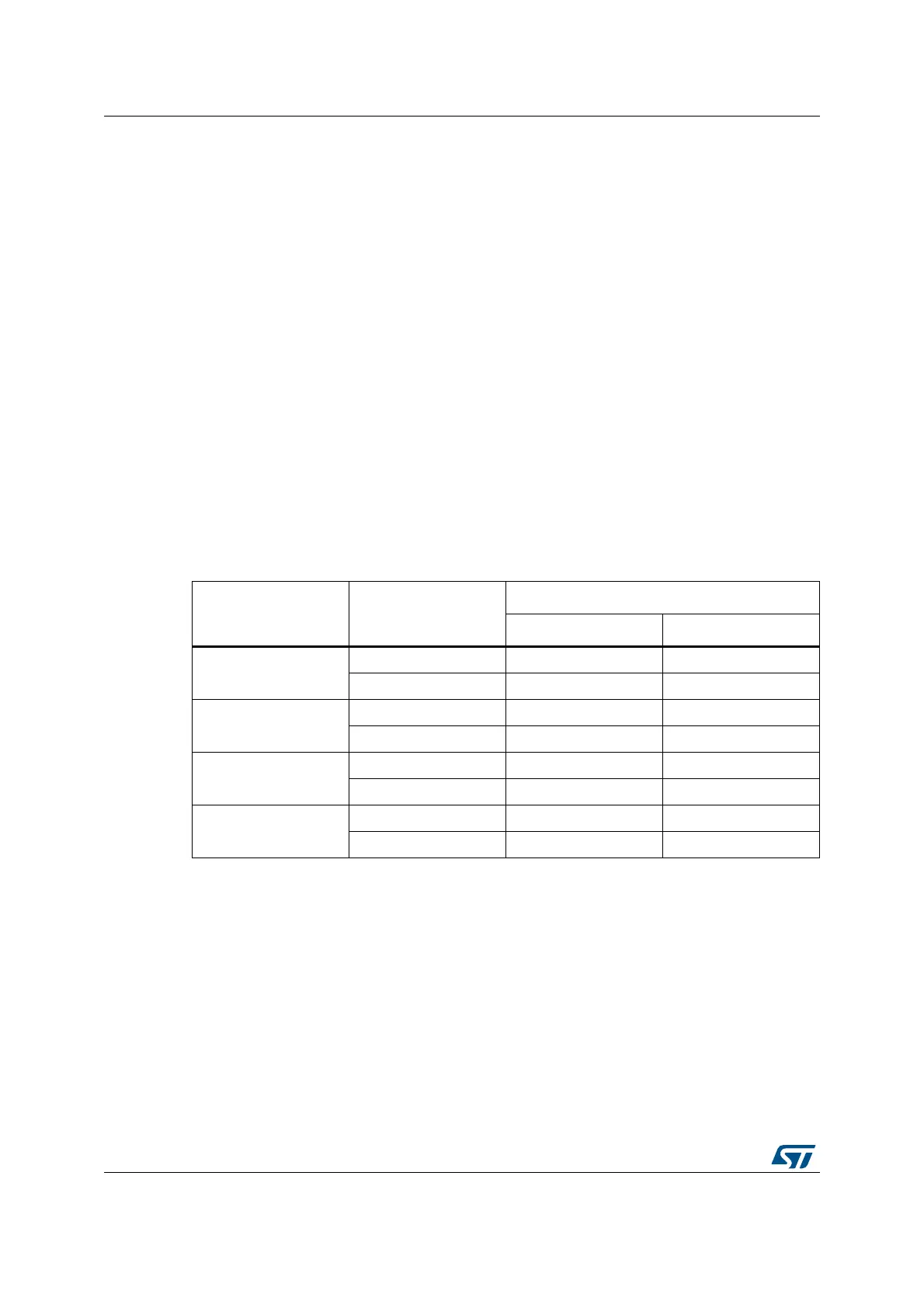

Table 5. Swap operations

Color depth Interface bus width

Required operation

Red blue swap Byte swap

8bpp (256 colors)

8-bit N N

16-bit N Y

16bpp (64k colors)

8-bit N Y

16-bit N N

18bpp (262k colors)

8-bit Y N

16-bit Y Y

24bpp (16.7M colors)

8-bit Y N

16-bit Y Y

Loading...

Loading...