DocID029937 Rev 2 9/22

AN4943 LCD-TFT display on FSMC

21

3.3 Controlling the D/CX signal with STM32L496xx/L4A6xx/

L4Rxxx/L4Sxxx microcontrollers

The D/CX signal of the DBI protocol is used to distinguish the commands (when D/CX = 0)

from the data (when D/CX = 1) transfers.

There are 2 ways to control the 'Data/Command control' (D/CX) signal:

1. By using a dedicated GPIO:

– Setting the 'Data/Command control' signal in "command mode" (setting the GPIO

connected to the D/CX signal to '0' by software)

– Sending the command

– Setting the 'Data/Command control' signal in "data mode" (setting the GPIO

connected to the D/CX signal to '1' by software)

– Sending the data (frame buffer)

2. By using an address bit of the FSMC address bus:

– Reserving a “low level” address in the memory map for the command transfer

– Reserving the higher memory map range for the data transfer

When using the DMA2D to access the LCD-TFT display on FSMC interface, it is important

to remember that even if the LCD-TFT display target is at a fixed address, the Chrom-ART

Accelerator™ (DMA2D) increments the address bus of the transmitted data at each access

(like a memory to memory access). Thus the FSMC address bus is incremented to cover

the full data range address in the memory map.

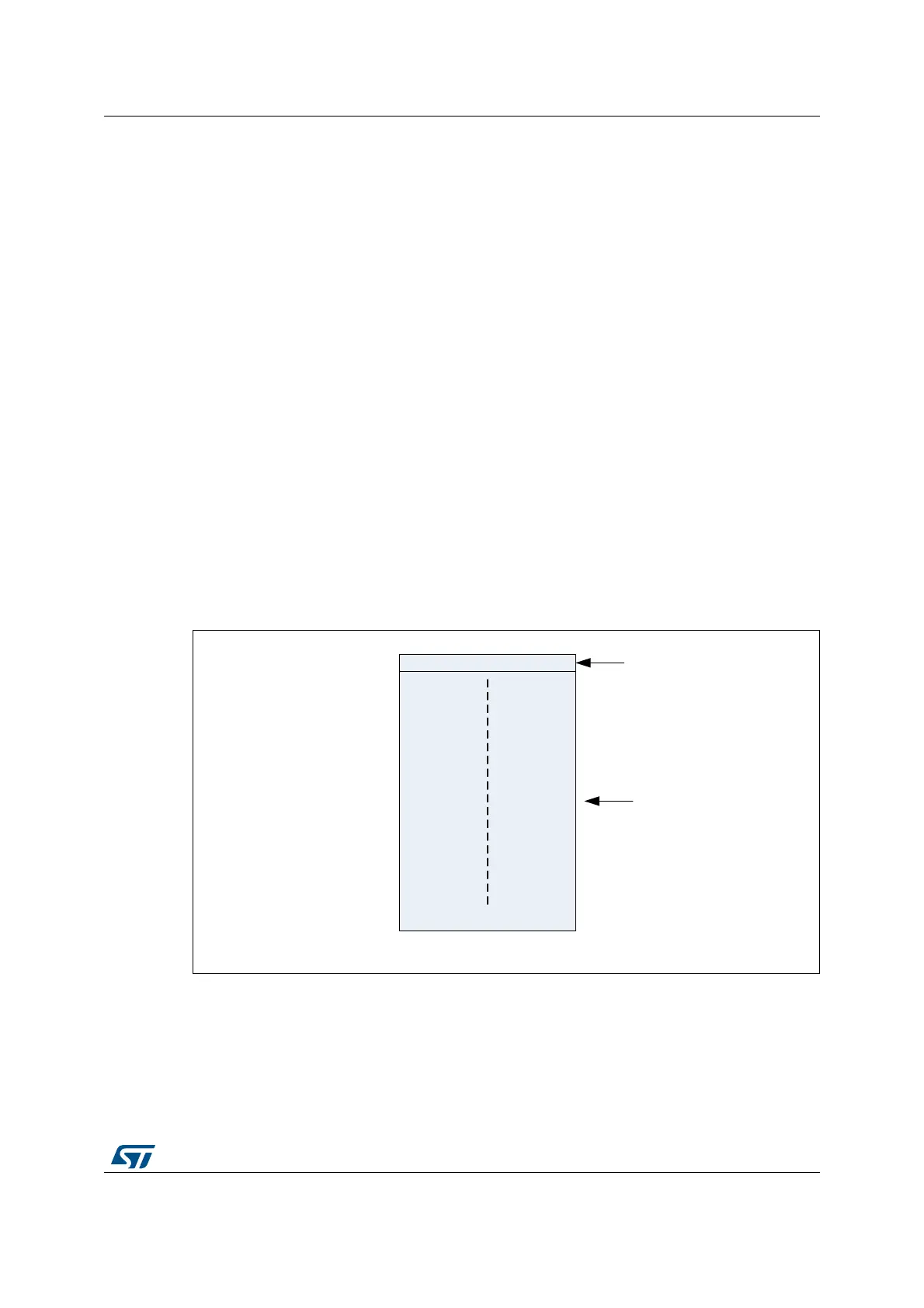

Figure 3. Memory map for LCD-TFT display access

Using the 2

nd

option “an address bit of the FSMC address bus” makes the software simpler

than using the 1

st

option with a dedicated GPIO, but it requires using the “high level”

address to control the ‘data or command select signal’.

• The user cannot use for example the FSMC address LSB bit (FSMC_A0) to control the

‘data or command select signal’

• The user must use a “high enough” FSMC address bit in order to keep for this bit the

same value during the whole image frame buffer transfer.

0xxxxx0000

‘High level’ address

command @

data @ range

MSv44236V1

Loading...

Loading...