TB9100 Reciter Service Manual Appendices 123

© Tait Electronics Limited January 2006

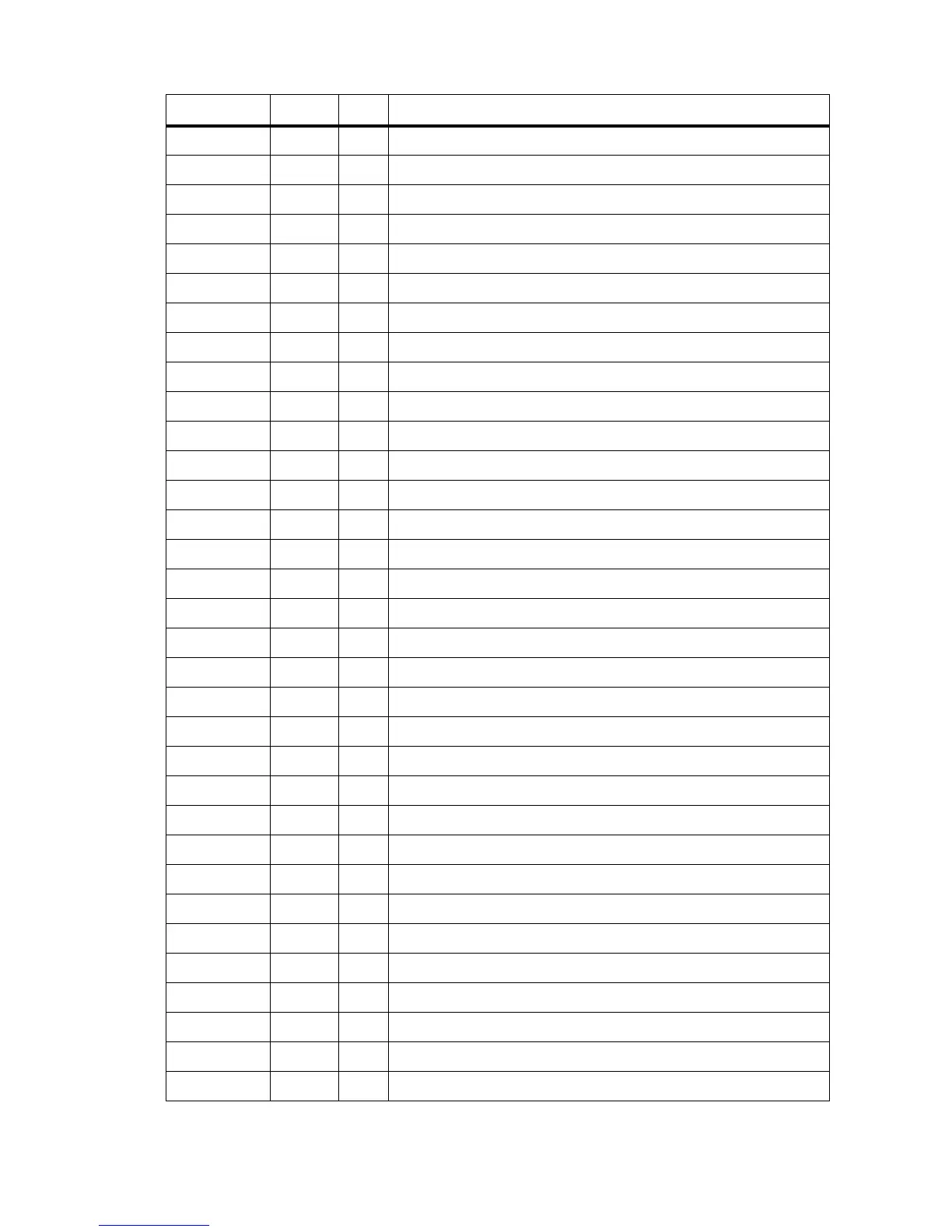

BOOTM3 E5 I/P Boot Mode Selection signal 3

CE0 J2 O/P External memory space enable 0

CE1 H2 O/P External memory space enable 1

CE2 G1 O/P External memory space enable 2

CE3 E4 O/P External memory space enable 3

CLKIN F16 I/P Clock input

CLKMD P16 I/P Clock mode select

CLKMEM B9 O/P Memory interface clock (for SDRAM / SBSRAM

CLKOUT H15 O/P Clock output

CLKR0 U3 I/P Serial shift clock input for McBSP 0

CLKR1 T3 I/P Serial shift clock input for McBSP 1

CLKR2 R5 I/P Serial shift clock input for McBSP 2

CLKS0 U5 I/P Ext. clock source to the sample rate generator 0

CLKS1 P2 I/P Ext. clock source to the sample rate generator 1

CLKS2 P8 I/P Ext. clock source to the sample rate generator 2

CLKX0 U7 I/O Serial shift clock input for McBSP 0

CLKX1 R15 I/O Serial shift clock input for McBSP 1

CLKX2 U8 I/O Serial shift clock input for McBSP 2

CVDD PWR Dedicated power supply for the internal logic (CPU and peripherals)

D[0] C8 I/O External data bus 0

D[1] D7 I/O External data bus 1

D[2] AB I/O External data bus 2

D[3] B6 I/O External data bus 3

D[4] D6 I/O External data bus 4

D[5] B5 I/O External data bus 5

D[6] D5 I/O External data bus 6

D[7] B4 I/O External data bus 7

D[8] D4 I/O External data bus 8

D[9] B3 I/O External data bus 9

D[10] C3 I/O External data bus 10

D[11] D3 I/O External data bus 11

D[12] E3 I/O External data bus 12

D[13] C2 I/O External data bus 13

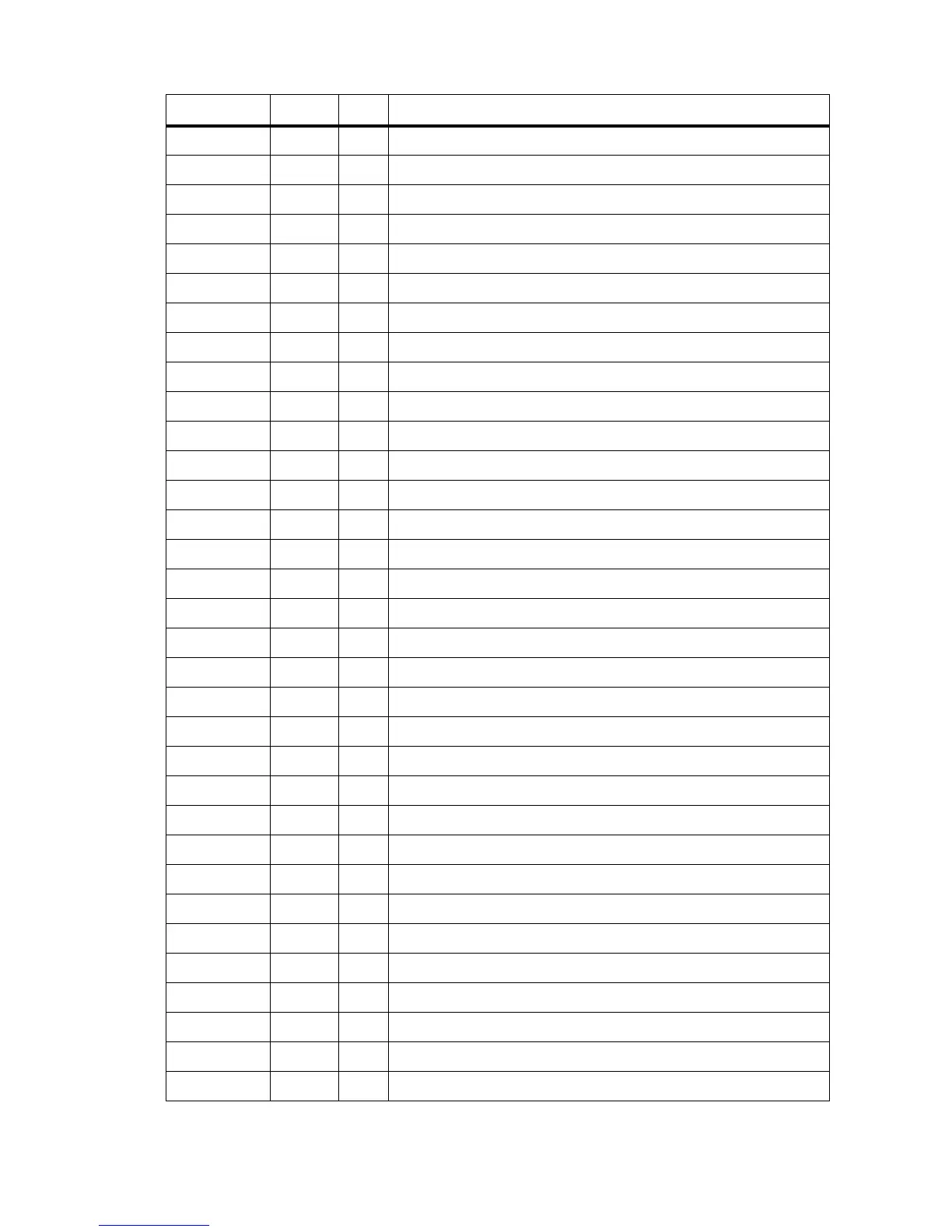

Table 8.11 TMS320VC5510 Port Assignments (Continued)

Pin Name Pin No. Type Function

Loading...

Loading...