38 Network Circuitry TB9100 Reciter Service Manual

© Tait Electronics Limited January 2006

5.2 Risc Processor

5.2.1 Risc Processor

The main processor, U201, is a PowerQUICC MPC859TPZ133, hereafter

abbreviated to MPC. This device consists of a PowerPC derived RISC

processor in conjunction with a micro-coded RISC based Communications

Processor Module (CPM). The RISC processor runs the main application

program(s) under Linux while the CPM offloads the lower level processing

of various serial communications protocols.

The MPC859T is a subset member of the MPC866 PowerQUICC

communications processor family and has fewer communications interfaces

compared to the full function MPC866 device ie. it provides only one serial

communications controller (SCC), instead of the four fitted to the

MPC866.

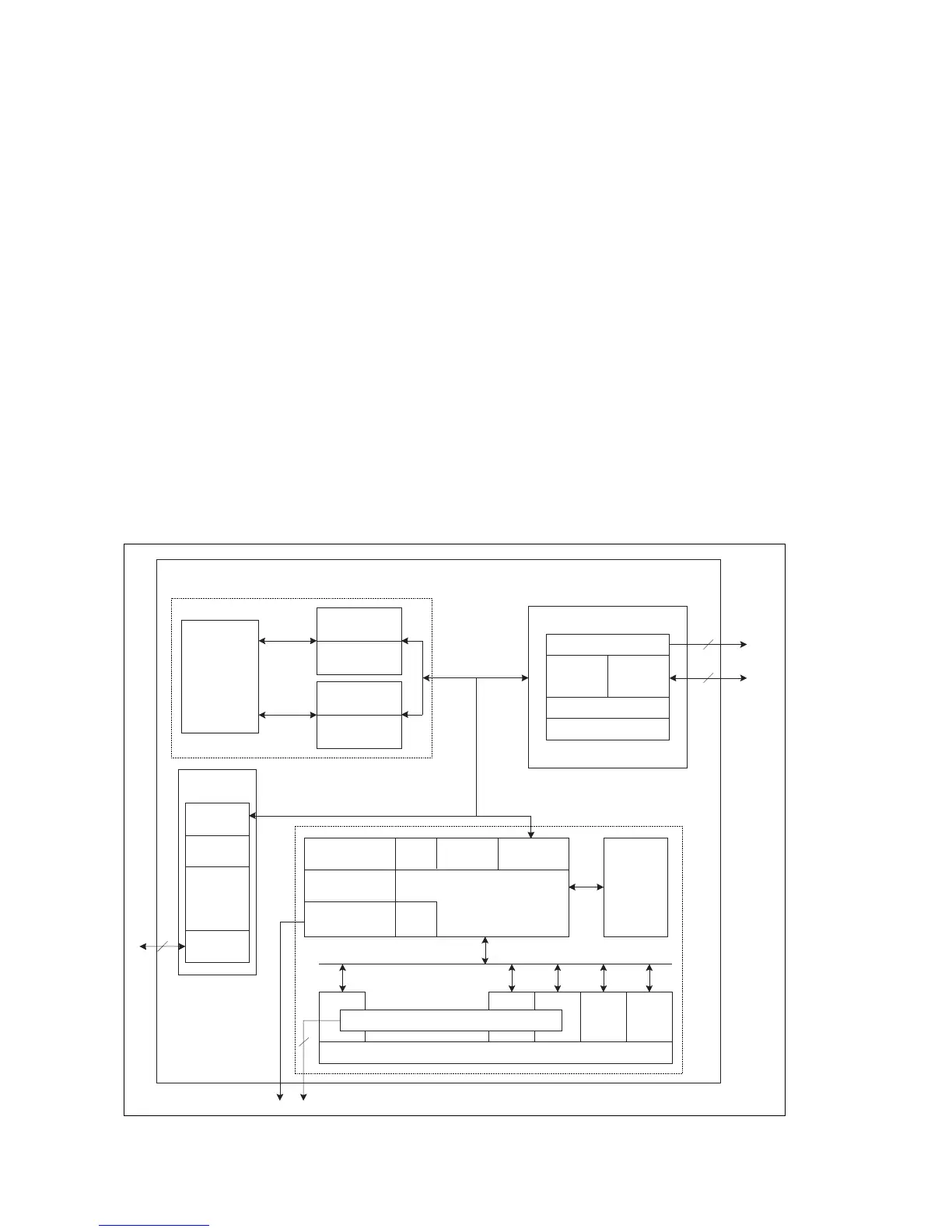

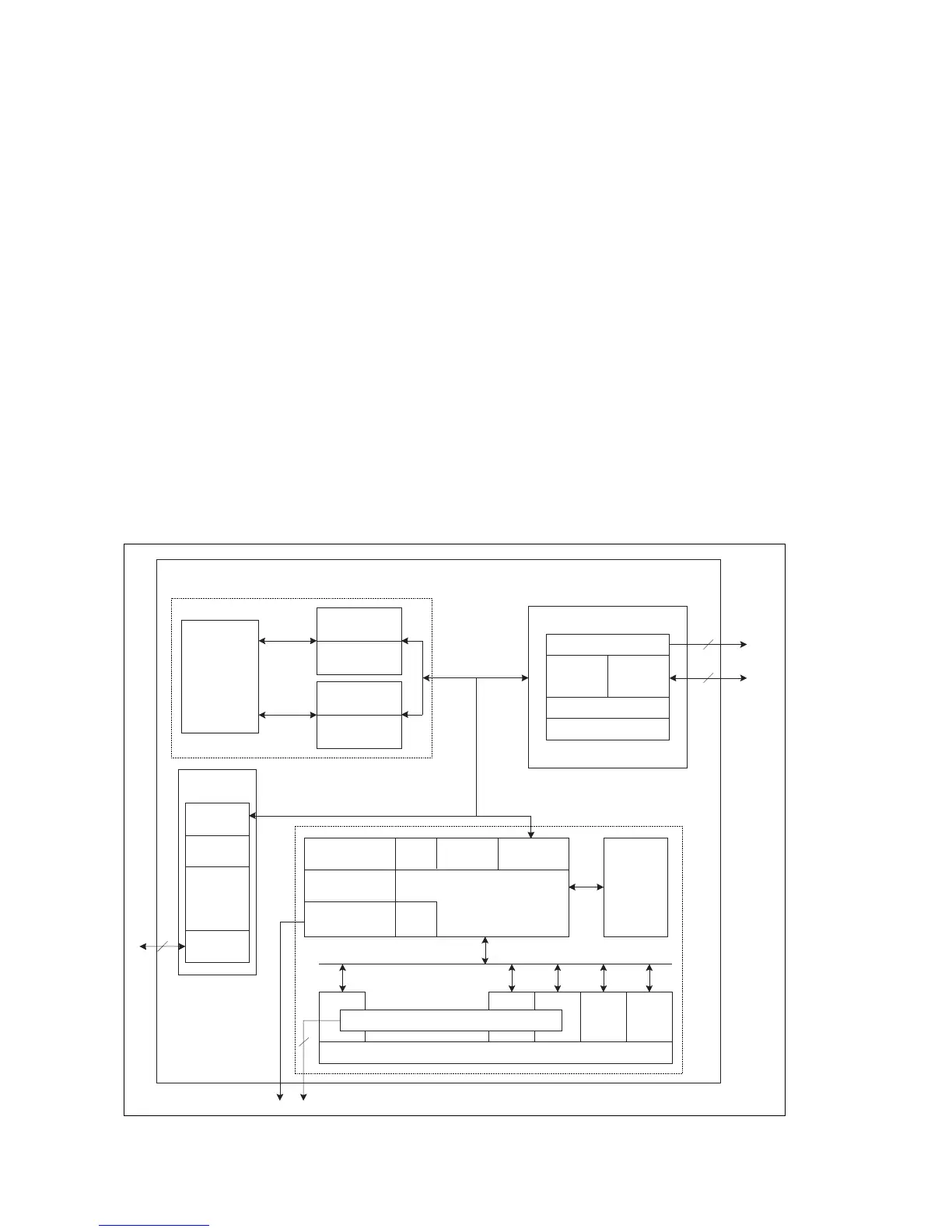

The block diagram (Figure 5.2) shows the internal structure; refer to the

MPC866 data sheet (reference 1) and MPC866 user’s manual (reference 2)

for full details of the internal functions.

Figure 5.2 MPC859T Block Diagram

Embedded

MPC8xx

Processor

Core

Instruction

Bus

Load/Store

Bus

4-Kbyte

Instruction Cache

Instruction MMU

32-Entry ITLB

4-Kbyte

Data Cache

Data MMU

32-Entry DTLB

Fast Ethernet

Controller

DMAs

FIFOs

10/100

Base-T

Media Access

Control

Ethernet

MII

Parallel I/O

4

Timers

Interrupt

Controllers

8-Kybte

Dual-Port RAM

4 Baud

Generators

Parallel Interface

Port and UTOPIA

Timers

10

Serial

and

2

Independent

DMA

Channels

32-Bit RISC Controller

and Program

ROM

Time Slot Assigner

Serial Interface

SCC1 SMC1 SMC2 SP1 I

2

C

POWERPC CORE

CPM

External

Buses

System Interface Unit (SIU)

Memory Controller

Internal

Bus Interface

Unit

External

Bus Interface

Unit

System Functions

PCMCIA-ATA Interface

Unified

Bus

Loading...

Loading...