FPGA Configuration

The Alveo U200/U250 accelerator card supports two UltraScale+™ FPGA conguraon modes:

• Quad SPI ash memory

• JTAG using USB JTAG conguraon port (USB J13/FT4232H U27)

The FPGA bank 0 mode pins are hardwired to M[2:0] = 001 master SPI mode with pull-up/down

resistors.

At power up, the FPGA is congured by the Quad SPI NOR ash device (Micron

MT25QU01GBBA8E12-0SIT) with the FPGA_CCLK operang at clock rate of 105 MHz

(EMCCLK) using the master serial conguraon mode. The Quad SPI ash memory NOR device

has a capacity of 1 Gb.

If the JTAG cable is plugged in, QSPI conguraon might not occur. JTAG mode is always

available independent of the mode pin sengs.

For complete details on conguring the FPGA, see the UltraScale Architecture Conguraon User

Guide (UG570).

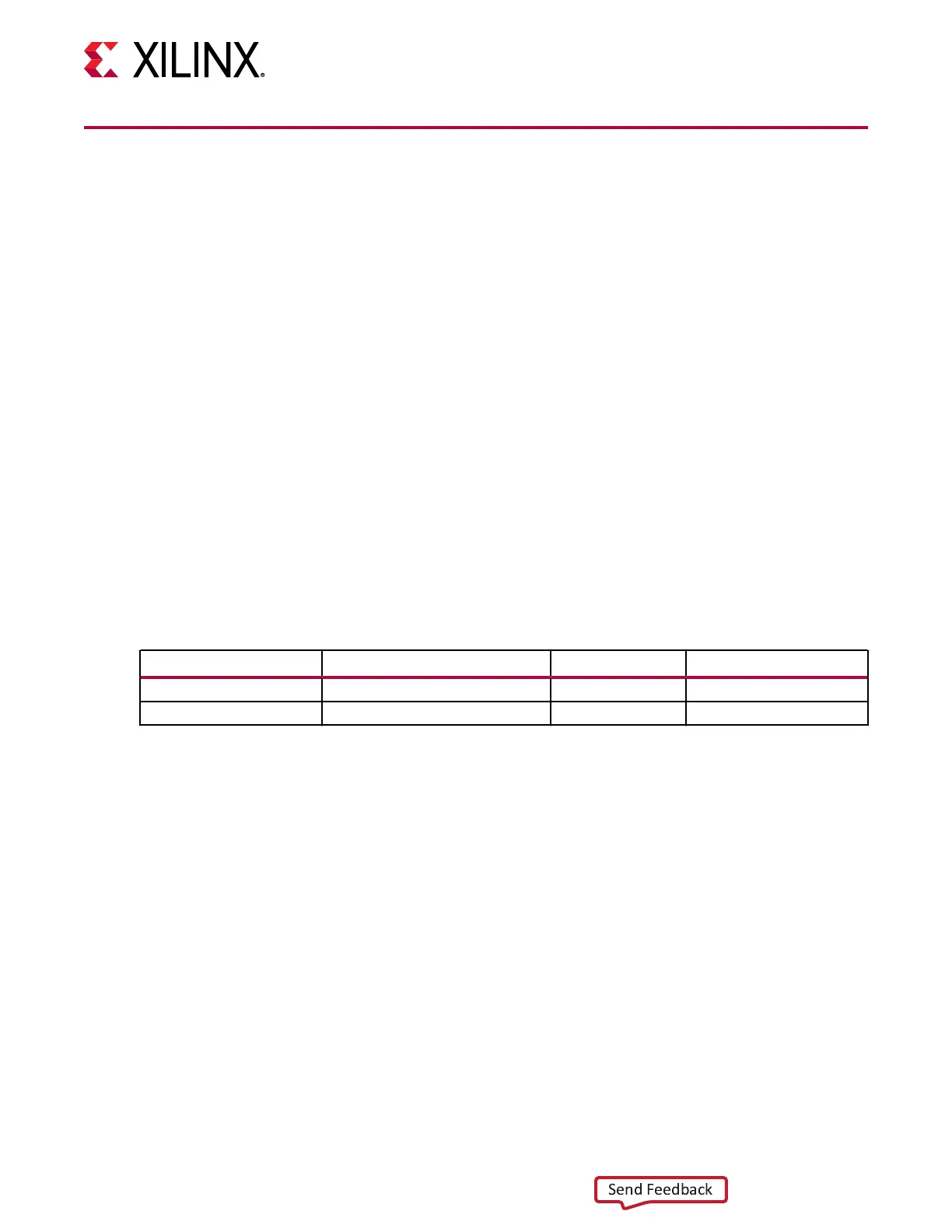

Table 2: Configuration Modes

Configuration Mode M[2:0] Bus Width CCLK Direction

Master SPI 001 x1, x2, x4 FPGA output

JTAG Not applicable – JTAG overrides x1 Not applicable

Chapter 2: Card Installation and Configuration

UG1289 (v1.1.1) November 20, 2019 www.xilinx.com

Alveo U200 and U250 Accelerator Cards 15

Loading...

Loading...