32 www.xilinx.com VC7203 IBERT Getting Started Guide

UG847 (v3.0) July 10, 2013

Chapter 1: VC7203 IBERT Getting Started Guide

9. In the Clock Settings tab, select DIFF SSTL15 for the I/O Standard, enter E19 for P

Package Pin and E18 for N Package Pin (the FPGA pins that the system clock connects

to), and make sure the Frequency is set to 200.00 (Figure 1-26). Press OK. A Generate

Output Products window opens. Leave the defaults unchanged, and press OK.

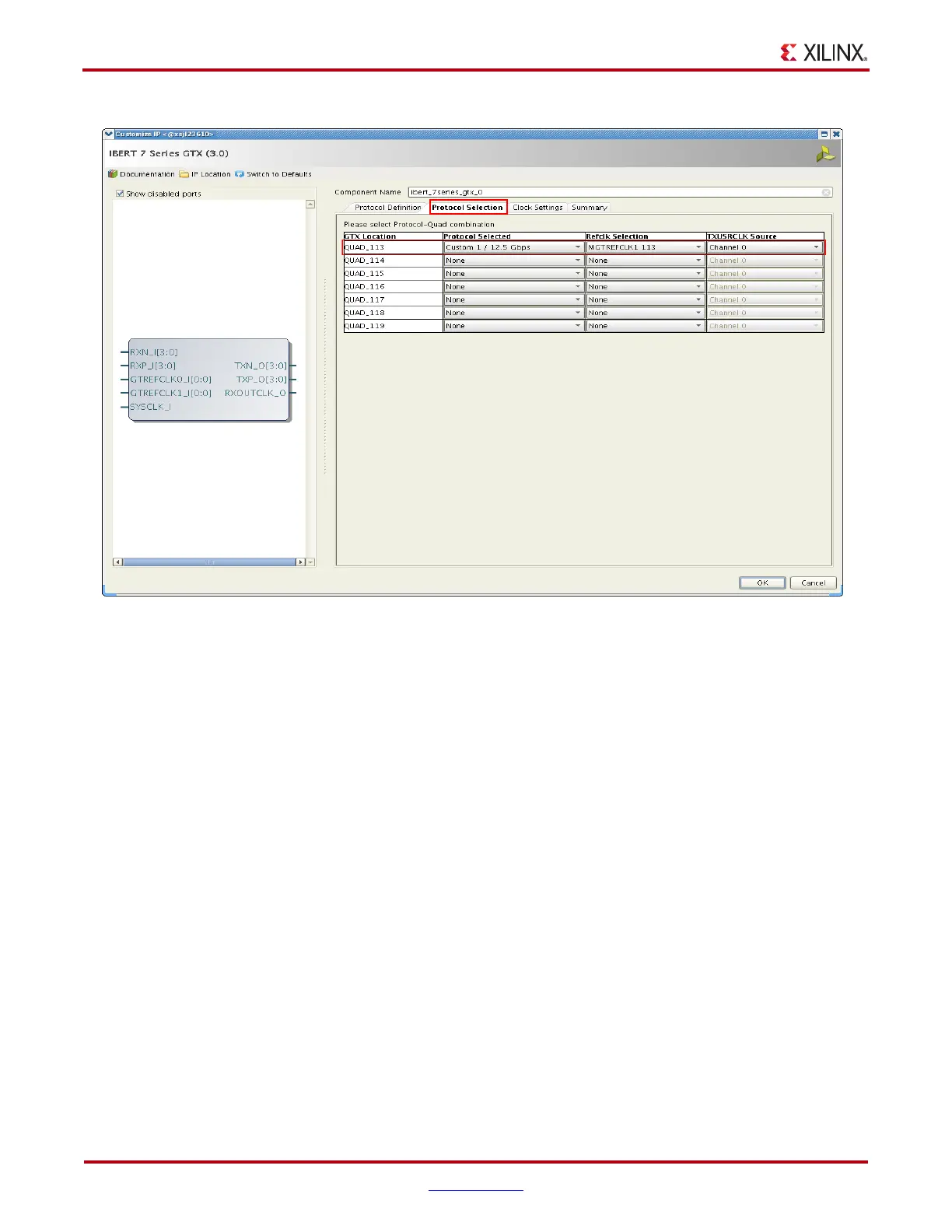

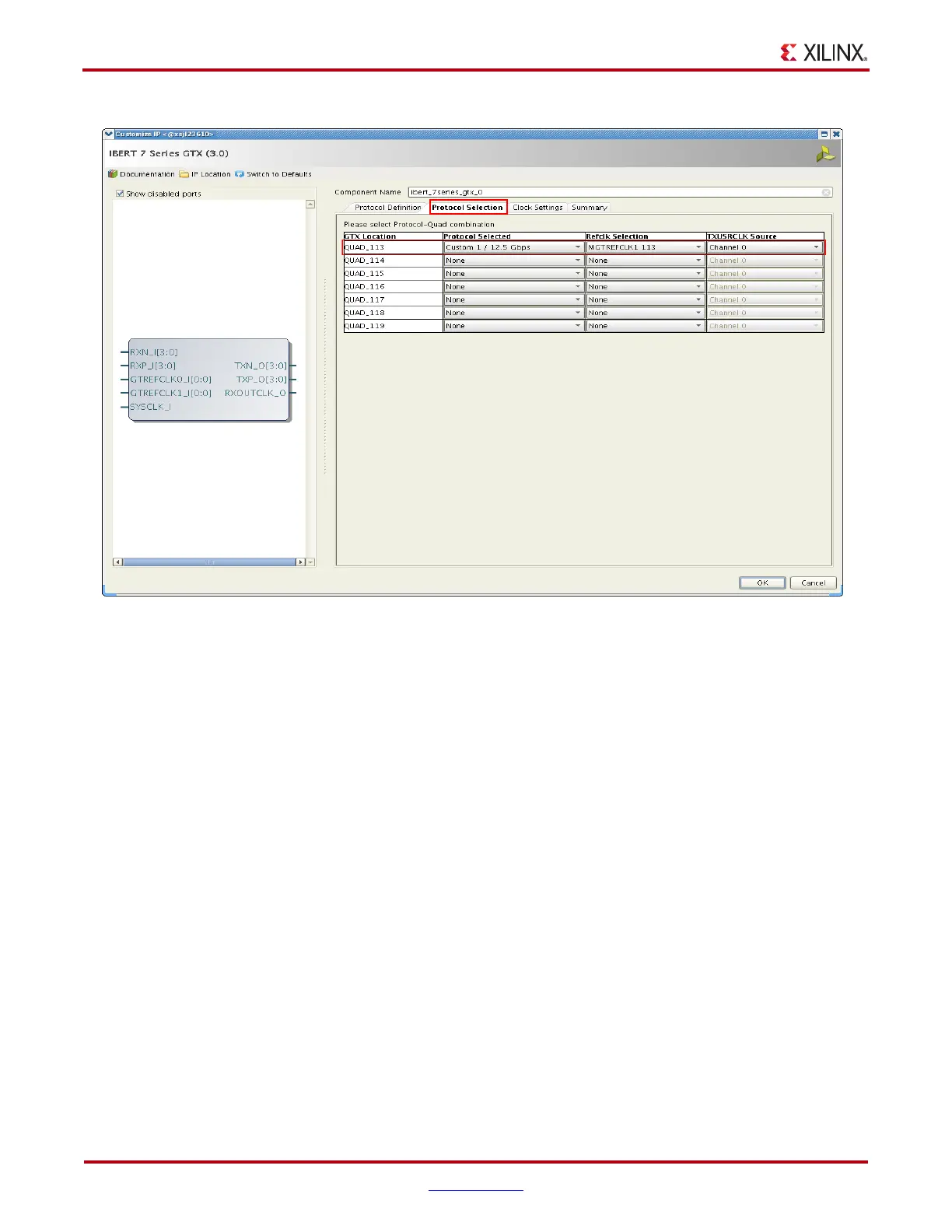

X-Ref Target - Figure 1-25

Figure 1-25: Customize IP - Protocol Selection

Loading...

Loading...