Zynq UltraScale+ VCU TRD User Guide 53

UG1250 (v2019.1) May 29, 2019 www.xilinx.com

Chapter 4: System Considerations

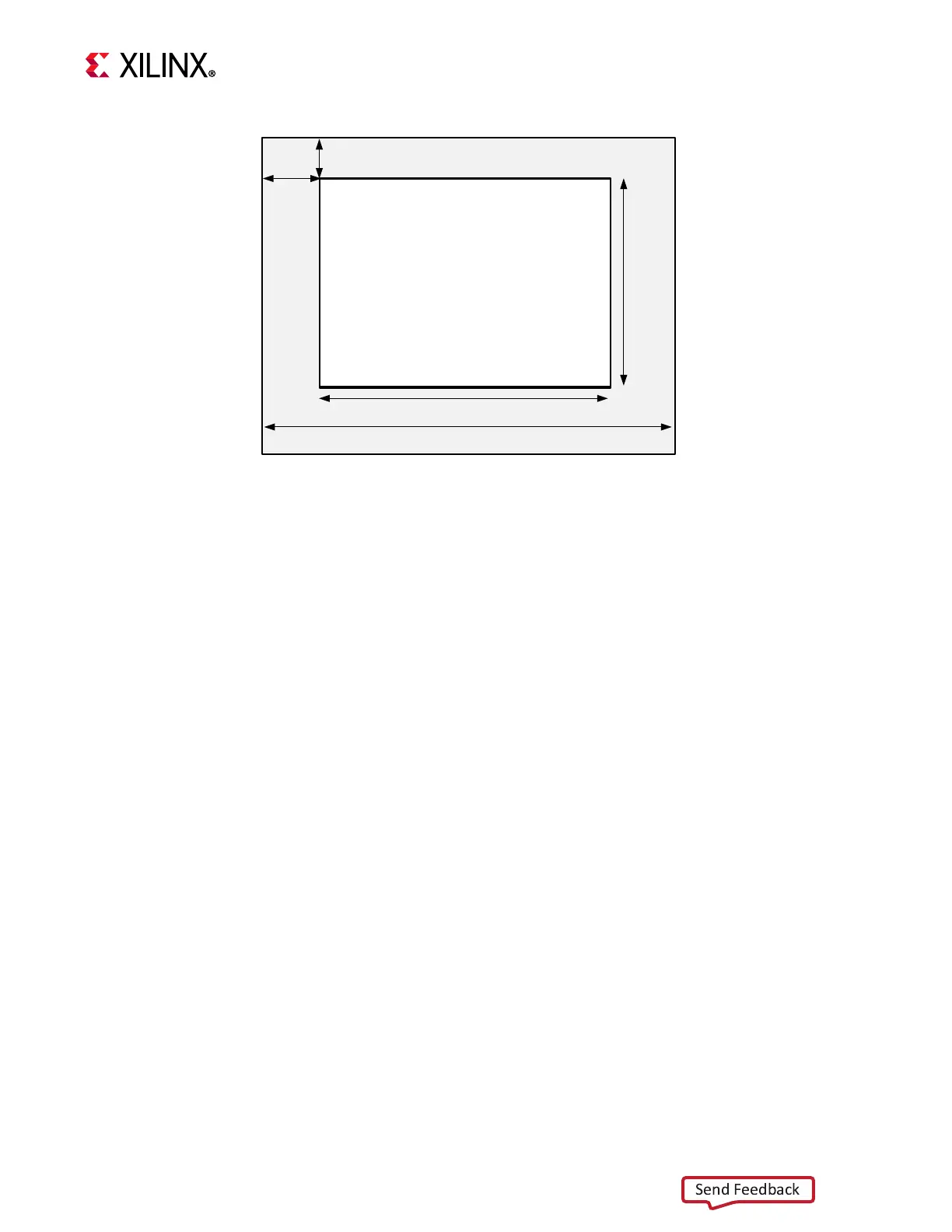

The active area is the part of the video buffer that is visible on the screen. The active area is

defined by the height and width parameters, also called the video dimensions. Those are

typically expressed in number of pixels because the bits per pixel depend on the pixel

format as explained above.

The stride or pitch is the number of bytes from the first pixel of a line to the first pixel of the

next line of video. In the simplest case, the stride equals the width multiplied by the bits per

pixel, converted to bytes. For example, AR24 requires 32 BPP which is four bytes per pixel.

A video buffer with an active area of 1920 x 1080 pixels therefore has a stride of

4 x 1920 = 7,680 bytes. Some DMA engines require the stride to be a power of two to

optimize memory accesses. In this design, the stride always equals the width in bytes.

X-Ref Target - Figure 4-2

Figure 4-2: Video Buffer Area

x-offset

y-offset

height

width

stride

fb

Active Area

X19455-112718

Loading...

Loading...