eZ80

®

CPU

User Manual

UM007714-0908 Memory Modes

8

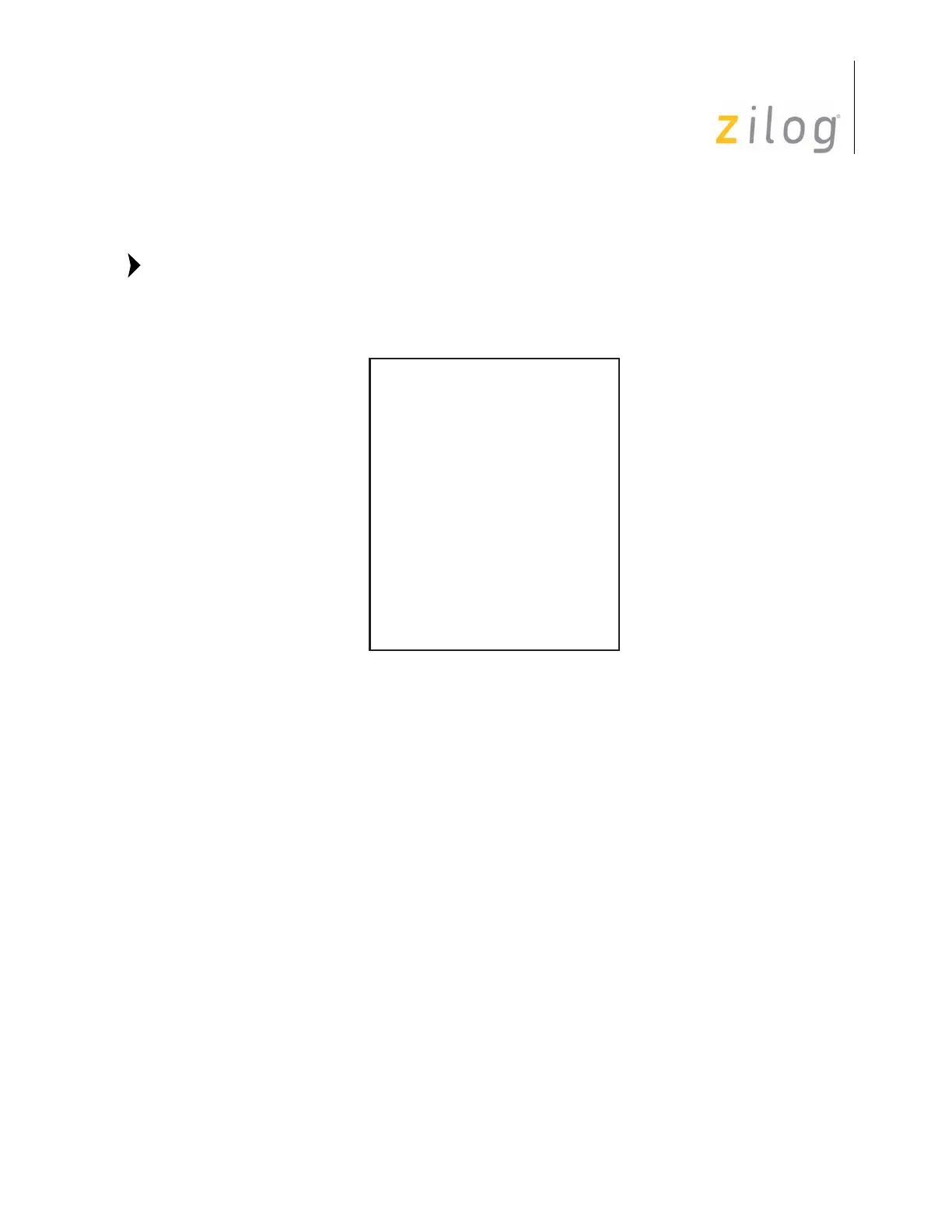

set. When ADL mode is selected, MBASE does not affect memory addressing. Figure 5

displays the ADL mode memory map.

There are no pages in ADL mode.

In ADL mode, the CPU’s multibyte registers are expanded from 16 to 24 bits. A 24-bit

Stack Pointer Long (SPL) register replaces the 16-bit Stack Pointer Short (SPS) register.

For more information on the CPU registers in ADL mode, see eZ80

®

CPU Registers in

ADL Mode on page 12.

In ADL mode, all addresses and data are 24 bits. All data READ and WRITE operations

pass 3 bytes of data to and from the CPU when operating in ADL mode (as opposed to

only 2 bytes of data while in Z80 mode operation). Thus, instructions operating in ADL

mode may require more clock cycles to complete than in Z80 mode. Although MBASE

does not affect operation during ADL mode, the MBASE register can only be written to

when operating in ADL mode.

Figure 5. ADL Addressing Mode Memory Map

ADL Mode

16 MB Linear

Memory Space

Memory

Location

24-Bit

Address

000000h

FFFFFFh

000000h

FFFFFFh

Loading...

Loading...