eZ80

®

CPU

User Manual

UM007714-0908 CPU Instruction Set

291

RES b, r

Reset Bit

Operation

r[b] ← 0

Description

The

r

operand is any of the 8-bit CPU registers A, B, C, D, E, H, or L. Bit

b

of the speci-

fied register

r

is reset to 0.

Condition Bits Affected

None.

Attributes

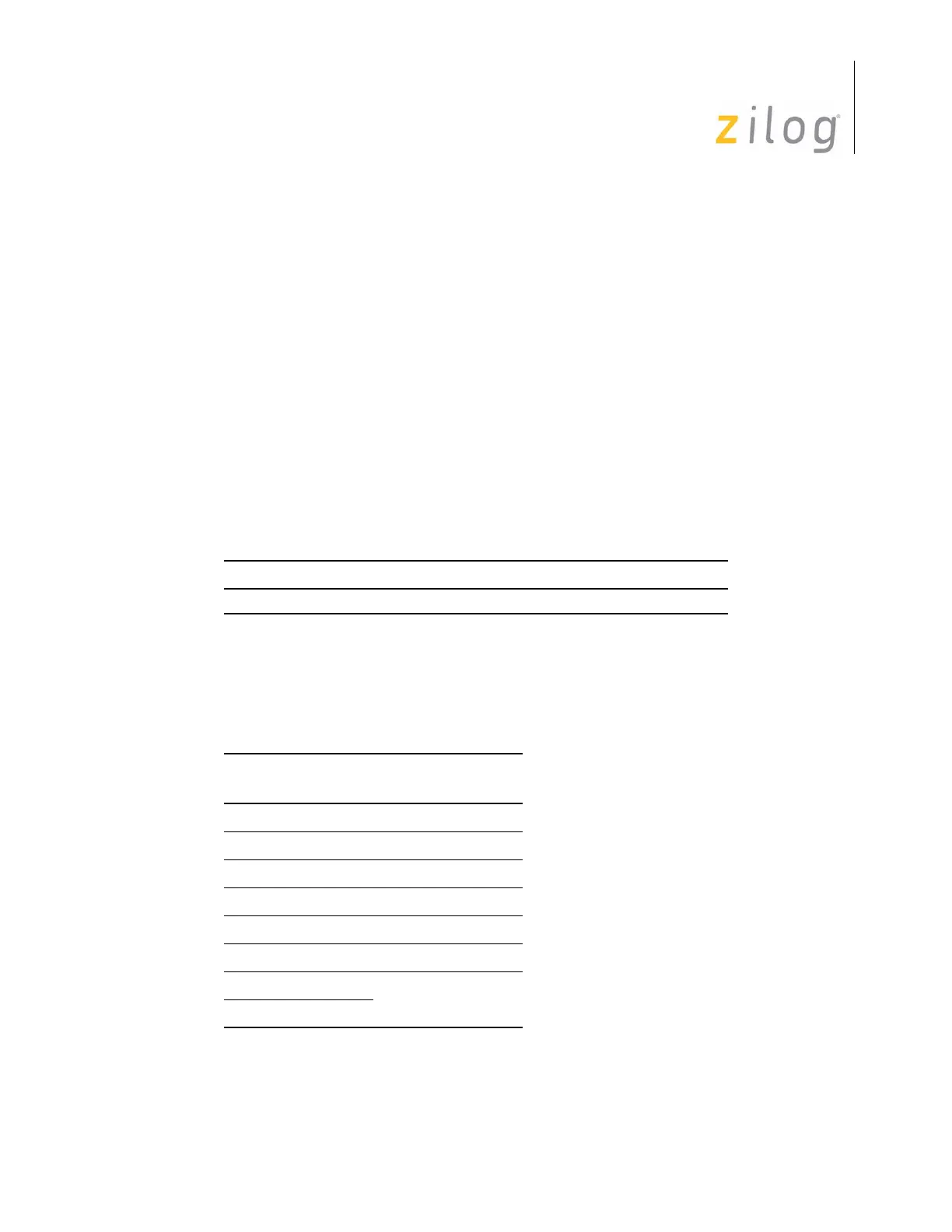

jj = binary code 10 bbb rrr, and kk = binary code 10 bbb 110; where rrr identifies

the A, B, C, D, E, H, or L register and

bbb identifies the bit tested and assembled into the

object code, as indicated in Table 82.

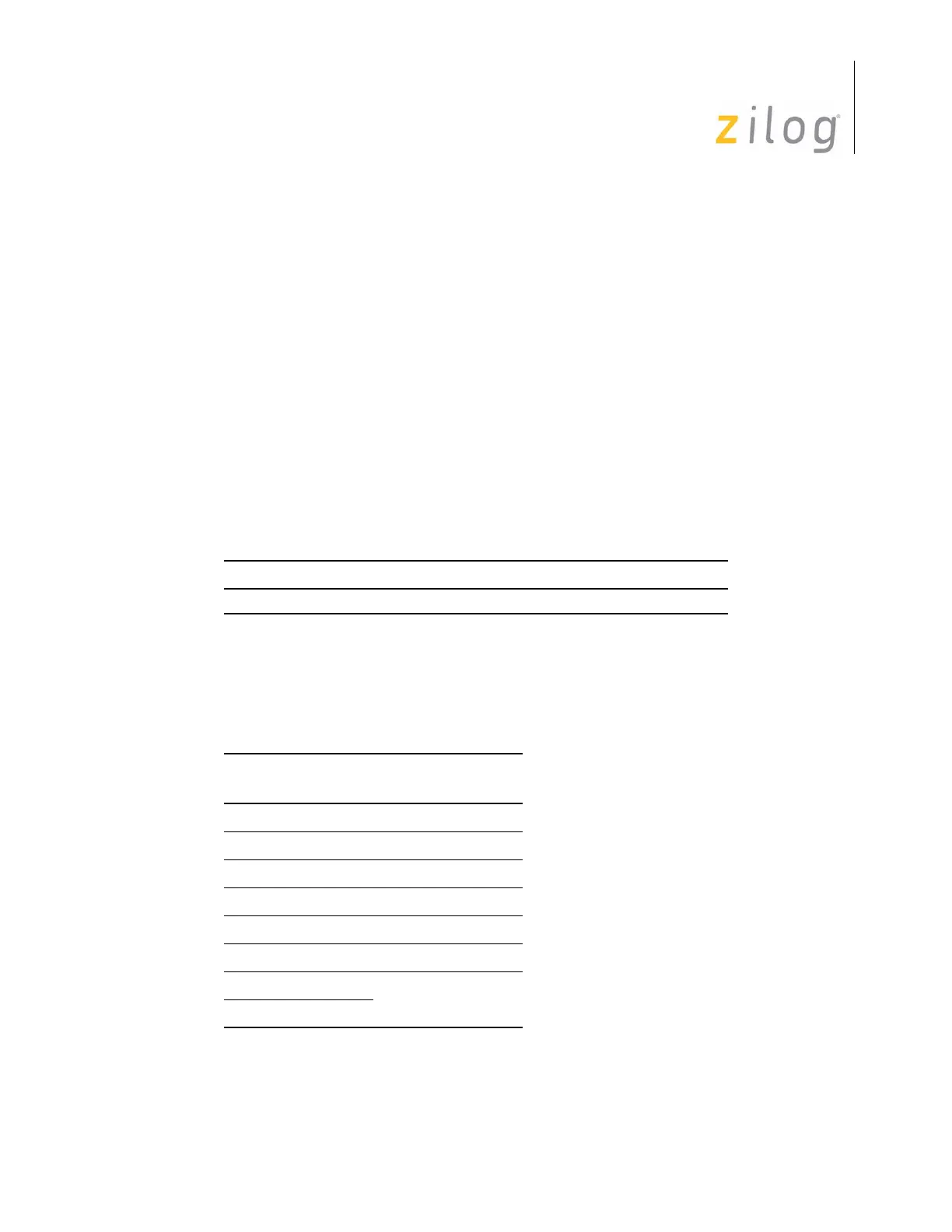

Mnemonic Operand ADL Mode Cycle Opcode (hex)

RES b,r X2CB, jj

Table 82. Register, bbb, and rrr Opcodes for RES b, r Instruction (hex)

Bit

Tested bbb Register rrr

0 000 A 111

1 001 B 000

2 010 C 001

3 011 D 010

4 100 E 011

5 101 H 100

6 110 L 101

7 111

Loading...

Loading...