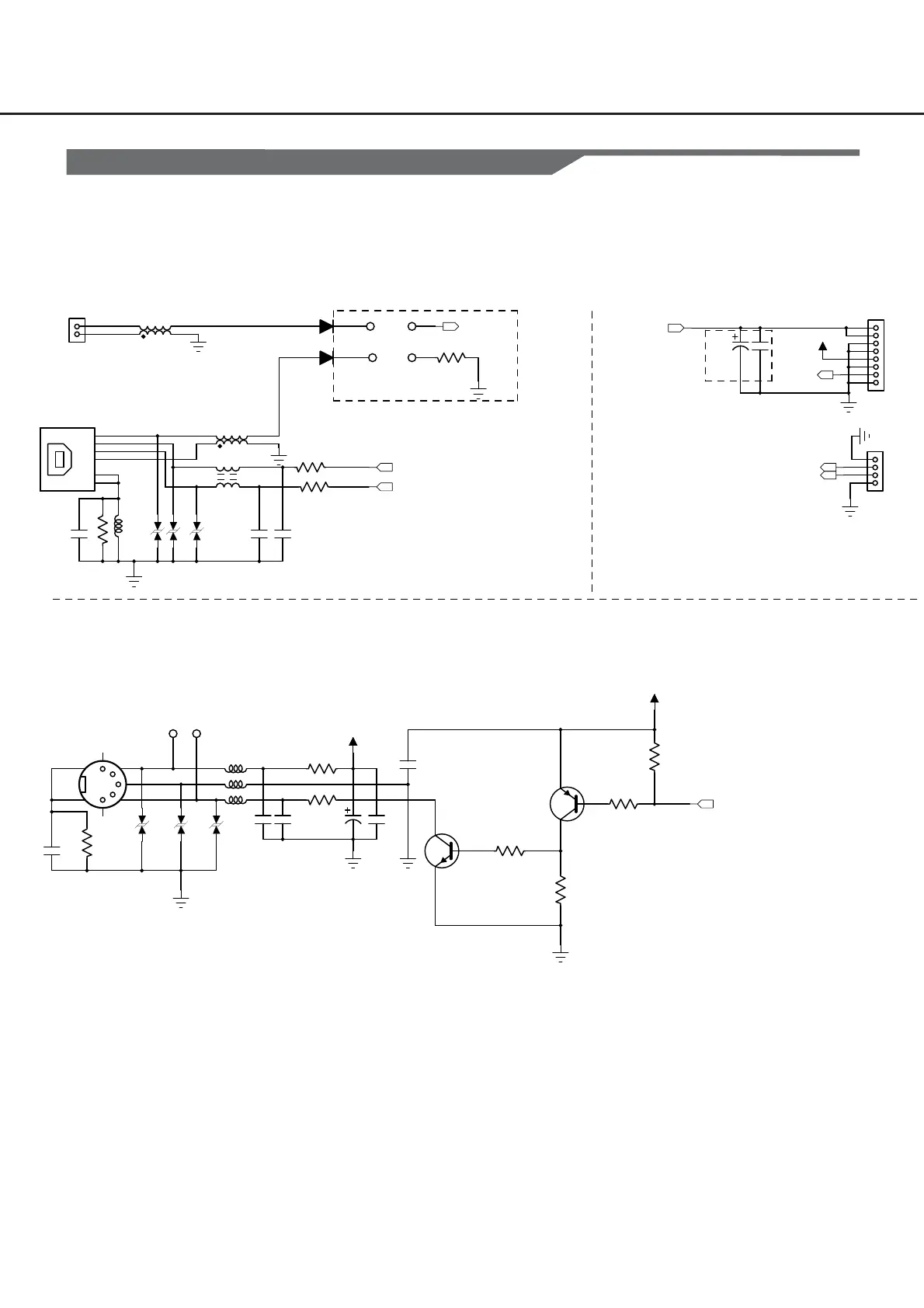

Circuit Boards

2 - ALL CAPACI TANCE VALUES ARE I NDI CATED I N "F". ( U = 0. 000001F; P = 0. 000001UF. )

1 - ALL RESI STANCE VALUES ARE I NDI CATED I N " ohm". ( K = 1, 000ohm; M = 1, 000, 000ohm. )

RE MARK :

ARM_S DRAM

PCM_FLASH

SPI_FLASH

1

VDD

2

DQ0

3

VDDQ

4

DQ1

5

DQ2

6

VS S Q

7

DQ3

8

DQ4

9

VDDQ

10

DQ5

11

DQ6

12

VS S Q

13

DQ7

14

VDD

15

DQML

16

/WE

17

/CAS

18

/RAS

19

/CS

20

BA0

21

BA1

22

A1 0

23

A0

24

A1

25

A2

26

A3

27

VDD

28

VS S

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

35

A1 1

36

A1 2

37

CKE

38

CLK

39

DQMH

40

NC

41

VS S

42

DQ8

43

VDDQ

44

DQ9

45

DQ1 0

46

VS S Q

47

DQ1 1

48

DQ1 2

49

VDDQ

50

DQ1 3

51

DQ1 4

52

VS S Q

53

DQ1 5

54

VS S

U2 1

MT 4 8 L C 8 M1 6

1

#CE

2

SO

3

#WP

7

#HOLD

6

SCK

5

SI

4

GND

8

VCC

U2 5

MX 2 5 L 4 0 0 6 E M2 I

C1 0 9

0. 1uF

C1 1 0

0. 1uF

C1 1 1

0. 1uF

C1 1 2

0. 1uF

C1 1 3

0. 1uF

R7 8

10K

C6 4

0. 1uF

C1 3 5

0. 1uF

C1 3 6

0. 1uF

C1 3 9

0. 1uF

C1 4 0

0. 1uF

C1 4 1

0. 1uF

C1 4 2

0. 1uF

C1 4 3

0. 1uF

1

A2 3

2

A2 2

3

A1 5

4

A1 4

5

A1 3

6

A1 2

7

A1 1

8

A1 0

9

A9

10

A8

11

A1 9

12

A2 0

13

WE

14

RES E T

15

A2 1

16

WP

17

RY/ BY

18

A1 8

19

A1 7

20

A7

21

A6

22

A5

23

A4

24

A3

25

A2

26

A1

27

NC

28

NC

29

VI O

30

NC

31

A0

32

CE

33

VS S

34

OE

35

D0

36

D8

37

D1

38

D9

39

D2

40

D1 0

41

D3

42

D1 1

43

VCC

44

D4

45

D1 2

46

D5

47

D1 3

48

D6

49

D1 4

50

D7

51

D1 5

52

VS S

53

BYTE

54

A1 6

55

A2 5

56

A2 4

U2 0

SI C- TSOP5 6- S2 9GL512

TP1

TP2

TP3

TP4

C1 1 4

0. 1uF

C1 1 5

0. 1uF

C1 1 6

0. 1uF

C1 1 7

0. 1uF

C1 1 8

0. 1uF

R13

10K

R14

10K

R2 8

0

R2 9

10K

C3 8

0. 1uF

1

VDD

2

DQ0

3

VDDQ

4

DQ1

5

DQ2

6

VS S Q

7

DQ3

8

DQ4

9

VDDQ

10

DQ5

11

DQ6

12

VS S Q

13

DQ7

14

VDD

15

DQML

16

/WE

17

/CAS

18

/RAS

19

/CS

20

BA0

21

BA1

22

A1 0

23

A0

24

A1

25

A2

26

A3

27

VDD

28

VS S

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

35

A1 1

36

A1 2

37

CKE

38

CLK

39

DQMH

40

NC

41

VS S

42

DQ8

43

VDDQ

44

DQ9

45

DQ1 0

46

VS S Q

47

DQ1 1

48

DQ1 2

49

VDDQ

50

DQ1 3

51

DQ1 4

52

VS S Q

53

DQ1 5

54

VS S

U8

MT 4 8 L C 8 M1 6

M1 7

MI S O / R X 1 / G P I O 0 [ 1 6 ]

M1 6

MO S I / T X 1 / G P I O 0 [ 1 7 ]

M1 5

SPI _ CS/ RX2/ GPI O0[ 1 8]

M1 4

SPI _ CLK/ TX2/ GPI O0[ 1 9]

U1 - P

A5 - 2 8 9 _ NE W

R5

ARM_ D[ 0 0 ]

N6

ARM_ D[ 0 1 ]

T4

ARM_ D[ 0 2 ]

U3

ARM_ D[ 0 3 ]

T3

ARM_ D[ 0 4 ]

R4

ARM_ D[ 0 5 ]

P5

ARM_ D[ 0 6 ]

U2

ARM_ D[ 0 7 ]

U1

ARM_ D[ 0 8 ]

T2

ARM_ D[ 0 9 ]

M4

ARM_ D[ 1 0 ]

R3

ARM_ D[ 1 1 ]

T1

ARM_ D[ 1 2 ]

R2

ARM_ D[ 1 3 ]

P3

ARM_ D[ 1 4 ]

M5

ARM_ D[ 1 5 ]

U1 - D

A5 - 2 8 9 _ NE W

K2

ARM_ A[ 0 0 ]

K3

ARM_ A[ 0 1 ]

J5

ARM_ A[ 0 2 ]

H4

ARM_ A[ 0 3 ]

J1

ARM_ A[ 0 4 ]

J2

ARM_ A[ 0 5 ]

J3

ARM_ A[ 0 6 ]

H5

ARM_ A[ 0 7 ]

H1

ARM_ A[ 0 8 ]

H2

ARM_ A[ 0 9 ]

G1

ARM_ A[ 1 0 ]

G2

ARM_ A[ 1 1 ]

H3

ARM_ A[ 1 2 ]

U1 - C

A5 - 2 8 9 _ NE W

L4

ARM_ D[ 1 6 ] / GP I O3 [ 0 0 ]

R1

ARM_ D[ 1 7 ] / GP I O3 [ 0 1 ]

P2

ARM_ D[ 1 8 ] / GP I O3 [ 0 2 ]

N3

ARM_ D[ 1 9 ] / GP I O3 [ 0 3 ]

P1

ARM_ D[ 2 0 ] / GP I O3 [ 0 4 ]

L5

ARM_ D[ 2 1 ] / GP I O3 [ 0 5 ]

K4

ARM_ D[ 2 2 ] / GP I O3 [ 0 6 ]

N2

ARM_ D[ 2 3 ] / GP I O3 [ 0 7 ]

N1

ARM_ D[ 2 4 ] / GP I O3 [ 0 8 ] / MP U_ D[ 8 ]

M3

ARM_ D[ 2 5 ] / GP I O3 [ 0 9 ] / MP U_ D[ 9 ]

K5

ARM_ D[ 2 6 ] / GP I O3 [ 1 0 ] / MP U_ D[ 1 0 ]

M2

ARM_ D[ 2 7 ] / GP I O3 [ 1 1 ] / MP U_ D[ 1 1 ]

M1

ARM_ D[ 2 8 ] / GP I O3 [ 1 2 ] / MP U_ D[ 1 2 ]

J4

ARM_ D[ 2 9 ] / GP I O3 [ 1 3 ] / MP U_ D[ 1 3 ]

L3

ARM_ D[ 3 0 ] / GP I O3 [ 1 4 ] / MP U_ D[ 1 4 ]

L2

ARM_ D[ 3 1 ] / GP I O3 [ 1 5 ] / MP U_ D[ 1 5 ]

U1 - E

A5 - 2 8 9 _ NE W

P6

ARM_ WR/ GP I O3 [ 1 6 ] / BOOT [ 0 ]

U4

ARM_ RD/ GP I O3 [ 1 7 ] / BOOT [ 1 ]

T5

ARM_ CS / GP I O3 [ 1 8 ]

U5

ARM_ S DR AM_ CS

G5

ARM_ S DR AM_ CKE

G3

ARM_ S DR AM_ CL K_ I N

G4

ARM_ S DR AM_ CL K

N4

ARM_ S DR AM_ CAS

N5

ARM_ S DR AM_ RAS

P4

ARM_ S DR AM_ WE

T6

ARM_ S DR AM_ DQM0

R6

ARM_ S DR AM_ DQM[ 1 ]

N7

ARM_ S DR AM_ DQM[ 2 ] / GP I O3 [ 1 9 ]

U6

ARM_ S DR AM_ DQM[ 3 ] / GP I O3 [ 2 0 ]

K1

ARM_ S DR AM_ B[ 1 ]

L1

ARM_ S DR AM_ B[ 0 ]

U1 - B

A5 - 2 8 9 _ NE W

U1 4

PCM_ A[ 0 0]

R1 1

PCM_ A[ 0 1]

T1 3

PCM_ A[ 0 2]

P11

PCM_ A[ 0 3]

N1 1

PCM_ A[ 0 4]

T1 2

PCM_ A[ 0 5]

U1 3

PCM_ A[ 0 6]

U1 2

PCM_ A[ 0 7]

T1 1

PCM_ A[ 0 8]

R1 0

PCM_ A[ 0 9]

P10

PCM_ A[ 1 0]

N1 0

PCM_ A[ 1 1]

U1 1

PCM_ A[ 1 2]

T1 0

PCM_ A[ 1 3]

U1 0

PCM_ A[ 1 4]

R9

PCM_ A[ 1 5]

T9

PCM_ A[ 1 6]

U9

PCM_ A[ 1 7]

P9

PCM_ A[ 1 8]

N9

PCM_ A[ 1 9]

U8

PCM_ A[ 2 0]

T8

PCM_ A[ 2 1]

R8

PCM_ A[ 2 2]

P8

PCM_ A[ 2 3]

N8

PCM_ A[ 2 4]

P7

PCM_ A[ 2 5]

T7

PCM_ A[ 2 6]

R7

PCM_ A[ 2 7]

U7

PCM_ A[ 2 8]

U1 - H

A5 - 2 8 9 _ NE W

T1 6

PCM_ D0 0

R1 5

PCM_ D0 1

U1 6

PCM_ D0 2

P14

PCM_ D0 3

N1 4

PCM_ D0 4

R1 4

PCM_ D0 5

N1 3

PCM_ D0 6

R1 3

PCM_ D0 7

M1 3

PCM_ D0 8

T1 5

PCM_ D0 9

P13

PCM_ D1 0

R1 2

PCM_ D1 1

P12

PCM_ D1 2

U1 5

PCM_ D1 3

N1 2

PCM_ D1 4

T1 4

PCM_ D1 5

U1 - G

A5 - 2 8 9 _ NE W

U1 7

PCM_ SDRAM_CLK

R1 7

PCM_ SDRAM_CKE

P16

PCM_ SDRAM_WE

N1 6

PCM_ SDRAM_CS

N1 7

PCM_ SDRAM_CAS

P17

PCM_ SDRAM_RAS

N1 5

PCM_ CS

P15

PCM_ WR

R1 6

PCM_ RD

T1 7

PCM_ SDRAM_CLK_ I N

U1 - F

A5 - 2 8 9 _ NE W

M6

VCC _ MEM

M7

VCC _ MEN

M8

VCC _ MEM

M9

VCC _ MEM

L6

VCC _ MEM

L7

VCC _ MEM

L8

VCC _ MEM

L9

VCC _ MEM

U1 - R

A5 - 2 8 9 _ NE W

ARM_ D[ 0 0 : 3 1 ]

ARM_ D1 6

ARM_ D1 7

ARM_ D1 8

ARM_ D1 9

ARM_ D2 0

ARM_ D2 1

ARM_ D2 2

ARM_ D2 3

ARM_ D2 4

ARM_ D2 5

ARM_ D2 6

ARM_ D2 7

ARM_ D2 8

ARM_ D2 9

ARM_ D3 0

ARM_ D3 1

ARM_ S DR AM_ CL K

ARM_ S DR AM_ DQM1

ARM_ S DR AM_ DQM0

ARM_ S DR AM_ CL K

ARM_ S DR AM_ DQM3

ARM_ S DR AM_ DQM2

+3. 3 VD

ARM_ A[ 0 0 : 1 2 ]

ARM_ A0 0

ARM_ A0 1

ARM_ A0 2

ARM_ A0 3

ARM_ A0 4

ARM_ A0 5

ARM_ A0 6

ARM_ A0 7

ARM_ A0 8

ARM_ A0 9

ARM_ A1 0

ARM_ A1 1

ARM_ A1 2

ARM_ S DR AM_ B0

ARM_ S DR AM_ B1

ARM_ S DR AM_ WE

ARM_ S DR AM_ CAS

ARM_ S DR AM_ RAS

ARM_ S DR AM_ CS

ARM_ S DR AM_ CKE

ARM_ S DR AM_ CKE

ARM_ S DR AM_ CS

ARM_ S DR AM_ RAS

ARM_ S DR AM_ CAS

ARM_ S DR AM_ WE

ARM_ S DR AM_ B1

ARM_ S DR AM_ B0

+3. 3 VD

SPI _ CS/ RX2/ GPI O0[ 1 8]

MI S O / R X 1 / G P I O 0 [ 1 6 ]

SPI _ CLK/ TX2/ GPI O0[ 1 9]

MO S I / T X 1 / G P I O 0 [ 1 7 ]

+3. 3 VD

+3. 3 VD

ARM_ A0 0

ARM_ A0 1

ARM_ A0 2

ARM_ A0 3

ARM_ A0 4

ARM_ A0 5

ARM_ A0 6

ARM_ A0 7

ARM_ A0 8

ARM_ A0 9

ARM_ A1 0

ARM_ A1 1

ARM_ A1 2

ARM_ D1 6

ARM_ D1 7

ARM_ D1 8

ARM_ D1 9

ARM_ D2 0

ARM_ D2 1

ARM_ D2 2

ARM_ D2 3

ARM_ D2 4

ARM_ D2 5

ARM_ D2 6

ARM_ D2 7

ARM_ D2 8

ARM_ D2 9

ARM_ D3 0

ARM_ D3 1

MI S O / R X 1 / G P I O 0 [ 1 6 ]

MO S I / T X 1 / G P I O 0 [ 1 7 ]

SPI _ CS/ RX2/ GPI O0[ 1 8]

SPI _ CLK/ TX2/ GPI O0[ 1 9]

ARM_ S DR AM_ DQM2

ARM_ S DR AM_ DQM3

ARM_ S DR AM_ CL K

ARM_ S DR AM_ DQM1

ARM_ S DR AM_ DQM0

ARM_ S DR AM_ B1

ARM_ S DR AM_ B0

ARM_ S DR AM_ WE

ARM_ S DR AM_ RAS

ARM_ S DR AM_ CAS

ARM_ S DR AM_ CL K

ARM_ S DR AM_ CKE

ARM_ S DR AM_ CS

+3. 3 VD

ARM_ WR/ GP I O3 [ 1 6 ] / BOOT [ 0 ]

ARM_ RD/ GP I O3 [ 1 7 ] / BOOT [ 1 ]

ARM_ CS / GP I O3 [ 1 8 ]

ARM_ WR/ GP I O3 [ 1 6 ] / BOOT [ 0 ]

ARM_ RD/ GP I O3 [ 1 7 ] / BOOT [ 1 ]

+3. 3 VD

PCM_ A[ 0 0: 28 ]

PCM_ D[ 0 0: 15 ]

PCM_ A0 0

PCM_ A0 1

PCM_ A0 2

PCM_ A0 3

PCM_ A0 4

PCM_ A0 5

PCM_ A0 6

PCM_ A0 7

PCM_ A0 8

PCM_ A0 9

PCM_ A1 0

PCM_ A1 1

PCM_ A1 2

PCM_ A1 3

PCM_ A1 4

PCM_ A1 5

PCM_ A1 6

PCM_ A1 7

PCM_ A1 8

PCM_ A1 9

PCM_ A2 0

PCM_ A2 1

PCM_ A2 2

PCM_ A2 3

PCM_ A2 4

PCM_ A2 5

PCM_ D0 0

PCM_ D0 1

PCM_ D0 2

PCM_ D0 3

PCM_ D0 4

PCM_ D0 5

PCM_ D0 6

PCM_ D0 7

PCM_ D0 8

PCM_ D0 9

PCM_ D1 0

PCM_ D1 1

PCM_ D1 2

PCM_ D1 3

PCM_ D1 4

PCM_ D1 5

/RESET

PCM_ CS

PCM_ WR

PCM_ RD

+3. 3 VD

PCM_ D0 0

PCM_ D0 1

PCM_ D0 2

PCM_ D0 3

PCM_ D0 4

PCM_ D0 5

PCM_ D0 6

PCM_ D0 7

PCM_ D0 8

PCM_ D0 9

PCM_ D1 0

PCM_ D1 1

PCM_ D1 2

PCM_ D1 3

PCM_ D1 4

PCM_ D1 5

PCM_ A0 0

PCM_ A0 1

PCM_ A0 2

PCM_ A0 3

PCM_ A0 4

PCM_ A0 5

PCM_ A0 6

PCM_ A0 7

PCM_ A0 8

PCM_ A0 9

PCM_ A1 0

PCM_ A1 1

PCM_ A1 2

PCM_ A1 3

PCM_ A1 4

PCM_ A1 5

PCM_ A1 6

PCM_ A1 7

PCM_ A1 8

PCM_ A1 9

PCM_ A2 0

PCM_ A2 1

PCM_ A2 2

PCM_ A2 3

PCM_ A2 4

PCM_ A2 5

PCM_ SDRAM_CLK

PCM_ SDRAM_CLK

PCM_ CS

PCM_ WR

PCM_ RD

+3. 3 VD

+3. 3 VD

FLASF_ RY/ BY

+3. 3 VD

ARM_ D1 5

ARM_ D1 4

ARM_ D1 3

ARM_ D1 2

ARM_ D1 1

ARM_ D1 0

ARM_ D0 9

ARM_ D0 8

ARM_ D0 7

ARM_ D0 6

ARM_ D0 5

ARM_ D0 4

ARM_ D0 3

ARM_ D0 2

ARM_ D0 1

ARM_ D0 0

ARM_ D1 5

ARM_ D1 4

ARM_ D1 3

ARM_ D1 2

ARM_ D1 1

ARM_ D1 0

ARM_ D0 9

ARM_ D0 8

ARM_ D0 7

ARM_ D0 6

ARM_ D0 5

ARM_ D0 4

ARM_ D0 3

ARM_ D0 2

ARM_ D0 1

ARM_ D0 0

ARM_ A1 0

ARM_ A1 2

ARM_ A1 1

ARM_ A0 9

ARM_ A0 8

ARM_ A0 7

ARM_ A0 6

ARM_ A0 5

ARM_ A0 4

ARM_ A0 3

ARM_ A0 2

ARM_ A0 1

ARM_ A0 0

SDRAM (U21, U22) data/address/control line to the A5 chip

Try to get the line of isometric, are not more than 3 cm

A5 G3, J5 two feet, can not be connected to the nearest

To ensure both into two pieces of SDRAM 38 feet line of equal length

FLASH (U20) to the A5 attachment length difference can be relaxed

But the difference to control under 10 cm

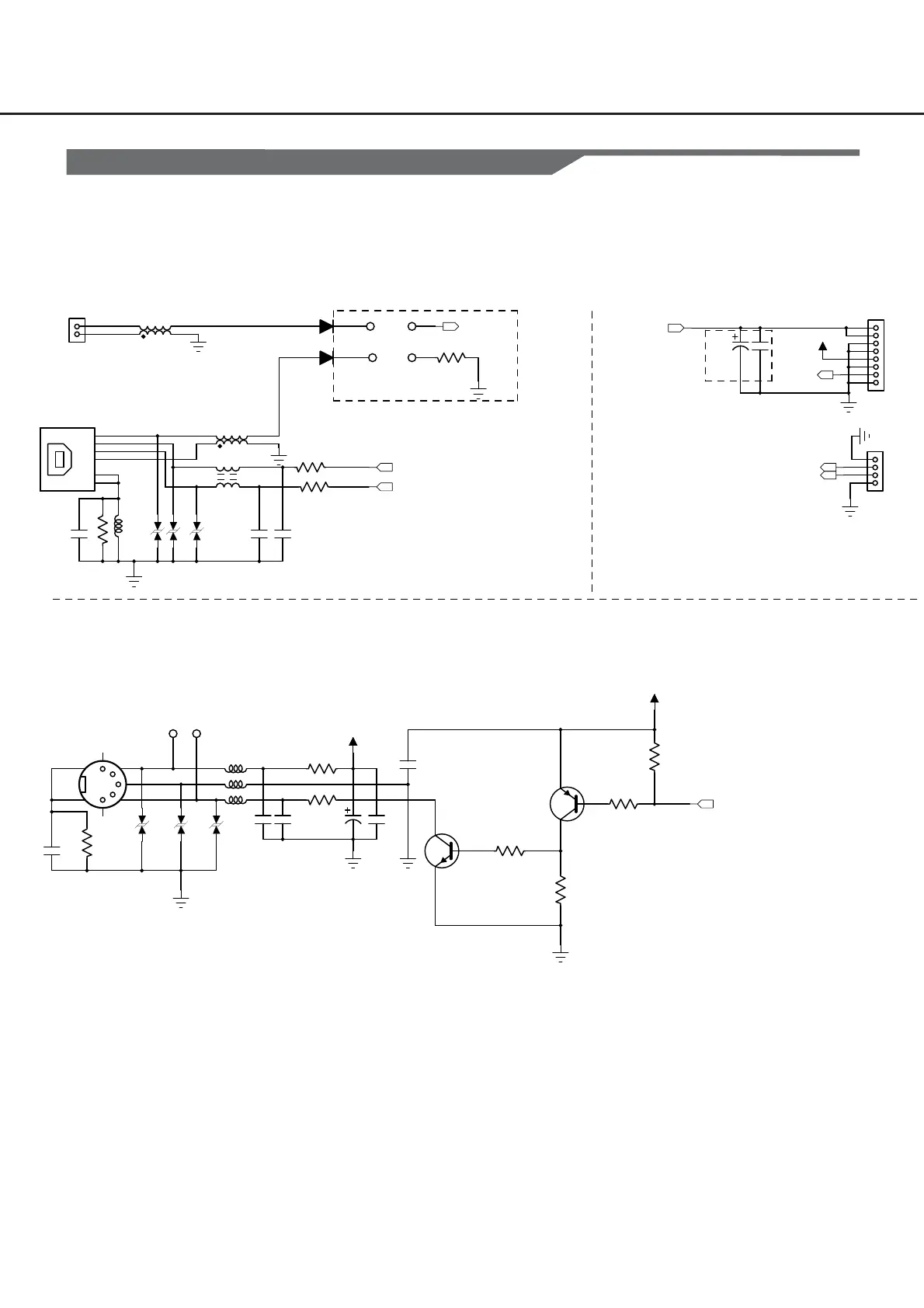

10

IO Board Schematic

2 - ALL CAPACITANCE VALUES ARE INDICATED IN "F". ( U = 0.000001F; P = 0.000001UF. )

1 - ALL RESISTANCE VALUES ARE INDICATED IN "ohm". (K = 1,000ohm; M = 1,000,000ohm. )

REMARK :

POWER & USB

BAT+

BAT-

MIDI_OUT

From Main BOARD

FROM IO BOARD

Connect to Switch Board

R2

27R

R3

27R

1

VBUS

2

D-

3

D+

4

GND

5

SH1

6

SH2

J2

USB

L4

D3

5V/0.15PF

D5

5V/0.15PF

D4

5V/0.15PF

C2

DNS

C4

DNS

C3

DNS

R4

DNS

3

4

1 2

L2

TC623-30uH

L3

DLW21HN121SQ2

1

2

JK1

R6

68R

R7

68R

L5

L7

L6

T1

T2

C5

104

1

2

3

4

5

6

7

J4

MS-CON-MIDI_JACK

MIDI_OUT

D6

5V/0.15PF

D7

5V/0.15PF

D8

5V/0.15PF

C9

104

C8

100U/16V

C7

DNS

C6

DNS

C10

DNS

R9

DNS

3

4

1 2

L1

TC623-30uH

B

E

C

Q2

8050

B

E

C

Q1

8550

R10

10K

R11

4.7K

R8

4.7K

R5

10K

1

2

3

4

5

6

7

8

J1

1

2

3

4

J3

To MB J2

PWR_VBUS OFF

PWR_BAT COMMON

R1

47R

C1

1000uf/16V

C11

104/50V

D1

1N4001

D2

SS24

VDD_3.3V

VDD_3.3V

MIDI_OUT

D-

D+

PWR_VBS

MIDI_OUT

D-

D+

GND

PWR_VBS

GND

GND

VDD_3.3V

Loading...

Loading...