Overview

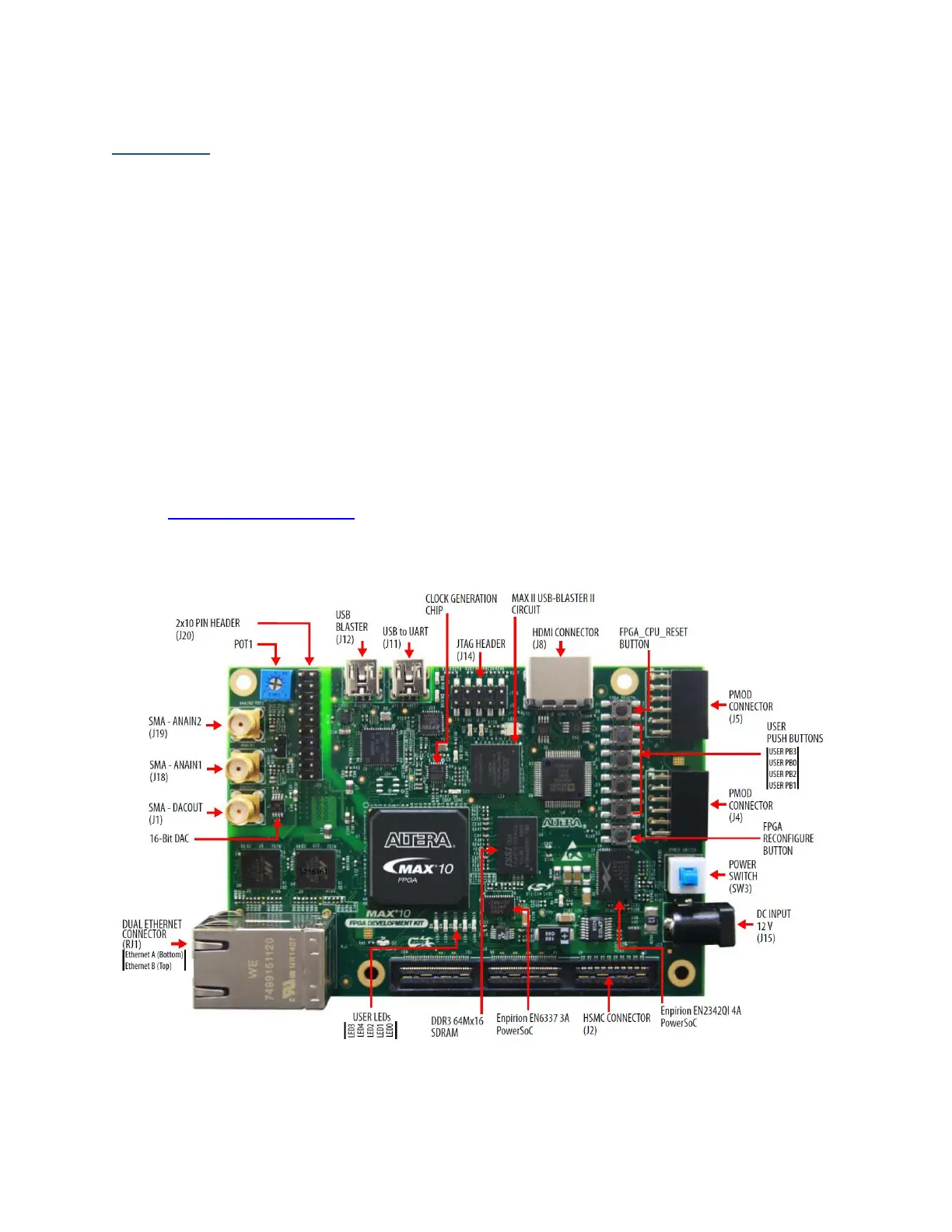

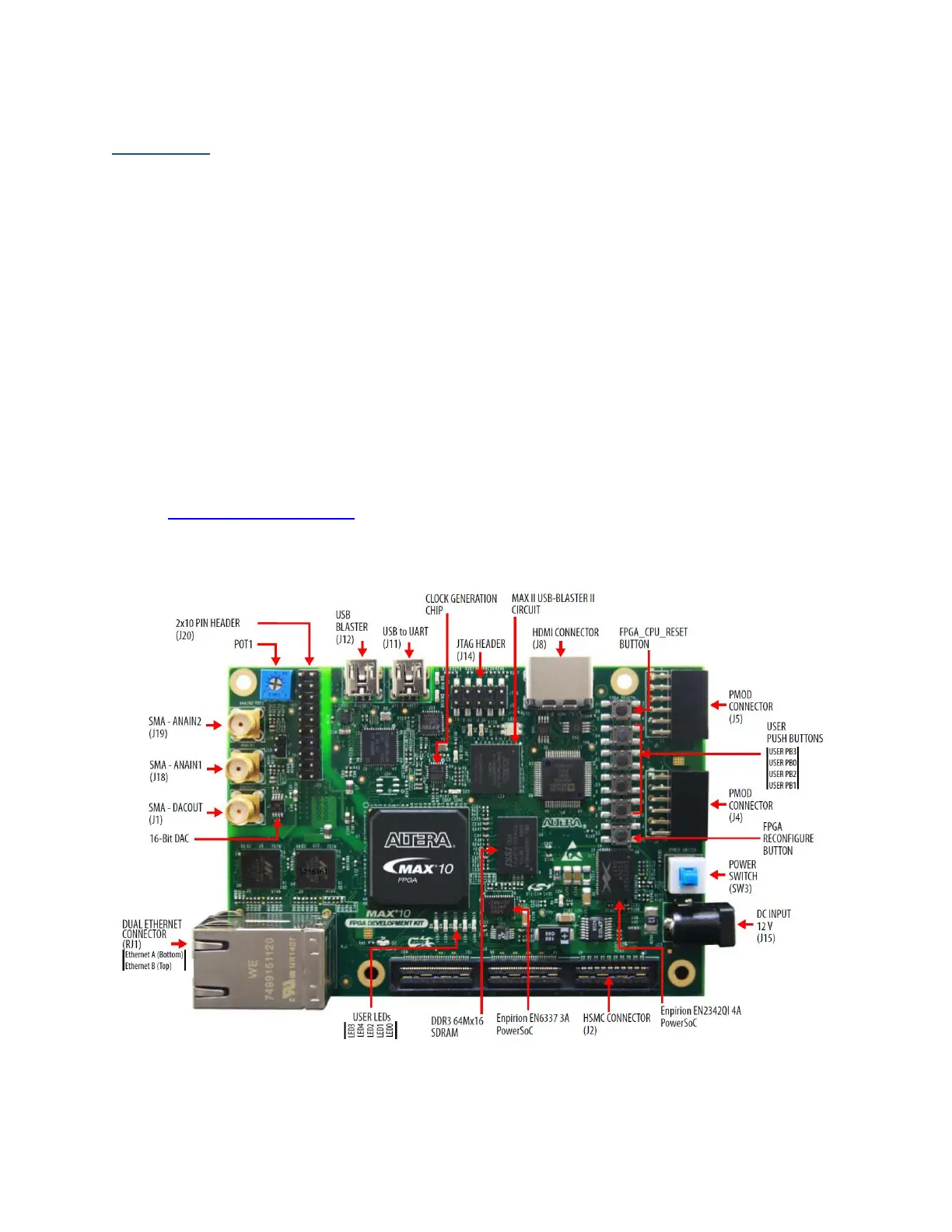

This example design is a web-server based board update portal (BUP) design which contains

a Nios® II processor, a Triple Speed Ethernet media access control (MAC) MegaCore® and a

DDR3 MegaCore®. It allows you to remotely update a FPGA system over Ethernet, for an

example, it can be used to update the firmware of an embedded FPGA system. The design is

based on Ethernet A port on MAX 10 FPGA development kit, please download and install the

BTS installer for more details about BUP design.

The following external parts are needed to demonstrate the design example:

1. MAX10 10M50DA FPGA Development kit

2. Mini-USB cable for programming MAX 10 device

3. Quartus v15.0 or later

Recompile the design example

Recompile the software build

Use NIOS command shell to download SOF and ELF file and get IP address info

Quartus v15.0.0/145 or later is required for this design example. Please refer to the

Altera Download Center for information on updates

4. IMPORTANT: only use the 12V, 2A AC adapter that came with this kit. Do not use

other power supplies from other Altera kits

Figure 1: Max10 FPGA Development Kit

Loading...

Loading...