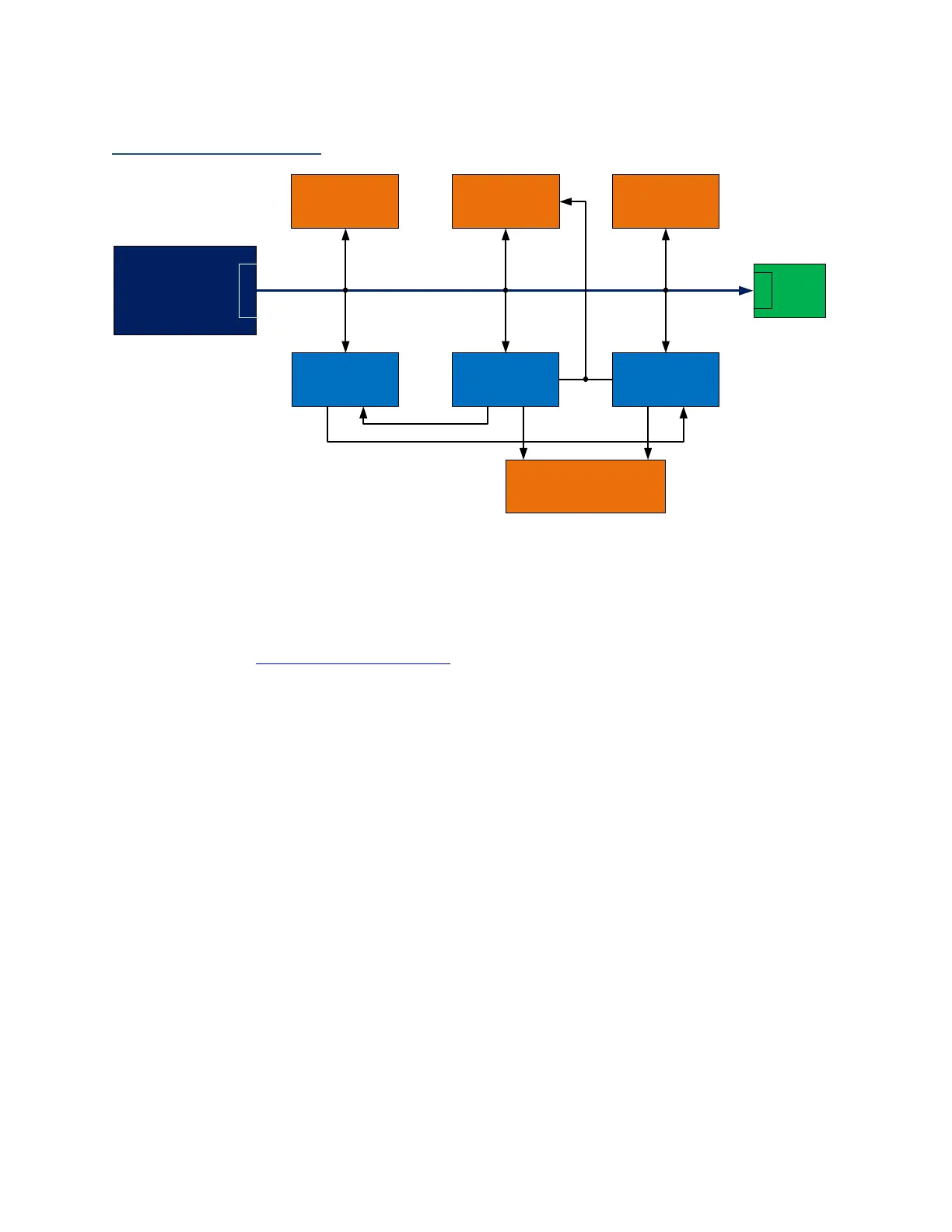

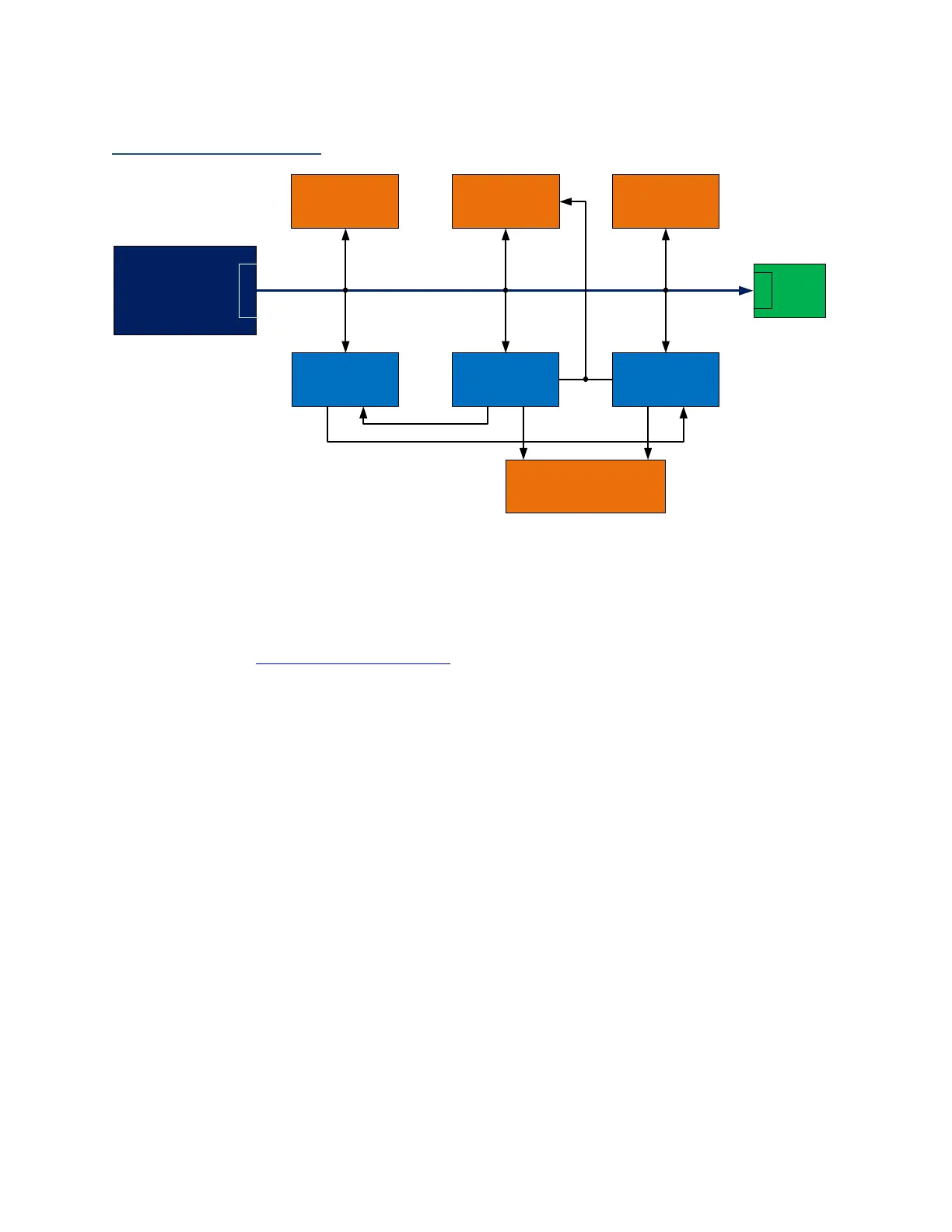

Theory of Operation

Nios® II Core

AVMM

Master

UART

AVMM

Master

QSPI Flash DDR3 SDRAM

On-Chip Memory

(Optional)

Ethernet Core SGDMA TX SGDMA RX

On-Chip

Description Memory

Figure 2: BUP design example block diagram

The Nios® II processor is used to implement a web server in MAX 10 FPGA device. Please

see application note AN429: Remote Configuration Over Ethernet with the Nios® II Processor

(PDF) to learn more about remote update. Also, more information about Embedded Peripheral

IP can be found at IP Peripheral User Guide.

Loading...

Loading...