ADE9000 Technical Reference Manual UG-1098

Rev. 0 | Page 35 of 86

During a SPI read operation, the LAST_DATA_16 and

LAST_DATA_32 registers are updated within two master clocks

after the CMD_HDR has been received. If a command to read

the LAST_CMD, LAST_DATA_16, or LAST_DATA_32 registers

is received, these three registers are not updated.

Note that the LAST_DATA_16 and LAST_DATA_32 registers

are not updated after a SPI burst read operation; these are the

cases in Table 20 where next address is written.

On a write operation, LAST_DATA_16 and LAST_DATA_32

are not updated until all 16 bits or 32 bits of the write data have

been received. Note that on a write register operation, the

addressed register is not written until all 16 bits or 32 bits are

received, depending on the length of the register.

Note that when the LAST_CMD, LAST_DATA_16, and LAST_

DATA_32 registers are read, their values remain unchanged.

CRC OF CONFIGURATION REGISTERS

The configuration register CRC feature in the ADE9000 monitors

many register values. It also optionally includes 15 registers that

are individually selectable in the CRC_OPTEN register.

This feature runs as a background task; it takes 10.8 ms to

calculate the configuration register CRC. The result is stored in

the CRC_RSLT register. If any of the monitored registers change

value, the CRC_RSLT changes as well, and the CRC_CHG bit in

the STATUS 1 register is set; this can also be configured to

generate an interrupt on

IRQ1

.

After configuring the ADE9000 and writing the required registers

to calibrate the measurements (such as xIGAIN or xVGAIN, for

example), the configuration register CRC calculation can be

started by writing the FORCE_CRC_UPDATE bit in the

CRC_FORCE register. When the calculation is complete, the

CRC_DONE bit is set in the STATUS1 register.

The method used for calculating the configuration register

CRC is also based on the CRC-16-CCITT algorithm. The most

significant byte of each register is introduced into the LFSR first,

without bit reversal.

The order in which the registers are calculated is given in Table 21,

with the lowest register introduced first. Note that 32-byte registers

have four bytes introduced into the LFSR, and 16-byte registers

have two bytes introduced into the LFSR.

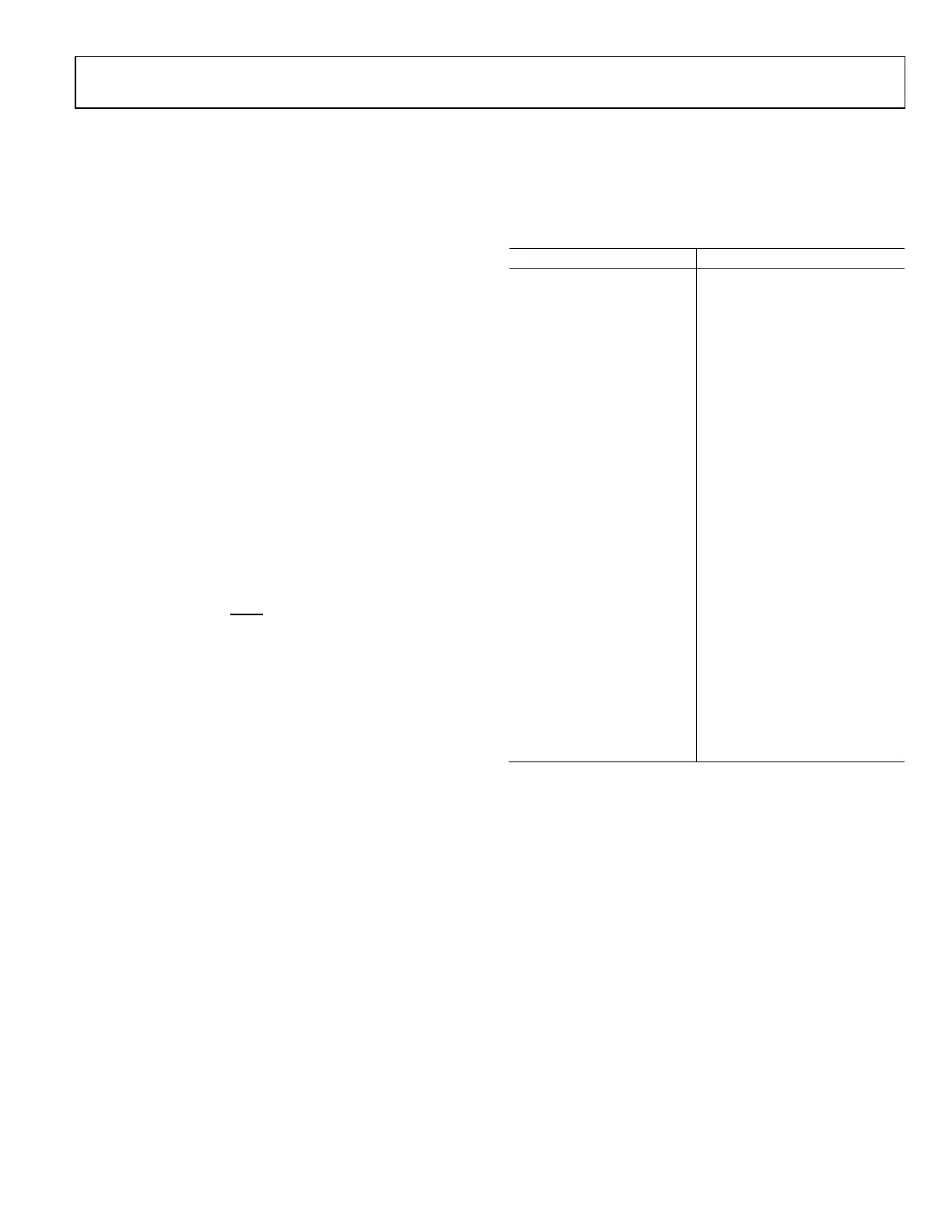

Table 21. Order of Registers Included in Configuration

Register CRC

Register Addresses Register Length (Bits)

0x21 to 0x38 32

0x41 to 0x58 32

0x60 to 0x73 32

0x409 32

0x420 to 0x422 32

0x424 32

0x470 to 0x475 32

0x480 to 0x481 16

0x490 to 0x497 16

0x499 16

0x4AF to 0x4B2 16

0x425 32

0x4B8 to 0x4B9 16

0x47D 32

0x478 to 0x479 32

0x4EF 16

0x4BA 16

0x47E 32

0x00 32

0x20 32

0x4B6 16

0x4BF 16

0x4B5 16

Loading...

Loading...