ADE9000 Technical Reference Manual UG-1098

Rev. 0 | Page 65 of 86

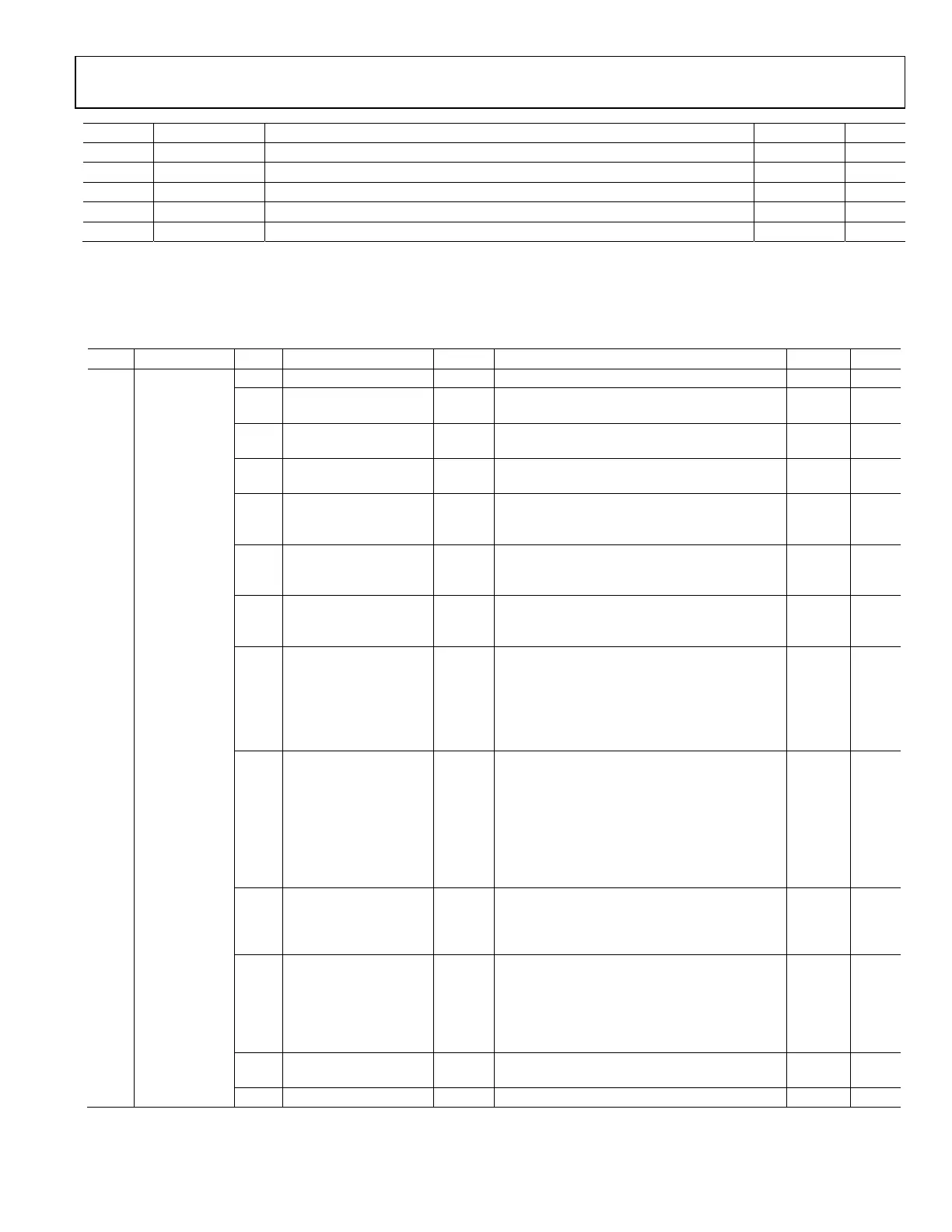

Address Name Description Reset Access

0x6B8 CVRMS1012_2 SPI burst read accessible. Registers organized by phase. See CVRMS1012. 0x00000000 R/W

0x6B9 NI_PCF_2 SPI burst read accessible. Registers organized by phase. See NI_PCF. 0x00000000 R/W

0x6BA NIRMS_2 SPI burst read accessible. Registers organized by phase. See NIRMS. 0x00000000 R/W

0x6BB NIRMSONE_2 SPI burst read accessible. Registers organized by phase. See NIRMSONE. 0x00000000 R/W

0x6BC NIRMS1012_2 SPI burst read accessible. Registers organized by phase. See NIRMS1012. 0x00000000 R/W

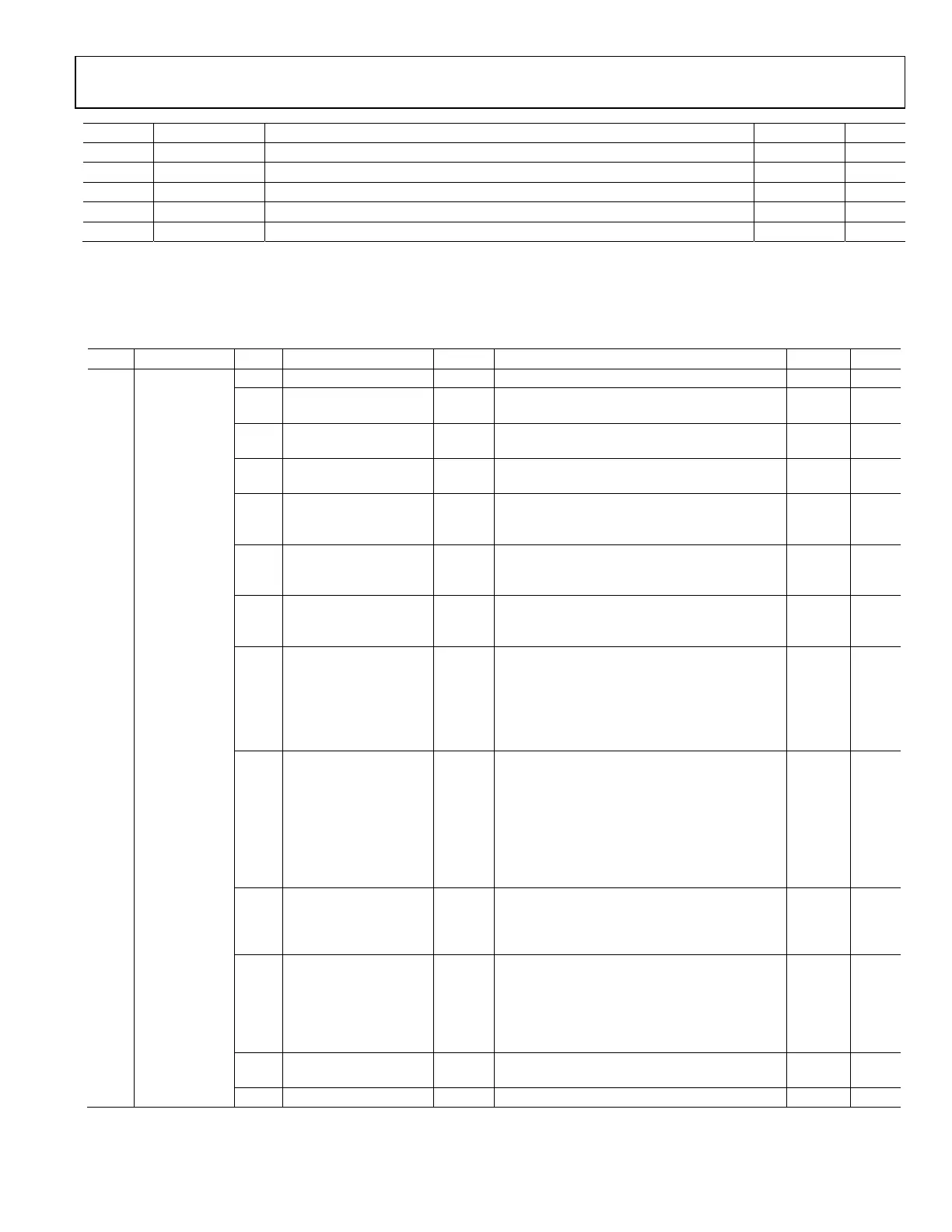

REGISTER DETAILS

Table 31 details the registers of the ADE9000 that have bit fields. Additional registers listed in Table 30 do not have bit fields.

Table 31. Register Details

Addr. Name Bits Bit Name Settings Description Reset Access

0x060 CONFIG0 [31:14] RESERVED Reserved. 0x0 R

13 DISRPLPF

Set this bit to disable the low-pass filter in the

total reactive power datapath.

0x0 R/W

12 DISAPLPF

Set this bit to disable the low-pass filter in the

total active power datapath.

0x0 R/W

11 ININTEN

Set this bit to enable the digital integrator in the

neutral current channel.

0x0 R/W

10 VNOMC_EN

Set this bit to use the nominal phase voltage

rms, V

NOM

, in the computation of Phase C total

apparent power, CVA.

0x0 R/W

9 VNOMB_EN

Set this bit to use the nominal phase voltage

rms, V

NOM

, in the computation of Phase B total

apparent power, BVA.

0x0 R/W

8 VNOMA_EN

Set this bit to use the nominal phase voltage

rms, V

NOM

, in the computation of Phase A total

apparent power, AVA.

0x0 R/W

7 RMS_SRC_SEL

This bit selects which samples are used for the

RMS½ and 10 cycle rms/12 cycle rms calculation.

0x0 R/W

0

xI_PCF waveforms, after the high-pass filter and

integrator.

1

ADC samples, before the high-pass filter and

integrator.

6 ZX_SRC_SEL

This bit selects whether data going into the zero-

crossing detection circuit comes before the

high-pass filter, integrator, and phase

compensation or afterwards.

0x0 R/W

0

After the high-pass filter, integrator, and phase

compensation.

1

Before the high-pass filter, integrator, and phase

compensation.

5 INTEN

Set this bit to enable the integrators in the phase

current channels. The neutral current channel

integrator is managed by the ININTEN bit in the

CONFIG0 register.

0x0 R/W

4 MTEN

Set this bit to enable multipoint phase and gain

compensation. If enabled, an additional gain

factor, xIGAIN0 through xIGAIN5, is applied to

the current channel based on the xIRMS current

rms amplitude and the MTTHR_Lx and

MTTHR_Hx register values.

0x0 R/W

3 HPFDIS

Set this bit to disable high-pass filters in all the

voltage and current channels.

0x0 R/W

2 RESERVED Reserved. 0x0 R

Loading...

Loading...