UG-1098 ADE9000 Technical Reference Manual

Rev. 0 | Page 60 of 86

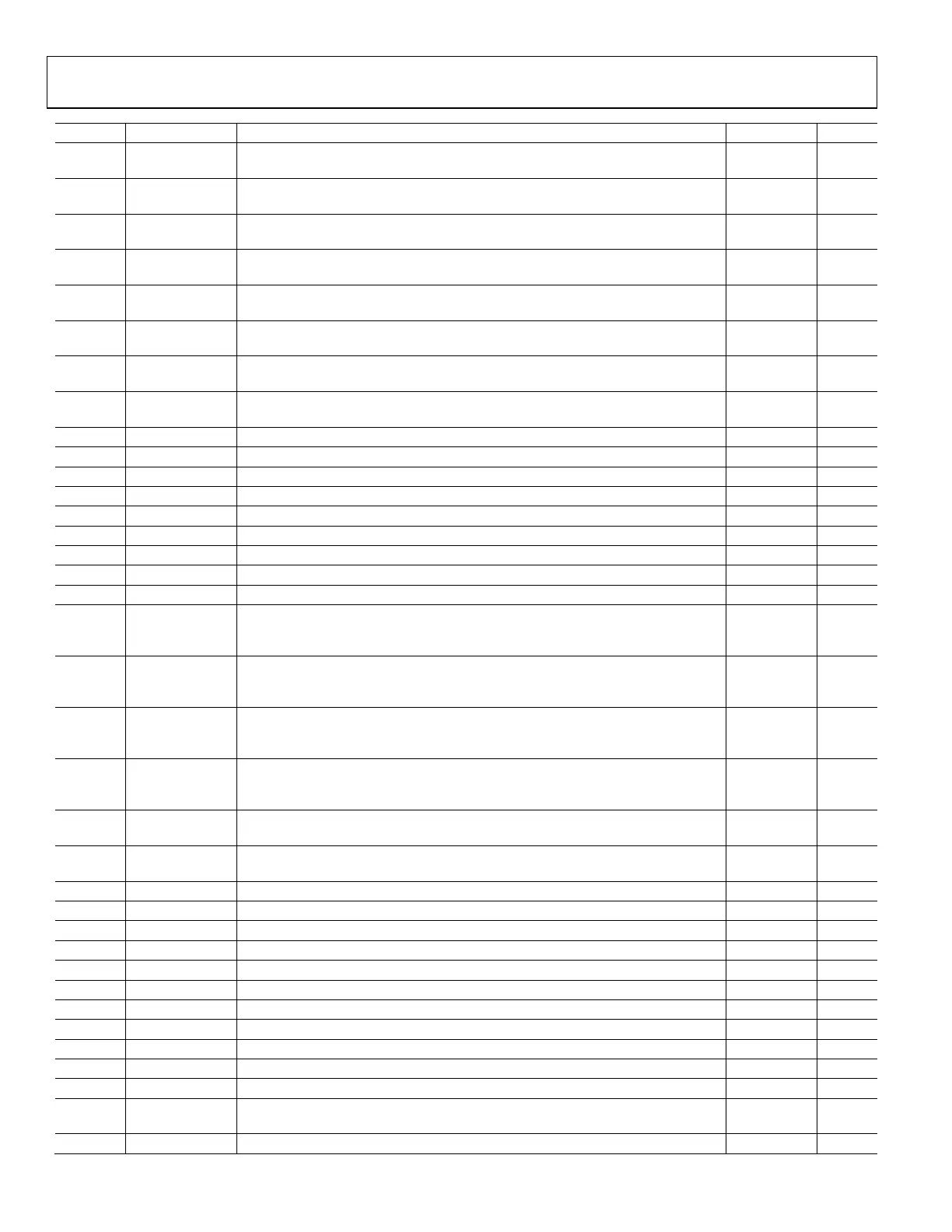

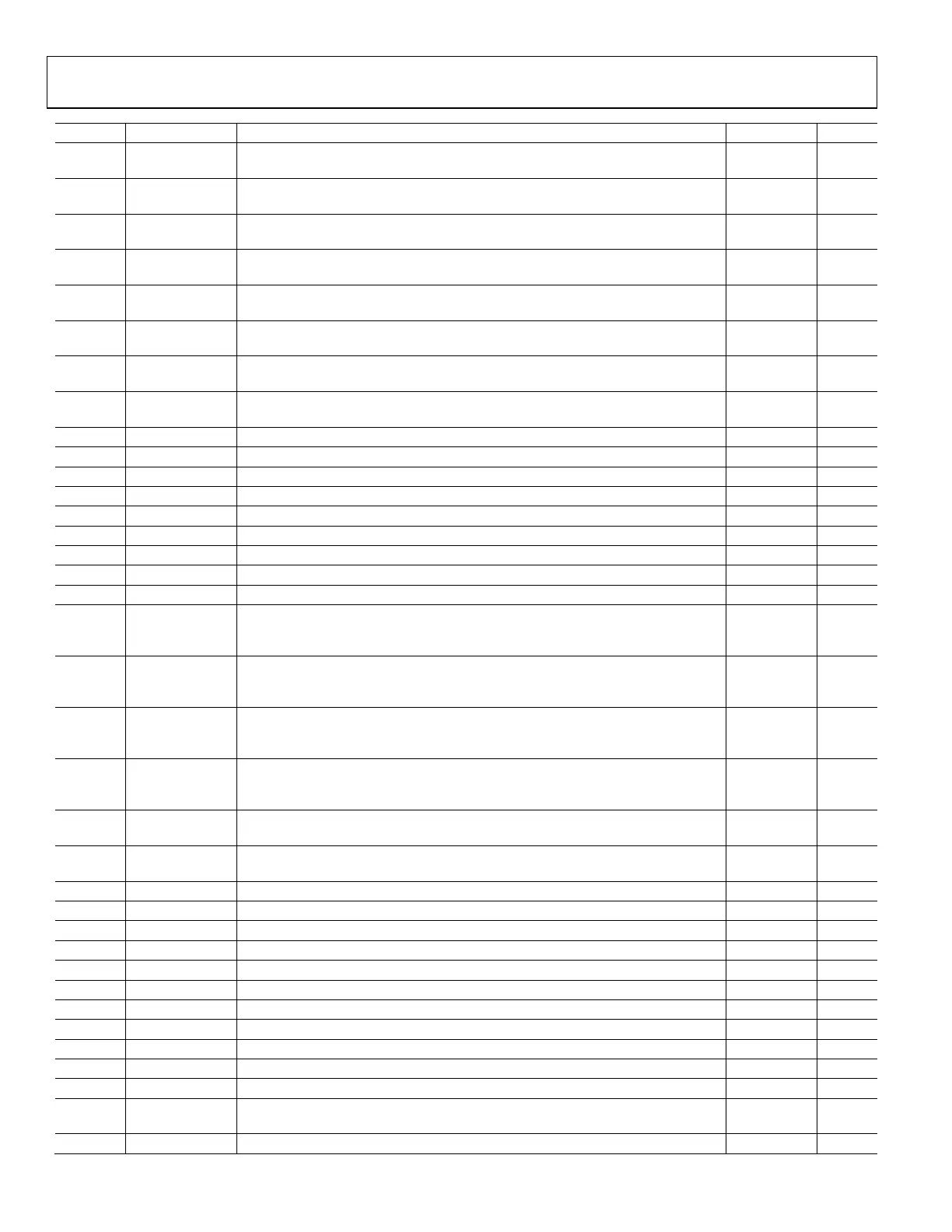

Address Name Description Reset Access

Phase C accumulated fundamental reactive energy, MSB. Updated according to

the settings in the EP_CFG and EGY_TIME registers.

0x38F CFVA_ACC Phase C accumulated fundamental apparent power, updated after PWR_TIME

8 kSPS samples.

0x00000000 R

0x390 CFVAHR_LO Phase C accumulated fundamental apparent energy, LSB. Updated according to

the settings in the EP_CFG and EGY_TIME registers.

0x00000000 R

0x391 CFVAHR_HI Phase C accumulated fundamental apparent energy, MSB. Updated according to

the settings in the EP_CFG and EGY_TIME registers.

0x00000000 R

0x397 PWAT T_ACC Accumulated positive total active power, MSB, from AWATT, BWATT, and CWATT

registers, updated after PWR_TIME 8 kSPS samples.

0x00000000 R

0x39B NWAT T_ACC

Accumulated Negative total active power, MSB, from AWATT, BWATT, and CWATT

registers, updated after PWR_TIME 8 kSPS samples.

0x00000000 R

0x39F PVAR_ACC Accumulated positive total reactive power, MSB, from AVAR, BVAR, and CVAR

registers, updated after PWR_TIME 8 kSPS samples.

0x00000000 R

Accumulated Negative total reactive power, MSB, from AVAR, BVAR, and CVAR

registers, updated after PWR_TIME 8 kSPS samples.

0x400 IPEAK Current peak register. 0x00000000 R

0x401 VPEAK Voltage peak register. 0x00000000 R

0x402 STATUS0 Status Register 0. 0x00000000 R/W

0x403 STATUS1 Status Register 1. 0x00000000 R/W

0x404 EVENT_STATUS Event status register. 0x00000000 R

0x405 MASK0 Interrupt Enable Register 0. 0x00000000 R/W

Interrupt Enable Register 1.

0x407 EVENT_MASK Event enable register. 0x00000000 R/W

0x409 OILVL Over current detection threshold level. 0x00FFFFFF R/W

Phase A overcurrent RMS½ value. If a phase is enabled, with the OC_ENA bit set

in the CONFIG3 register and AIRMSONE greater than the OILVL threshold, this

value is updated.

Phase B overcurrent RMS½ value. If a phase is enabled, with the OC_ENB bit set

in the CONFIG3 register and BIRMSONE greater than the OILVL threshold, this

value is updated.

Phase C overcurrent RMS½ value. If a phase is enabled, with the OC_ENC bit set

in the CONFIG3 register and CIRMSONE greater than the OILVL threshold, this

value is updated.

0x40D OIN Neutral current overcurrent RMS½ value. If enabled, with the OC_ENN bit set in

the CONFIG3 register and NIRMSONE greater than the OILVL threshold, this value

is updated.

0x00000000 R

0x40E USER_PERIOD User configured line period value used for resampling, fast RMS½ and 10 cycle rms/

12 cycle rms when the UPERIOD_SEL bit in the CONFIG2 register is set.

0x00500000 R/W

0x40F VLEVEL Register used in the algorithm that computes the fundamental active, reactive,

and apparent powers as well as the fundamental IRMS and VRMS values.

0x00045D45 R/W

Voltage RMS½ dip detection threshold level.

0x411 DIPA Phase A voltage RMS½ value during a dip condition. 0x007FFFFF R

0x412 DIPB Phase B voltage RMS½ value during a dip condition. 0x007FFFFF R

0x413 DIPC Phase C voltage RMS½ value during a dip condition. 0x007FFFFF R

0x414 SWELL_LVL Voltage RMS½ swell detection threshold level. 0x00FFFFFF R/W

0x415 SWELLA Phase A voltage RMS½ value during a swell condition. 0x00000000 R

0x416 SWELLB Phase B voltage RMS½ value during a swell condition. 0x00000000 R

0x417 SWELLC Phase C voltage RMS½ value during a swell condition. 0x00000000 R

0x418 APERIOD Line period on Phase A voltage. 0x00A00000 R

Line period on Phase B voltage.

0x41A CPERIOD Line period on Phase C voltage. 0x00A00000 R

0x41B COM_PERIOD Line period measurement on combined signal from Phase A, Phase B, and

Phase C voltages.

0x00A00000 R

0x41C ACT_NL_LVL No load threshold in the total and fundamental active power datapath. 0x0000FFFF R/W

Loading...

Loading...