ADE9000 Technical Reference Manual UG-1098

Rev. 0 | Page 81 of 86

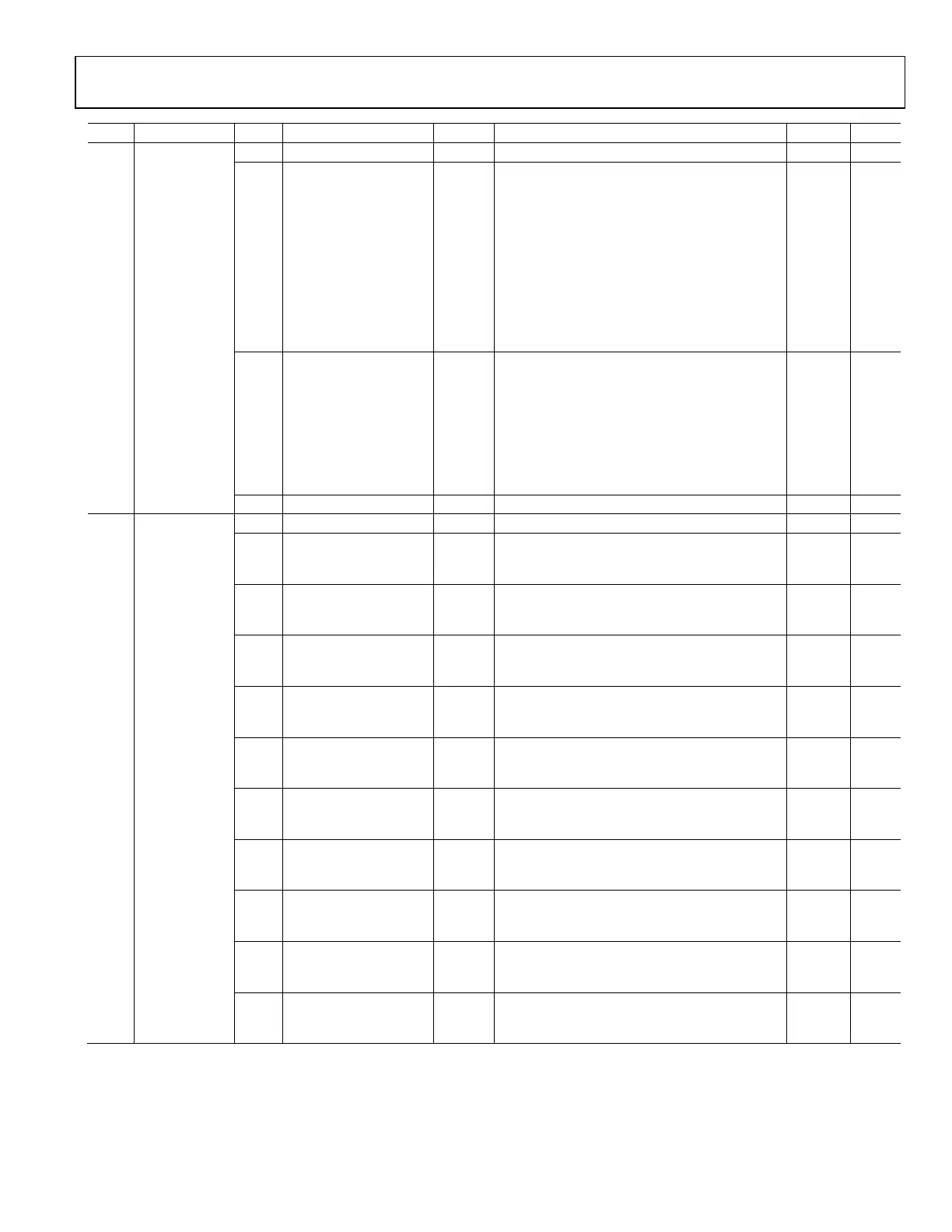

Addr. Name Bits Bit Name Settings Description Reset Access

0x49A ZX_LP_SEL [15:5] RESERVED Reserved. 0x0 R

[4:3] LP_SEL Selects line period measurement used for

VRMS½ cycle, 10 cycle rms/12 cycle rms, and

resampling.

0x3 R/W

00 APERIOD, line period measurement from Phase A

voltage.

01

BPERIOD, line period measurement from Phase B

voltage.

10 CPERIOD, line period measurement from Phase C

voltage.

11 COM_PERIOD, line period measurement on

combined signal from VA, VB, and VC.

[2:1] ZX_SEL Selects the zero-crossing signal, which can be

routed to the CF3/ZX output pin and used for

line cycle energy accumulation.

0x3 R/W

00 ZXVA, Phase A voltage zero-crossing signal.

01 ZXVB, Phase B voltage zero-crossing signal.

10 ZXVC, Phase C voltage zero-crossing signal.

11 ZXCOMB, zero-crossing on combined signal

from VA, VB, and VC.

0 RESERVED Reserved. 0x0 R

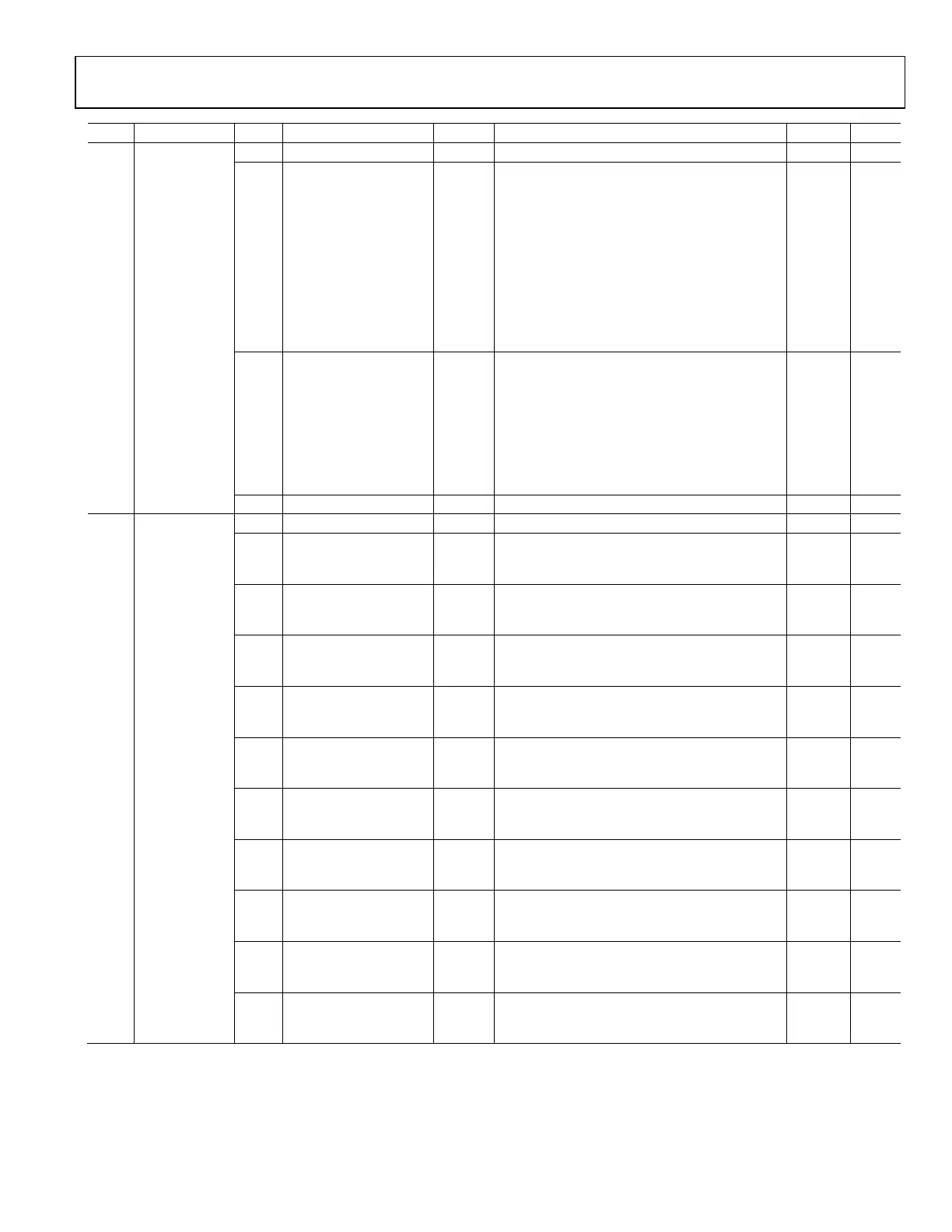

0x49D PHSIGN [15:10] RESERVED Reserved. 0x0 R

9 SUM4SIGN Sign of the sum of the powers included in the

CF4 datapath. The CF4 energy is positive if this

bit is clear and negative if this bit is set.

0x0 R

8 SUM3SIGN Sign of the sum of the powers included in the

CF3 datapath. The CF3 energy is positive if this

bit is clear and negative if this bit is set.

0x0 R

7 SUM2SIGN Sign of the sum of the powers included in the

CF2 datapath. The CF2 energy is positive if this

bit is clear and negative if this bit is set.

0x0 R

6 SUM1SIGN Sign of the sum of the powers included in the

CF1 datapath. The CF1 energy is positive if this

bit is clear and negative if this bit is set.

0x0 R

5 CVARSIGN Phase C reactive power sign bit. The PWR_SIGN_

SEL bit in the EP_CFG selects whether this feature

monitors total or fundamental reactive power.

0x0 R

4 CWSIGN Phase C active power sign bit. The PWR_SIGN_SEL

bit in the EP_CFG selects whether this feature

monitors total or fundamental active power.

0x0 R

3 BVARSIGN Phase B reactive power sign bit. The PWR_SIGN_

SEL bit in the EP_CFG selects whether this feature

monitors total or fundamental reactive power.

0x0 R

2 BWSIGN Phase B active power sign bit. The PWR_SIGN_SEL

bit in the EP_CFG selects whether this feature

monitors total or fundamental active power.

0x0 R

1 AVARSIGN Phase A reactive power sign bit. The PWR_SIGN_

SEL bit in the EP_CFG selects whether this feature

monitors total or fundamental reactive power.

0x0 R

Phase A active power sign bit. The PWR_SIGN_SEL

bit in the EP_CFG selects whether this feature

monitors total or fundamental active power.

Loading...

Loading...