UG-1098 ADE9000 Technical Reference Manual

Rev. 0 | Page 80 of 86

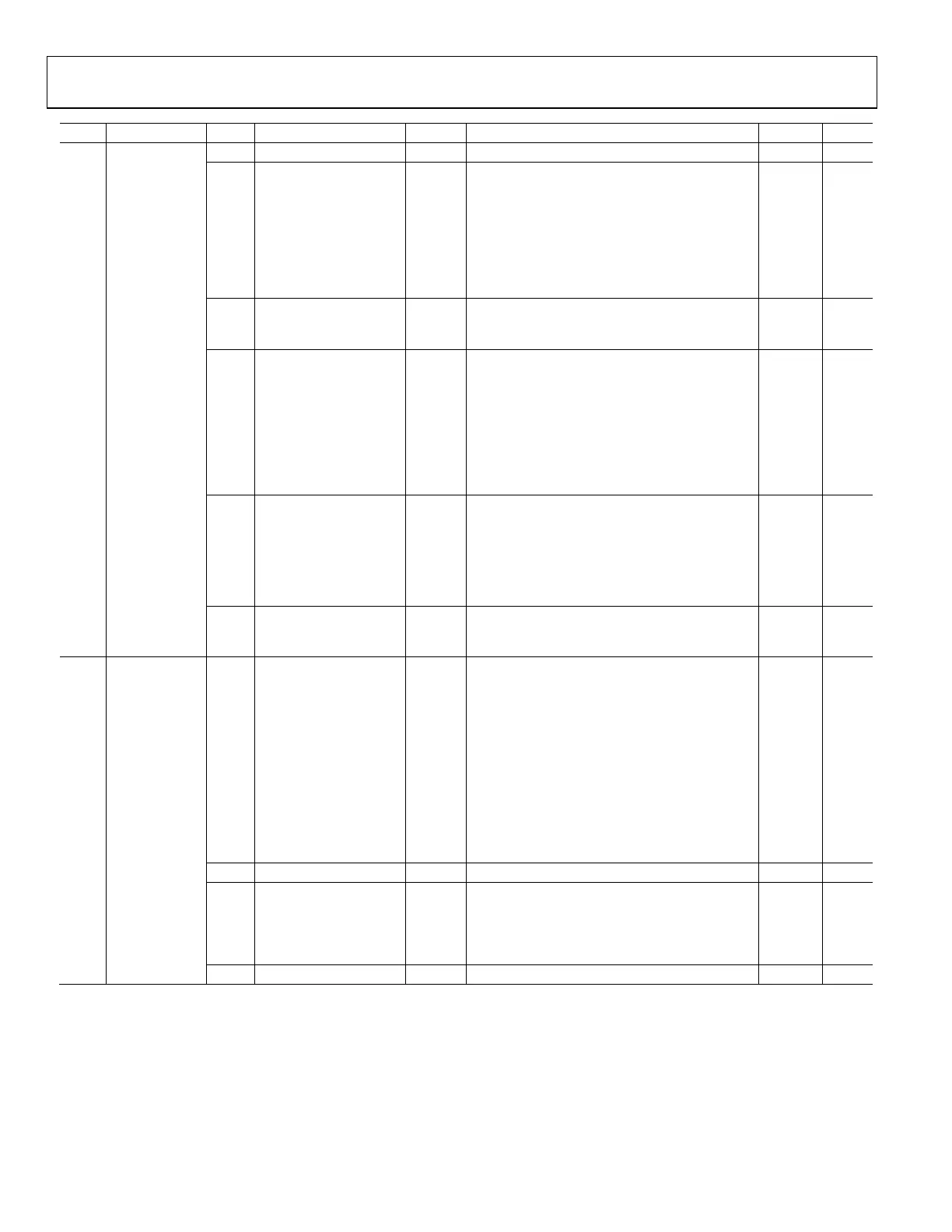

Addr. Name Bits Bit Name Settings Description Reset Access

0x492 ACCMODE [15:9] RESERVED Reserved. 0x0 R

8 SELFREQ Use this bit to configure the IC for a 50 Hz or

60 Hz system. This setting is used in the

fundamental power measurements and to set the

default line period used for VRMS½, 10 cycle rms/

12 cycle rms and resampling calculations if a

zero-crossing is not present.

0x0 R/W

0 50 Hz.

1 60 Hz.

7 ICONSEL Set this bit to calculate the current flowing

through IB from the IA and IC measurements. If

this bit is set, IB = −IA − IC.

0x0 R/W

[6:4] VCONSEL 3-wire and 4-wire hardware configuration

selection.

0x0 R/W

000 4-wire wye.

001 3-wire delta. VB' = VA − VC.

010 4-wire wye, nonBlondel compliant. VB' = −VA − VC.

011 4-wire delta, nonBlondel compliant. VB' = −VA.

100 3-wire delta. VA' = VA − VB; VB' = VA − VC; VC' =

VC − VB.

[3:2] VARACC Total and fundamental reactive power accumula-

tion mode for energy registers and CFx pulses.

0x0 R/W

00 Signed accumulation mode.

01 Absolute value accumulation mode.

Positive accumulation mode.

11 Negative accumulation mode.

[1:0] WAT TACC Total and fundamental active power accumulation

mode for energy registers and CFx pulses. See

VARACC.

0x0 R/W

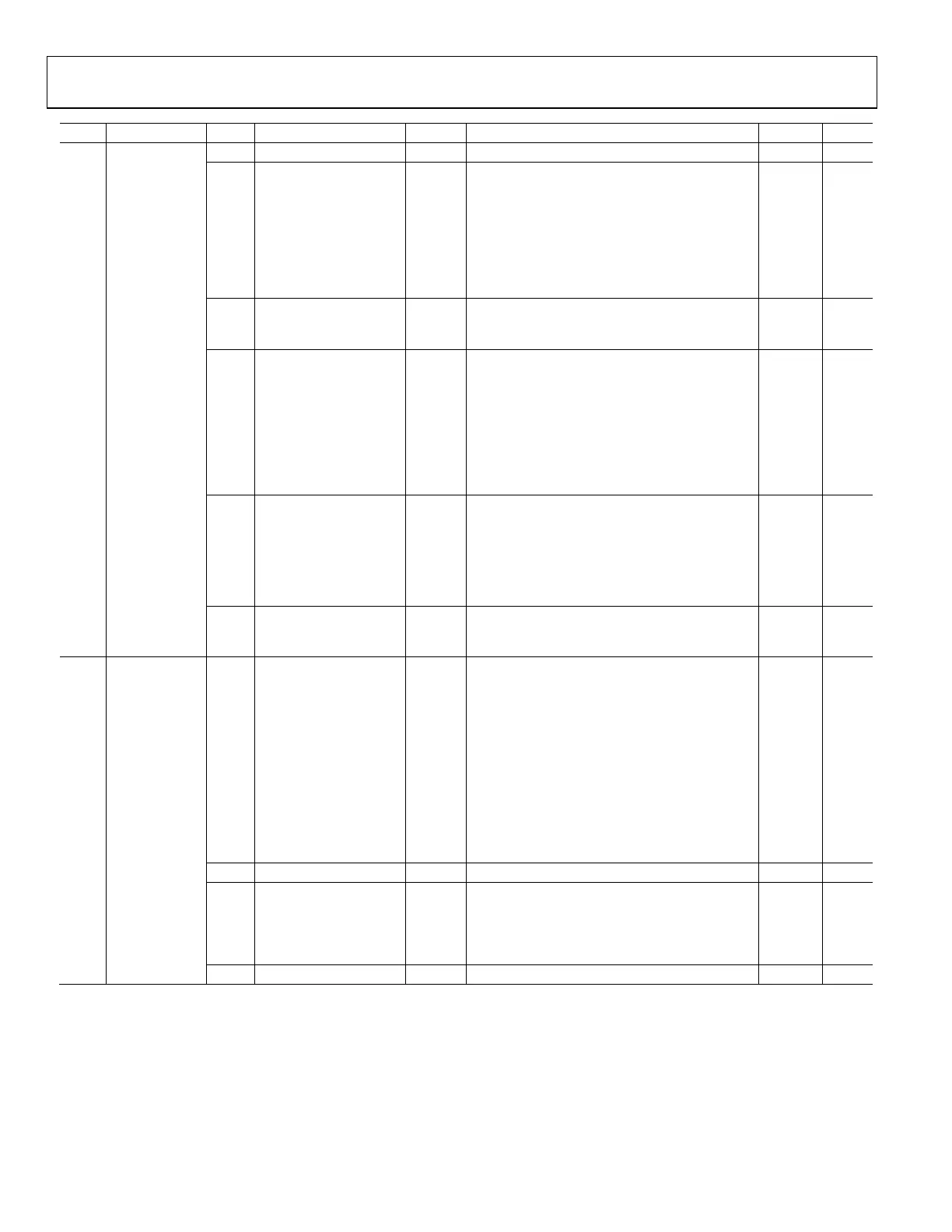

0x493 CONFIG3 [15:12] OC_EN Overcurrent detection enable. OC_EN[3:0] bits

can all be set to 1 simultaneously to allow

overcurrent detection on all three phases and/or

neutral simultaneously.

0xF R/W

Bit 12. When OC_EN[3] is set to 1, Phase A is

selected for the overcurrent detection.

Bit 13. When OC_EN[2] is set to 1, Phase B is

selected for the overcurrent detection.

Bit 14. When OC_EN[1] is set to 1, Phase C is

selected for the overcurrent detection.

Bit 15. When OC_EN[0] is set to 1, the neutral line

is selected for the overcurrent detection.

[4:2] PEAKSEL Set this bit to select which phase(s) to monitor

peak voltages and currents on. Write 1 to PEAKSEL,

Bit 0 to enable Phase A peak detection. Similarly,

PEAKSEL, Bit 1 enables Phase B peak detection, and

PEAKSEL, Bit 2 enables Phase C peak detection.

0x0 R/W

[1:0] RESERVED Reserved. 0x0 R

Loading...

Loading...