ADE9000 Technical Reference Manual UG-1098

Rev. 0 | Page 85 of 86

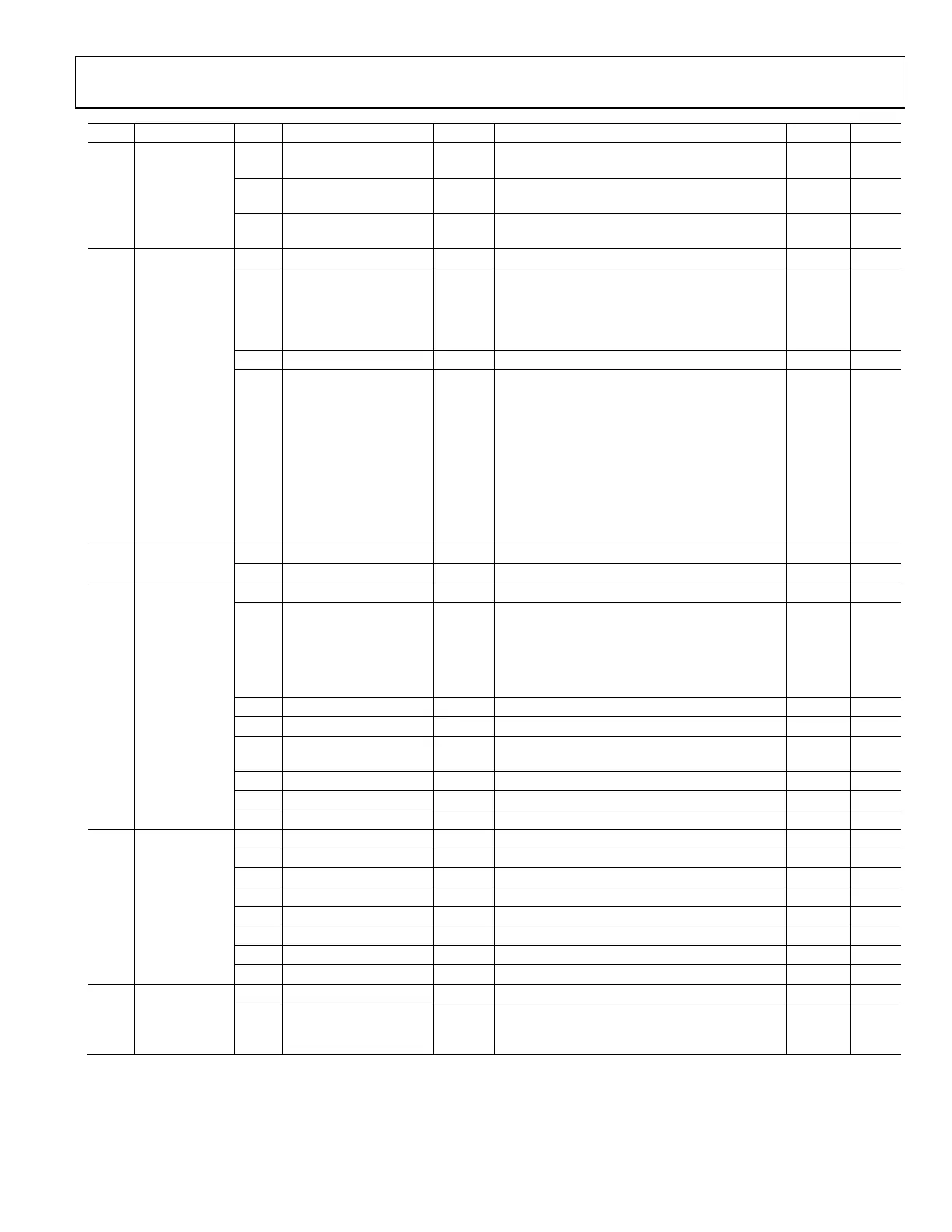

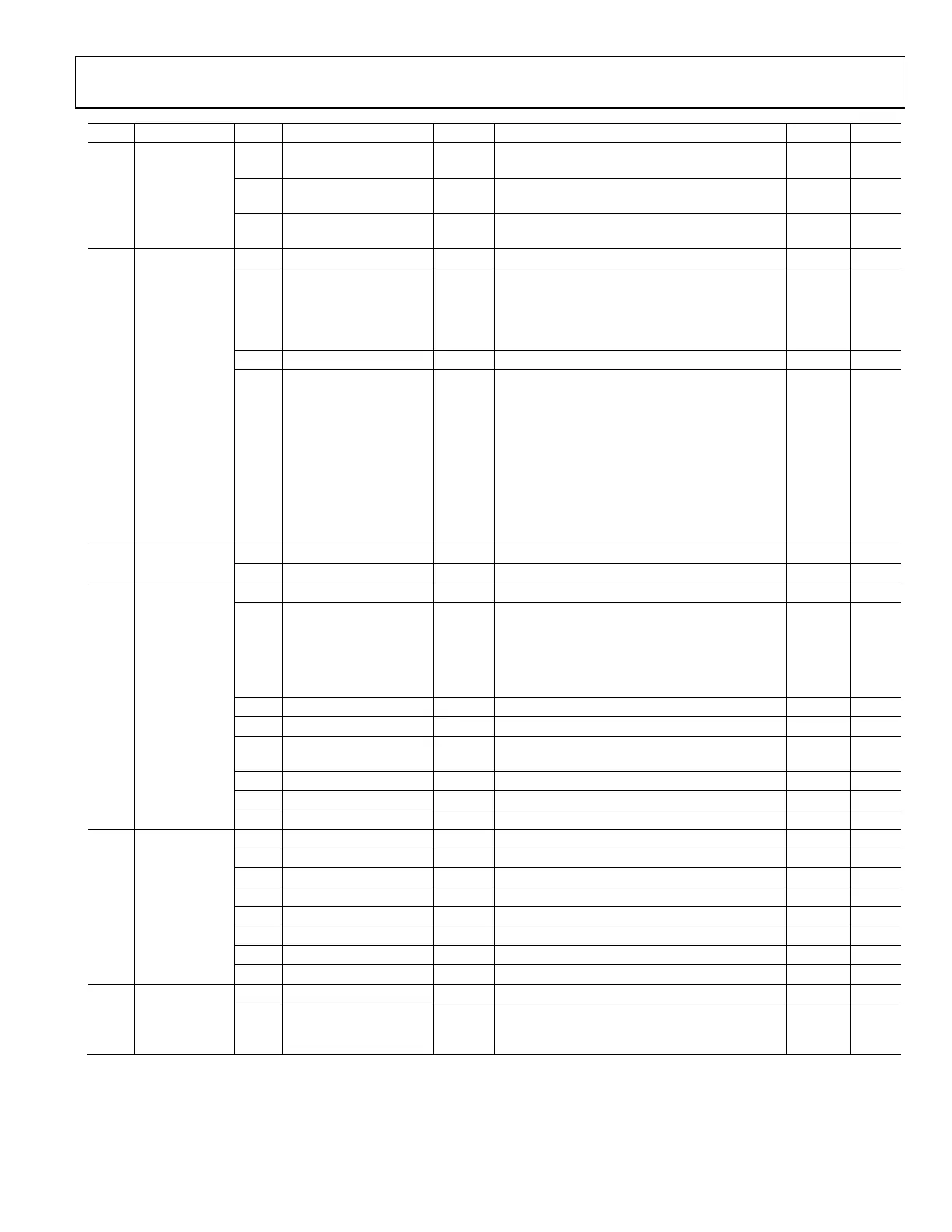

Addr. Name Bits Bit Name Settings Description Reset Access

Set this bit to include the EVENT_MASK register

in the configuration register CRC calculation.

1 CRC_MASK1_EN Set this bit to include the MASK1 register in the

configuration register CRC calculation.

0x0 R/W

0 CRC_MASK0_EN Set this bit to include the MASK0 register in the

configuration register CRC calculation.

0x0 R/W

0x4B6 TEMP_CFG [15:4] RESERVED Reserved. 0x0 R

3 TEMP_START Set this bit to request a temperature sensor

reading. The new temperature reading is

available in 1.25 ms, indicated by the TEMP_RDY

bit in the STATUS0 register. Note that this bit is

self clearing.

0x0 W1

2 TEMP_EN Set this bit to enable the temperature sensor. 0x0 R/W

[1:0] TEMP_TIME Select the number of temperature readings to

average.

0x0 R/W

0 1 sample. New temperature measurement every

1.25 ms.

1 256 samples. New temperature measurement

every 320 ms.

10 512 samples. New temperature measurement

every 640 ms.

11 1024 samples. New temperature measurement

every 1.3 sec.

0x4B7 TEMP_RSLT [15:12] RESERVED Reserved. 0x0 R

[11:0] TEMP_RESULT 12-bit temperature sensor result. 0x0 R

0x4B9 PGA_GAIN [15:14] RESERVED Reserved. 0x0 R

[13:12] VC_GAIN PGA gain for voltage Channel C ADC. 0x0 R/W

00 Gain = 1.

01 Gain = 2.

10 Gain = 4.

11 Gain = 4.

[11:10] VB_GAIN PGA gain for Voltage Channel B ADC. See VC_GAIN. 0x0 R/W

[9:8] VA_GAIN PGA gain for Voltage Channel A ADC. See VC_GAIN. 0x0 R/W

[7:6] IN_GAIN PGA gain for neutral current channel ADC. See

VC_GAIN.

0x0 R/W

[5:4] IC_GAIN PGA gain for Current Channel C ADC. See VC_GAIN. 0x0 R/W

[3:2] IB_GAIN PGA gain for Voltage Channel B ADC. See VC_GAIN. 0x0 R/W

[1:0] IA_GAIN PGA gain for Current Channel A ADC. See VC_GAIN. 0x0 R/W

6 VC_DISADC Set this bit to one to disable the ADC. 0x0 R/W

5 VB_DISADC Set this bit to one to disable the ADC. 0x0 R/W

4 VA_DISADC Set this bit to one to disable the ADC. 0x0 R/W

3 IN_DISADC Set this bit to one to disable the ADC. 0x0 R/W

2 IC_DISADC Set this bit to one to disable the ADC. 0x0 R/W

1 IB_DISADC Set this bit to one to disable the ADC. 0x0 R/W

Set this bit to one to disable the ADC.

0x4E0 VAR_DIS [15:1] RESERVED Reserved. 0x0 R

0 VARDIS Set this bit to disable the total VAR calculation.

This bit must be set before writing the run bit for

proper operation.

0x0 R/W

Loading...

Loading...