2

1.3 Specifications

The Pattern Generator specifications are as follow:

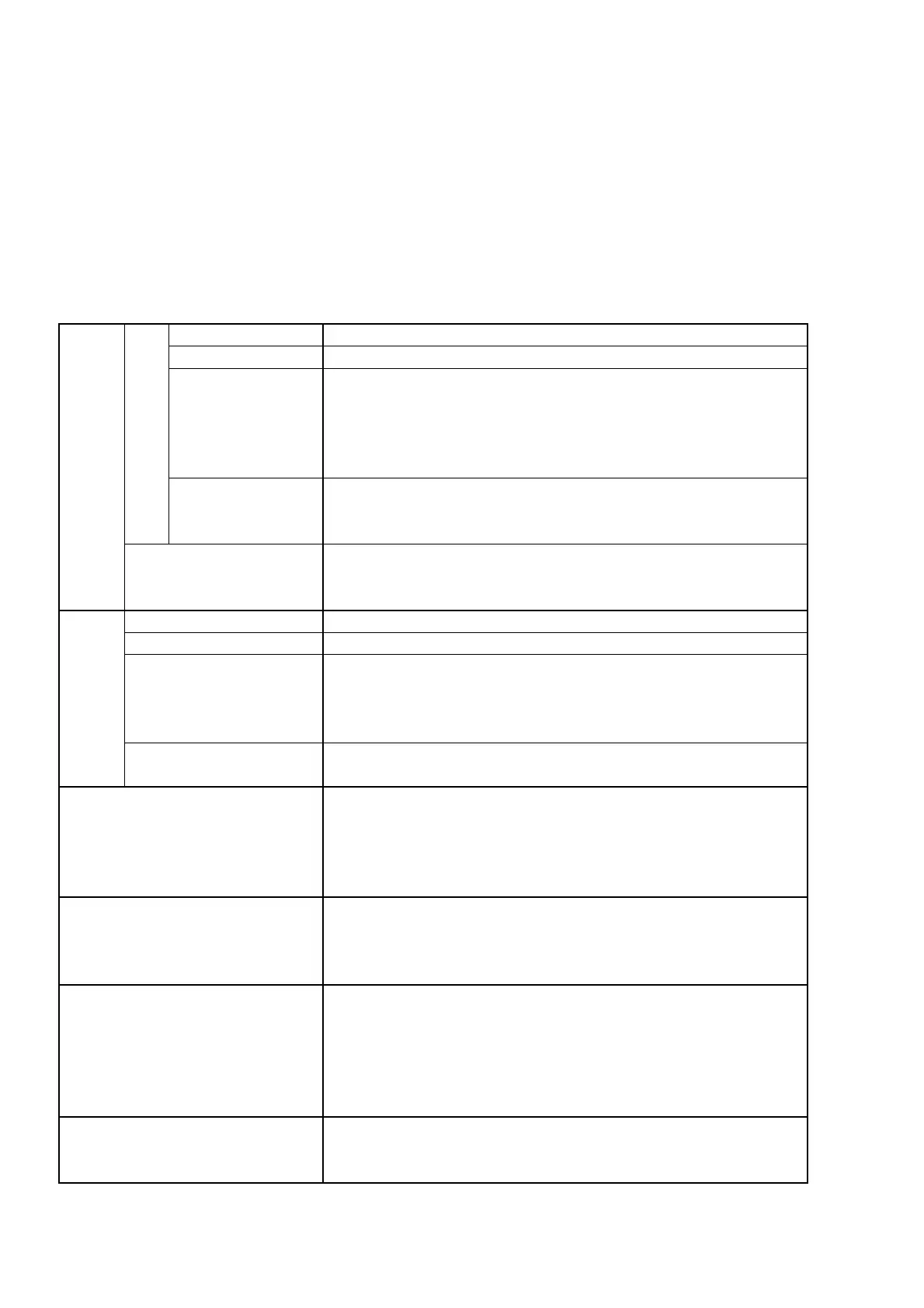

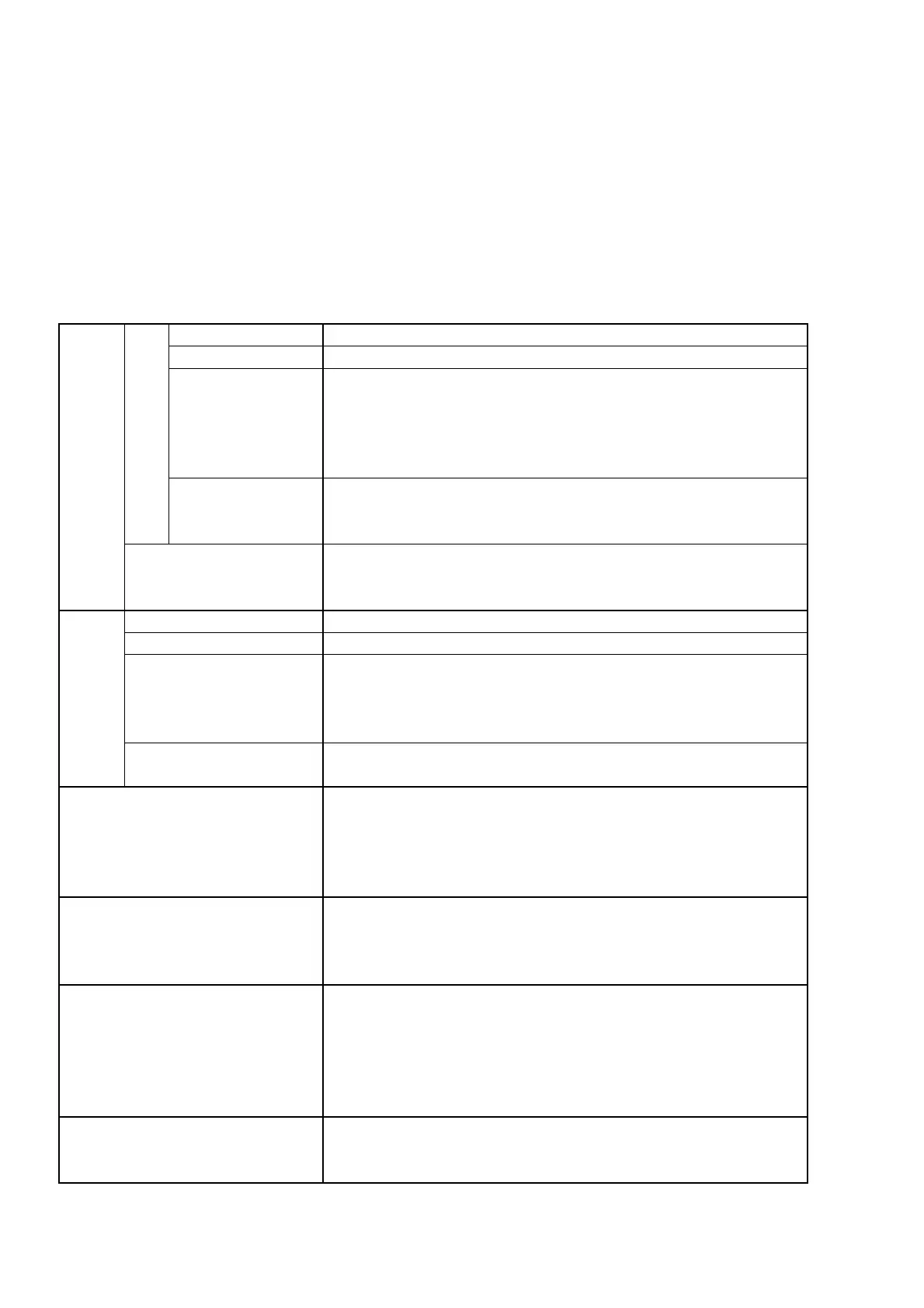

Table 1-2 Pattern Generator specifications

Data

pattern

Idle

pattern

Free

Number of memories

Memory capacity

Pattern delivery

range

Memory write

4 (Defind: 1 to 4)

524288 bit/memory

The first delivery address and the data bit length are specified for each free

pattern memory.

The first delivery address setting range: 00000 to 65535

Data bit length setting range: 2 to 524288 bit

(However, the last delivery address shall be 65535)

Write by 1 byte unit via GPIB

Write enabled when the Pattern Generator output is turned OFF or the idle

pattern is delivered.

PN9 pseudo-random pattern (complying with ITU-T V.52)

PN15 pseudo-random pattern (complying with ITU-T O.151)

“01010101” fixed pattern

1 (Idle)

524288 bit

The first delivery address and the data bit length are specified.

The first delivery address setting range: 00000 to 65535

Data bit length setting range: 2 to 524288 bit

(However, the last delivery address shall be 65535)

Write by 1 byte unit via GPIB

Write enabled when the Pattern Generator output is turned OFF.

Single: Specified data pattern is delivered once (either PN9 or PN15

is delivered twice).

Continuous: Specified data pattern is continuously delivered.

When no data pattern is delivered, the idle pattern is continuously deliv-

ered.

Range: 1 to 99,999 bps

Resolution: 1 bps

Accuracy: As same as the reference generator frequency of

MG3641A/MG3642A units.

1-bit NRZ output (corresponding to two values):

Sequentially output by 1-bit starting from the first bit into Data 2

1

Output.

The Data 2

0

Output logic is fixed to “0”.

2-bit NRZ output (corresponding to four values):

Sequentially output by 2-bits starting from the first bit into Data 2

1

Output

and Data 2

0

Output.

Data 2

0

Output: TTL level

Data 2

1

Output: TTL level

Clock Output: TTL level, rise

Fixed

Number of memories

Memory capacity

Pattern delivery range

Memory write

Delivery method

Send rate

Output method

Output level

Section 1 Overview

Loading...

Loading...