6 3.1 Architecture

CW6632B Bluetooth 3.0 Audio Player SOC Version 1.0.0

Copyright ©2015, www.appotech.com. All Rights Reserved.

3 CPU Core Information

3.1 Architecture

The AXC51-CORE of CW6632B is fully compatible with the MCS-51

TM

instruction set.

The AXC51-CORE employs a pipelined architecture that greatly increases its instruction throughput over the

standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock

cycles to execute, and usually have a maximum system clock of 12MHz. By contrast, the AXC51-CORE executes

most of its instructions in 1 system clock cycle. With system clock running at 48 MHz, it has a peak throughput of 48

MIPS running in on-chip SRAM area.

3.2 Instruction Set

The instruction set of the AXC51-CORE is fully compatible with the standard MCS-51

TM

instruction set; standard

8051 development tools can be used to develop software for the AXC51-CORE. All instructions of AXC51-CORE

are the binary and functional equivalent of their MCS-51

TM

counterparts, including op-codes, addressing modes and

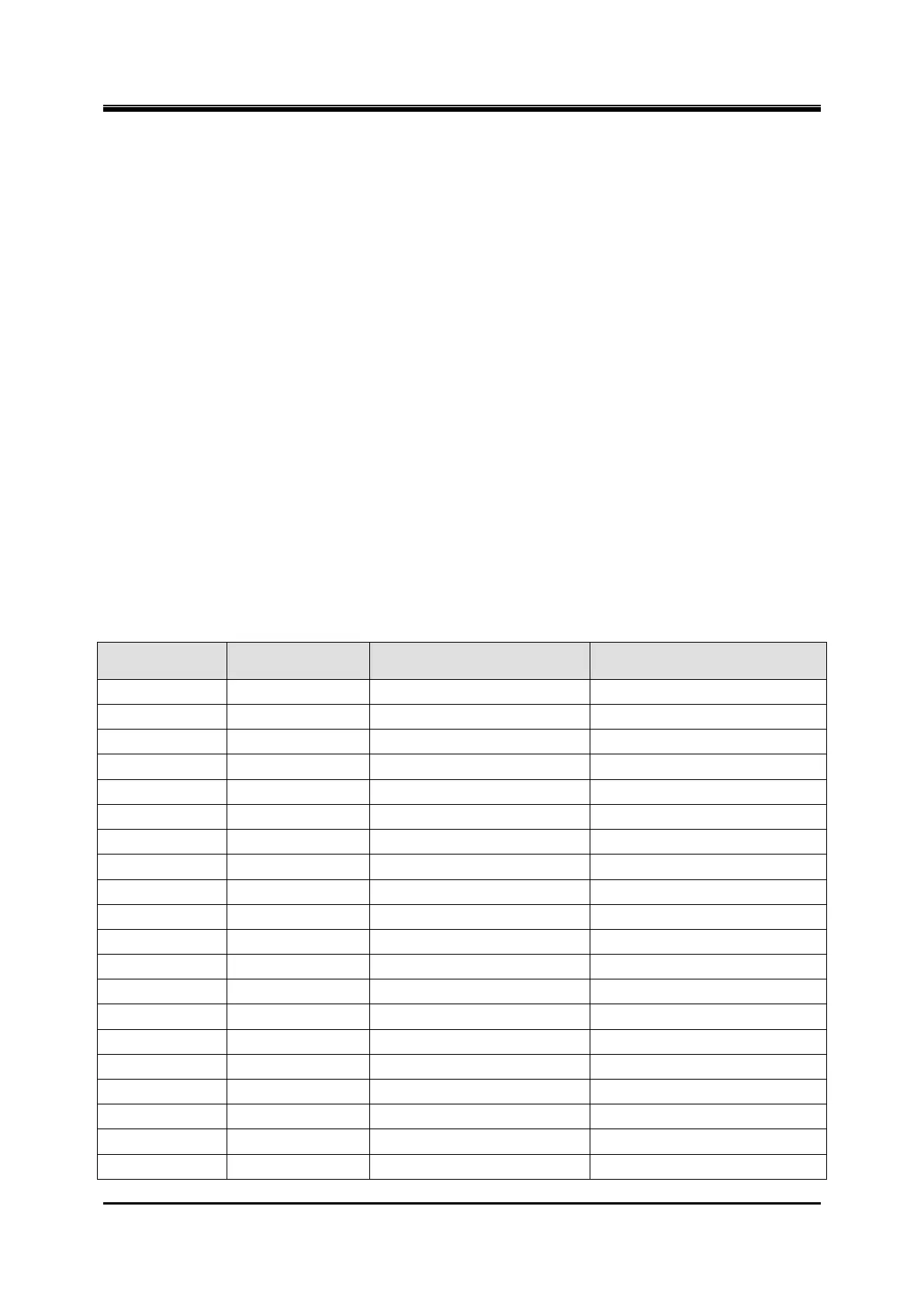

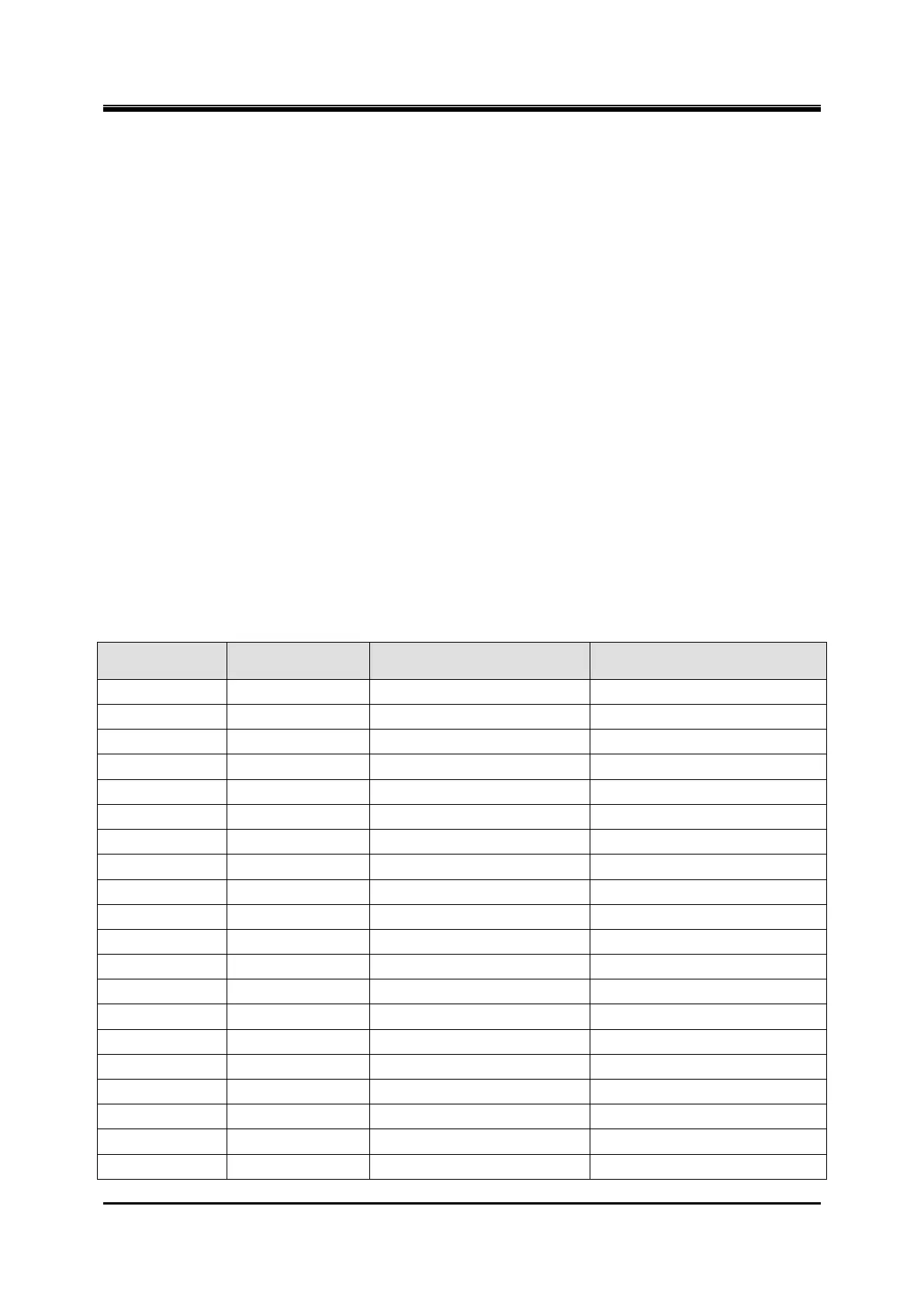

effect on PSW flags. However, instruction timing is different than that of the standard 8051. Table 3-1 shows

AXC51-CORE Instruction Set Summary

Table 3-1 AXC51-CORE Instruction Set Summary

Clock Cycles (running in IRAM)

Loading...

Loading...