3 CPU Core Information 15

CW6632B Bluetooth 3.0 Audio Player SOC Version 1.0.0

Copyright ©2015, www.appotech.com. All Rights Reserved.

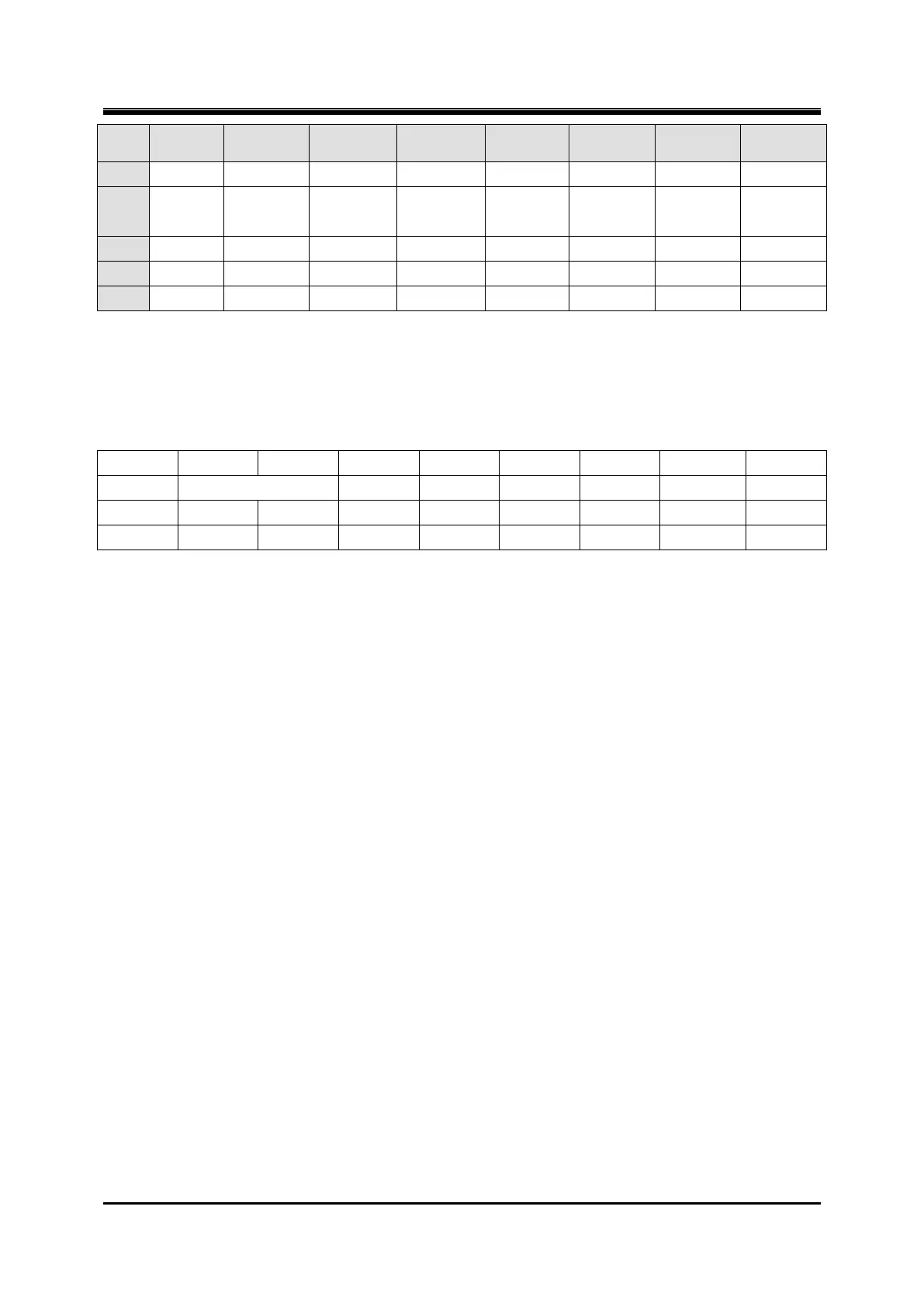

3.7 CPU and Memory related SFR Description

Register 3-1 DPCON – Data Pointer Configure Register

IA: Select Interrupt Vector‟s Base Address

00 = Base address is 0x0003

01 = Base address is 0x4003

10 = Base address is 0x8003

11 = Base address is 0xc003

note:interrupt address is determined by SPMODE1[4]

0 = interrupt base address depend on IA

1 = interrupt base address is 0x2000

DPID0: DPTR0 increase direction control

0 = DPTR increase

1 = DPTR decrease

DPID1: DPTR1 increase direction control

0 = DPTR increase

1 = DPTR decrease

DPAID: DPTR auto increment enables

0 = Auto increment disable

1 = Auto increment enable

DPTSL: DPSEL toggle enable

0 = DPSEL toggle disable

1 = DPSEL toggle enable

EINSTEN: Extern instruction enables

0 = Disable

1 = Enable

Loading...

Loading...