118 16.3 Operation Guide

CW6632B Bluetooth 3.0 Audio Player SOC Version 1.0.0

Copyright ©2015, www.appotech.com. All Rights Reserved.

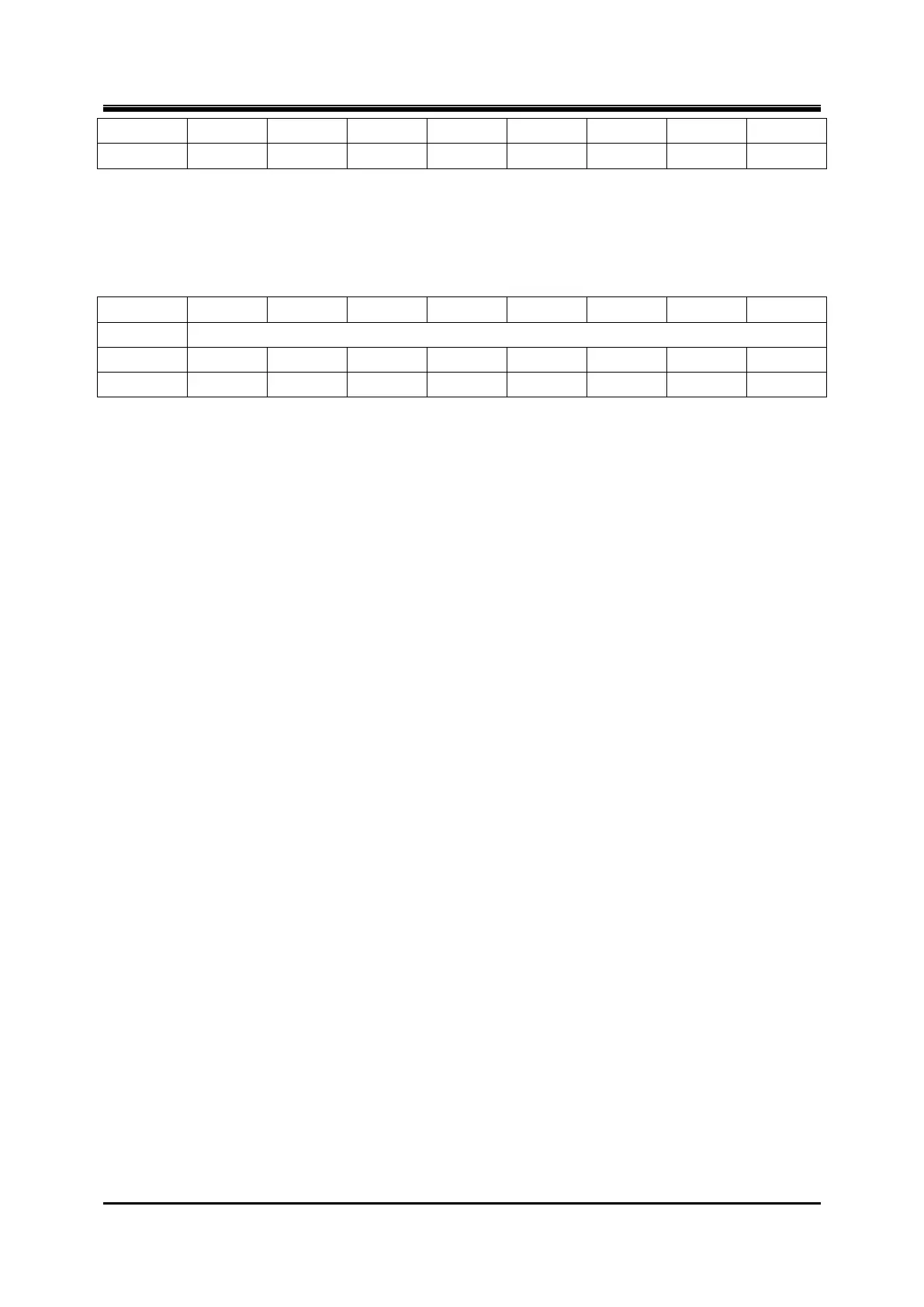

IIS_DMA_RD_P_CNT0-1: During the process of dma, we can know how many datas have been already read from

the memory by reading these two registers.

IIS_DMA_RD_P_CNT0 is the lower bits and IIS_DMA_RD_P_CNT1 is the higher bits

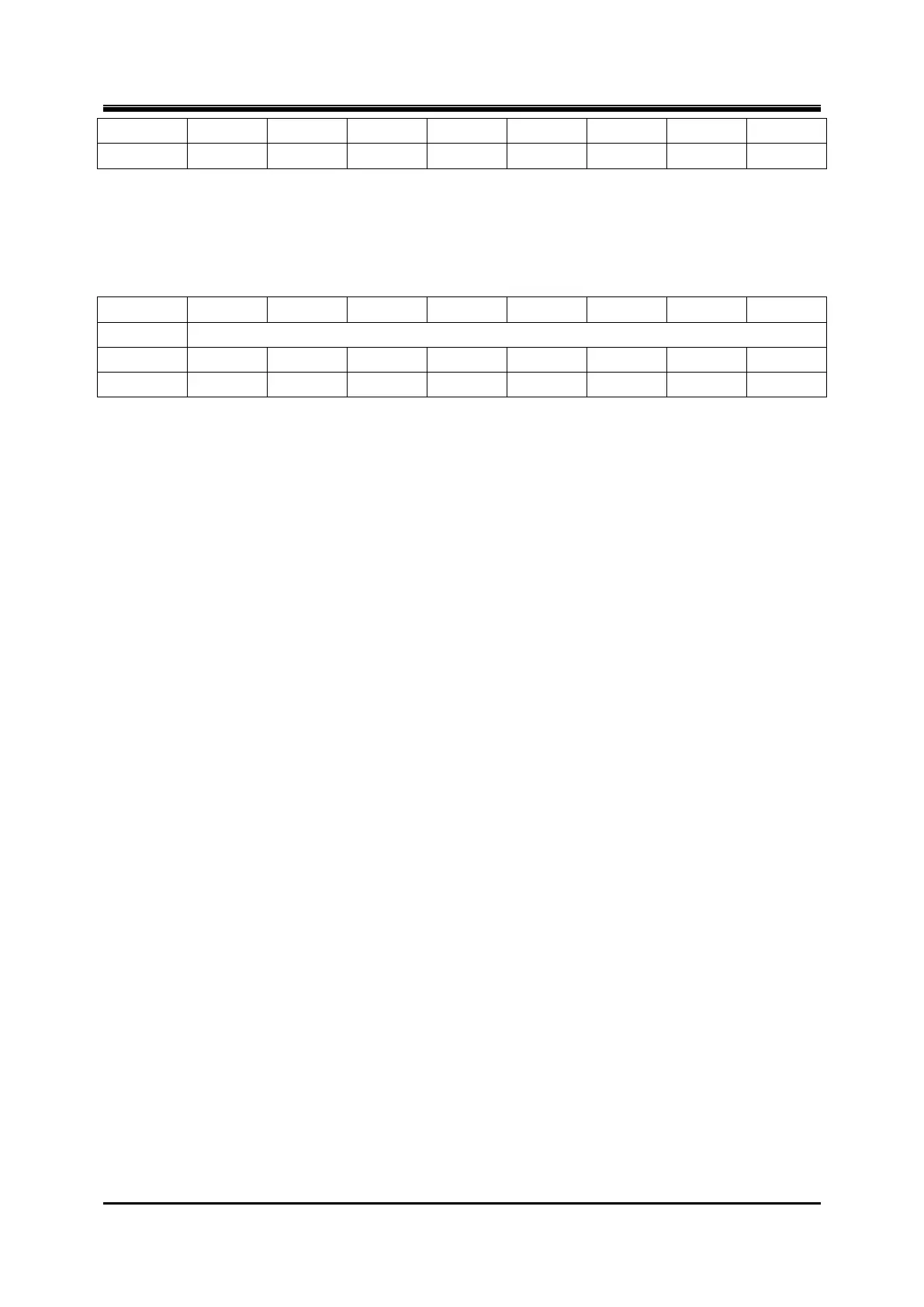

Register 16–17 IIS_DMA_WR_P_CNT0-1:

IIS_DMA_WR_P_CNT0-1: During the process of dma, we can know how many datas have been already written to

memory by reading these two registers.

IIS_DMA_WR_P_CNT0 is the lower bits and IIS_DMA_WR_P_CNT1 is the higher bits

16.3 Operation Guide

16.3.1 CPU RD/WR

For 2-wire data mode,set IO direction,1-wire Data input/output hardware auto control

configure other IO direction. Such as WS,BCLK,REFCLK(if need)

if master mode,set BAUDRATE, IIS_BCLK_CFG,set IIS_VALBIT ,IIS_ALLBIT for different bits transfer

write IIS_CON0-1 for Slave mode, sample edge, LTHWS,CH_SEL,DATA_FMT,TXRX_MOD,OP_MOD,IIS_IE

setting.

enable IIS_EN kick start RX/TX or both

For data receive ,if both left and right channel data available, then hardware will halt until left channel is

coming.

So if first receive right channel data ,hardware will ignore it.

Write IIS_DAT0 8 times to send data out

wait TX_BUF_EMPTY = 1,then write another 2 data to send ,if tx

wait IIS_PND = 1,when rx mode,then read IIS_DAT0-7 out

16.3.2 loop

this IIS support loop operation mode.that is send out data come from RX pin. And the tx data will delay 2-4 sample

before really data come out.and the first 2-4 sample being send out is all 0s.must config OP_MOD=2‟b11;

Loading...

Loading...