16 Integrated Interchip Sound (IIS) 117

CW6632B Bluetooth 3.0 Audio Player SOC Version 1.0.0

Copyright ©2015, www.appotech.com. All Rights Reserved.

IIS_ADR0:Write two times for dma write address.

Frist time is the higher address part, second time is the lower address part

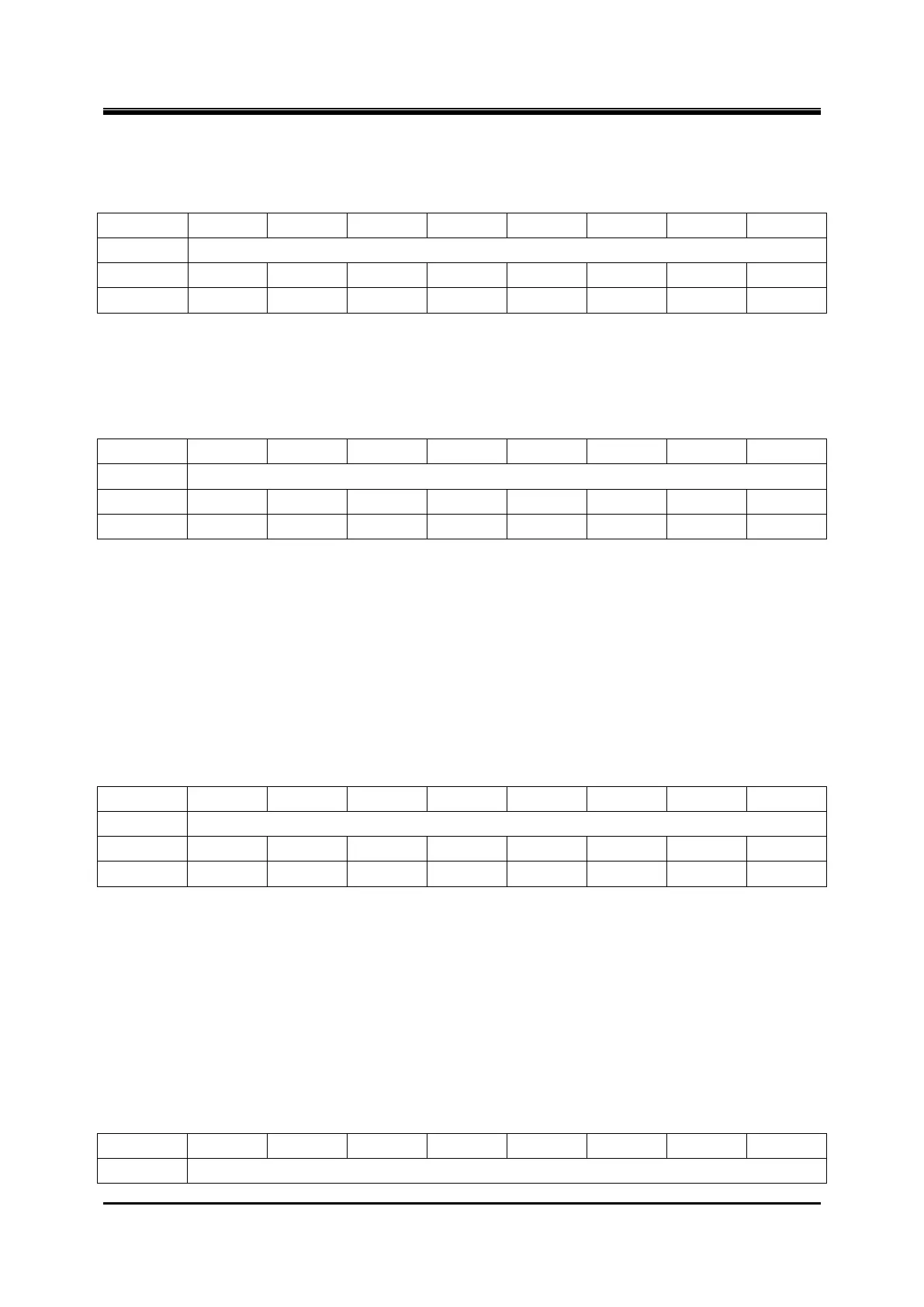

Register 16–13 IIS_ADR1:DMA read addr

IIS_ADR1:Write two times for dma read address.

Frist time is the higher address part, second time is the lower address part

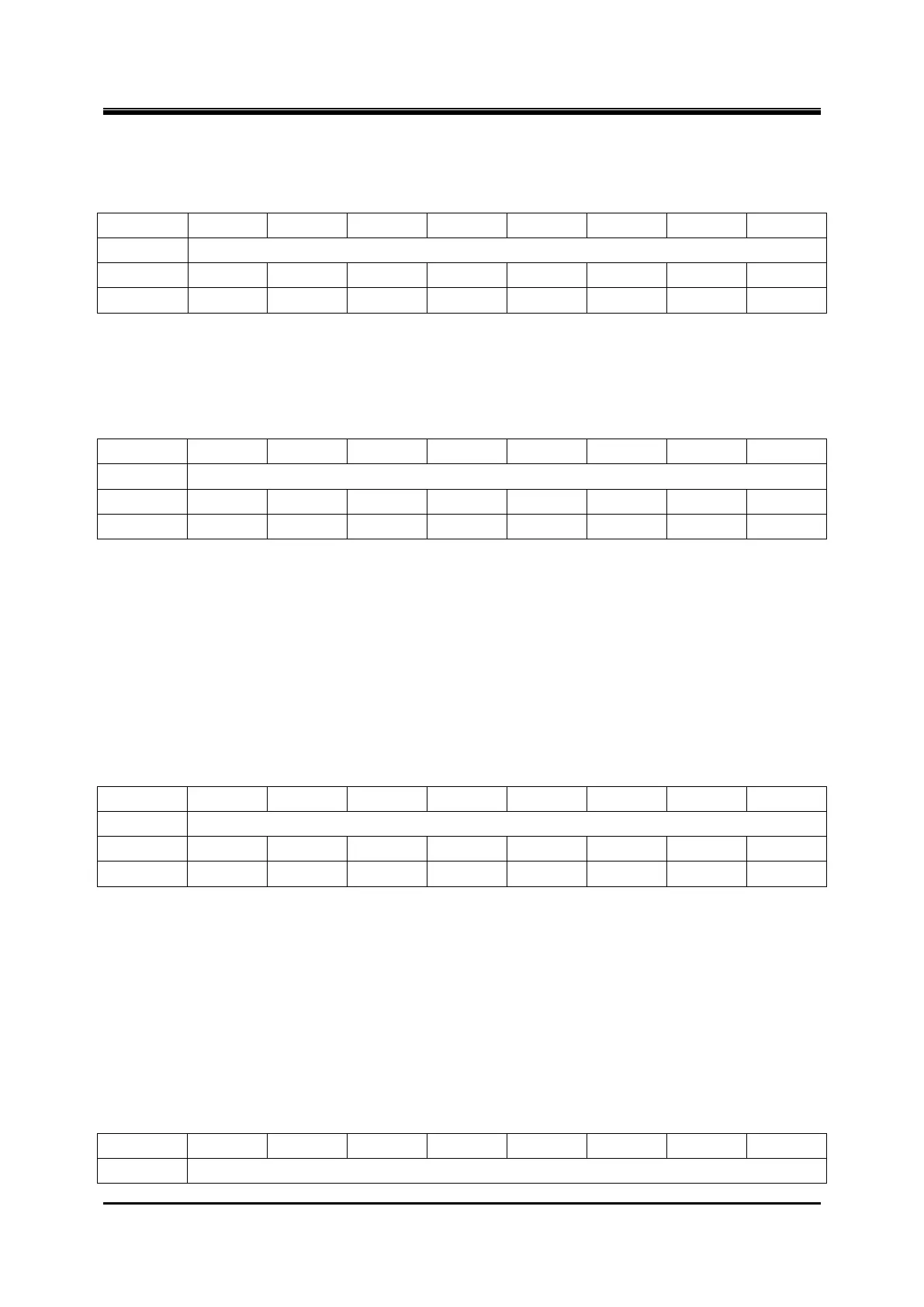

Register 16–14 IIS_DMA_RD_CNT0-1:

IIS_DMA_RD_CNT0-1: the counter of IIS DMA data, use for kick start DMA transfer and dma_loop mode

Write:

Firstly, write IIS_DMA_RD_CNT0 8 bits, this register is the low bits

secondly, write IIS_DMA_RD_CNT1 2 bits, this register is the high bits,write this register is the same time to

kick start DMA transfer

For iis dma one time is two buffers, IIS_DMA_RD_CNT should be odd

the real data bits is : ({IIS_DMA_RD_CNT1,IIS_DMA_RD_CNT0}+1) * 16 bits

Register 16–15 IIS_DMA_WR_CNT0-1:

IIS_DMA_WR_CNT0-1: the counter of IIS DMA data, use for kick start DMA rx and dma_loop mode

Write:

Firstly, write IIS_DMA_WR_D_CNT0 8 bits, this register is the low bits

secondly, write IIS_DMA_WR__CNT1 2 bits, this register is the high bits,write this register is the same time to

kick start DMA rx

For iis dma one time is two buffers, IIS_DMA_WR_CNT should be odd

the real data bits is : ({IIS_DMA_WR_CNT1,IIS_DMA_WR_CNT0}+1) * 16 bits

Register 16–16 IIS_DMA_RD_P_CNT0-1:

Loading...

Loading...