34 4.3 Clock System

CW6632B Bluetooth 3.0 Audio Player SOC Version 1.0.0

Copyright ©2015, www.appotech.com. All Rights Reserved.

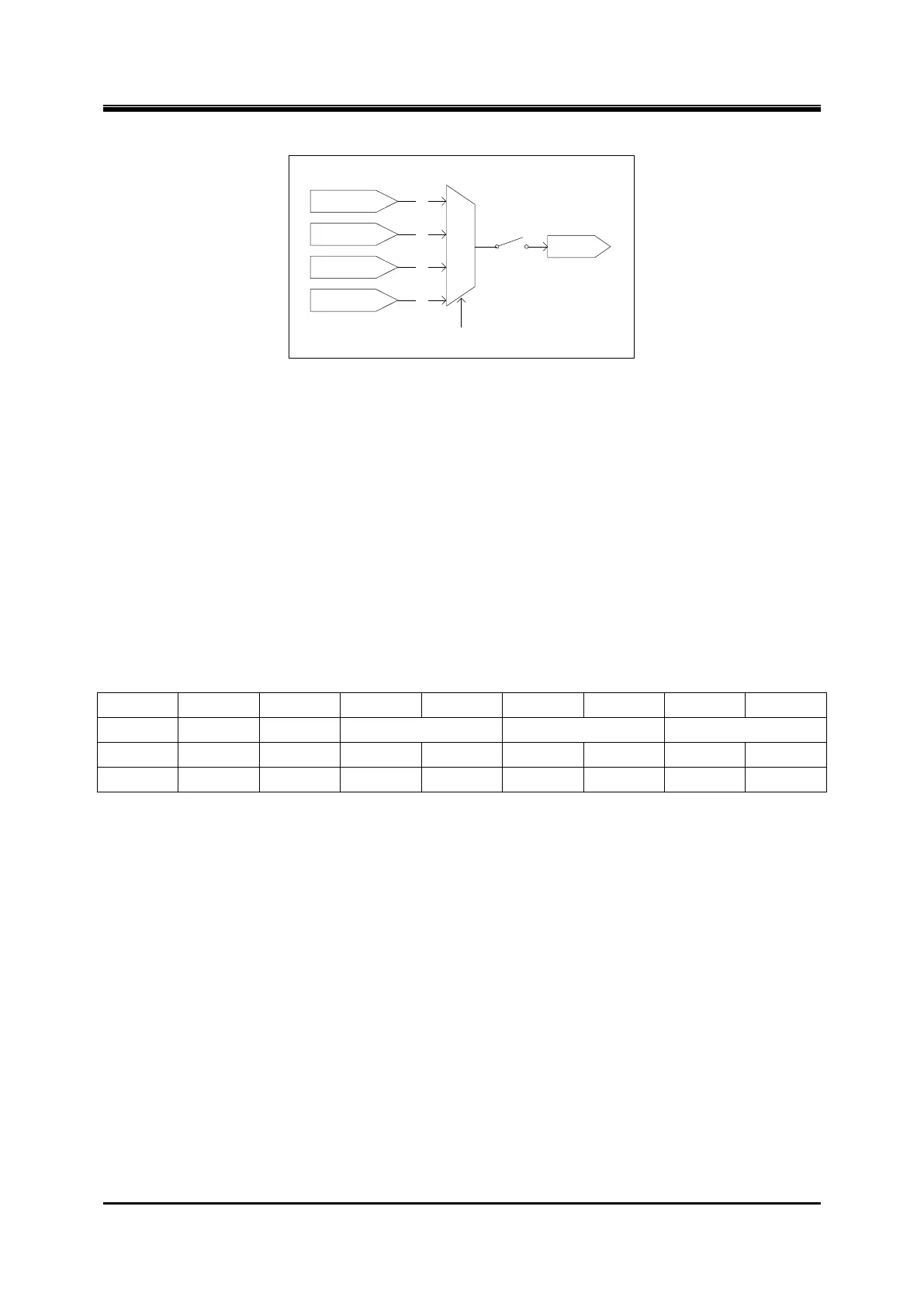

11 = 1MHz div form XOSC26M

pll_1m

rc1m

xosc_tclk

x26m_1m

00

01

10

11

MUX

CLKCON[1:0]

ir_clk

PCON0[3]

Figure 4-6 IR clock select figure

4.3.2 Clock Gating

CW6632B provides comprehensive clock gating options for eliminating power-wasting activities.

4.3.3 Phase Lock Loop (PLL)

CW6632B provides one on-chip Phase Locked Loop (PLL 48M) clock generators. The PLL has reference clock from

external 32 KHz/4M/12 M crystal oscillators to provide a stable reference clock and the reference clock is multiplied

to provide the final PLL output.

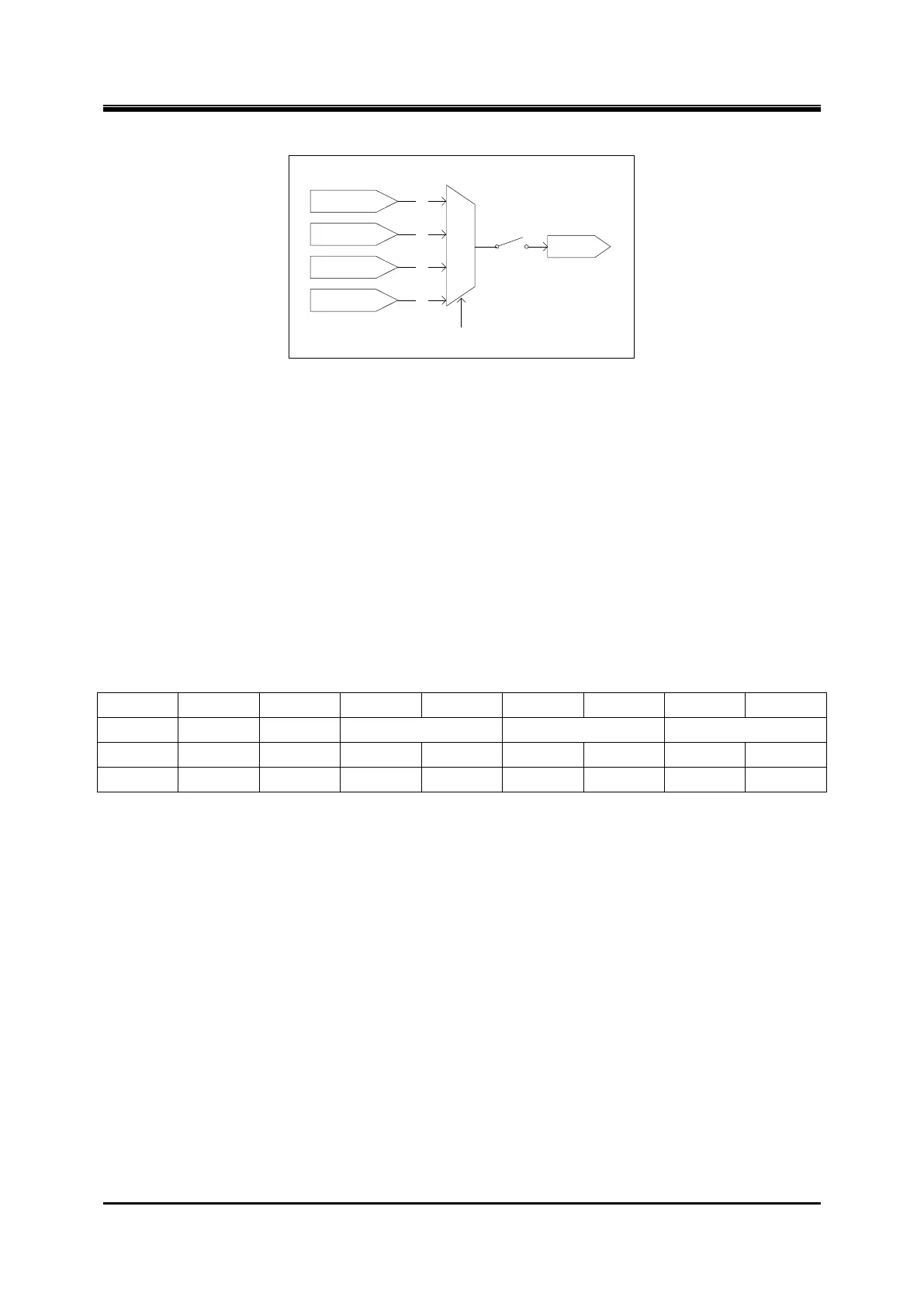

Register 4-9 PLLCON – PLL Configuration

PLL1AREF_SEL: PLL1 input reference clock digital select

00 = XOSC

01 = RCOSC

10 = RCOSC div

11 = Reserved

PLL2AREF_SEL: PLL2 input reference clock digital select

00 = XOSC

01 = RCOSC

10 = PLL1 div

11 = Reserved

SDADCCLK_SEL: SDADC clockl select

00 = XOSC inv

01 = XOSC

10 = PLL2 div2 inv

Loading...

Loading...