4 Reset Generation 35

CW6632B Bluetooth 3.0 Audio Player SOC Version 1.0.0

Copyright ©2015, www.appotech.com. All Rights Reserved.

11 = PLL2

SDADCEN: SDADC clock enable

0 = disable

1 = enable

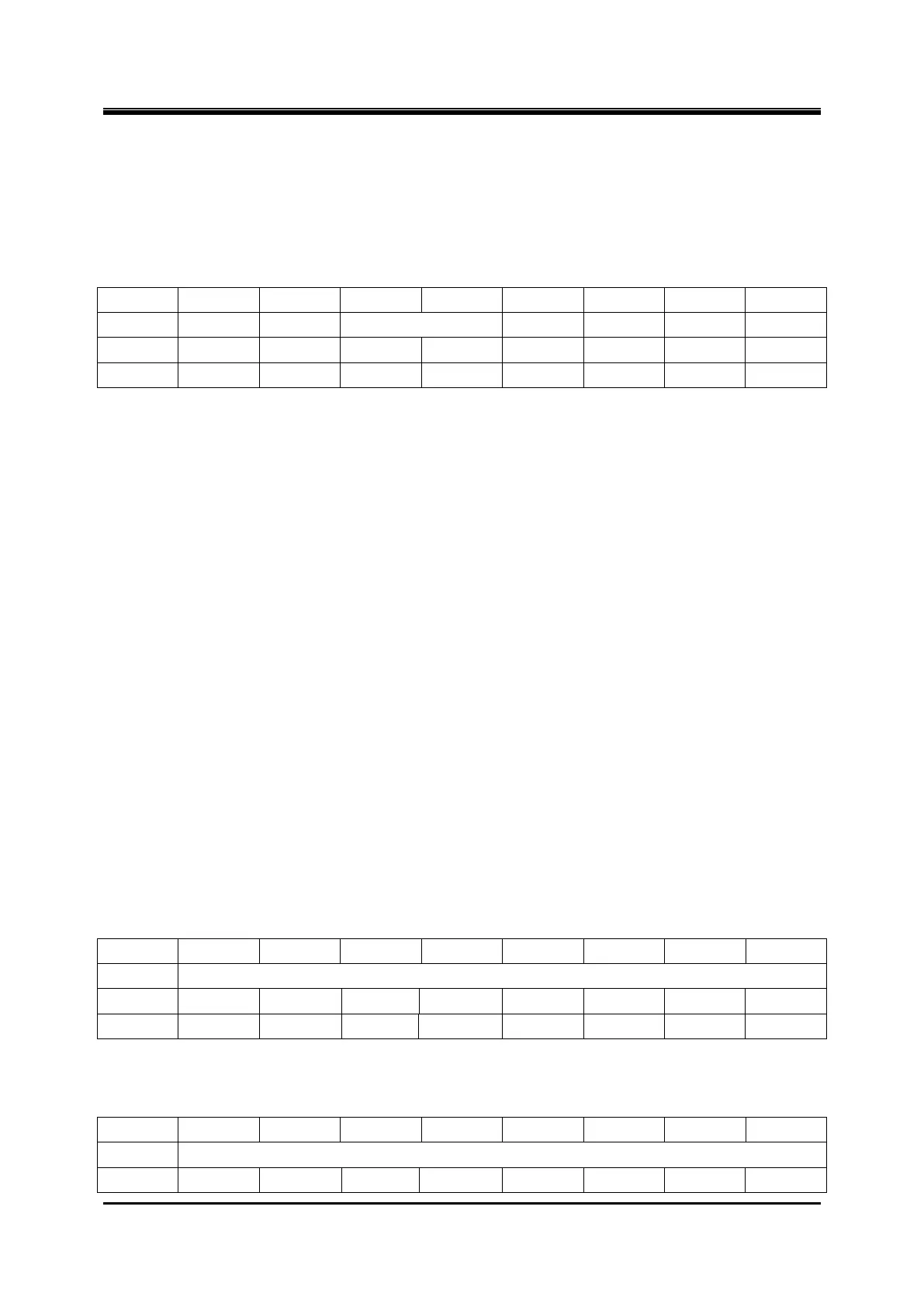

Register 4-10 PLL1CON – PLL1 Configuration

PLL1AEN: PLL analog module enables

0 = Disable

1 = Enable

PLL1DEN: PLL digital module enables

0 = Disable

1 = Enable

When change the divider, also need write 1 to PLLDEN

PLL1DEN32K: PLL digital 32K enable

0 = disable

1 = enable

X12EN: XOSC 12M 374 divider enable bit

0 = Disable

1 = Enable

PLL1AREF_SEL: PLL input reference clock analog select

00 = 12M XOSC

01 = 4M XOSC

10 = 32K XOSC

11 = 32K XOSC

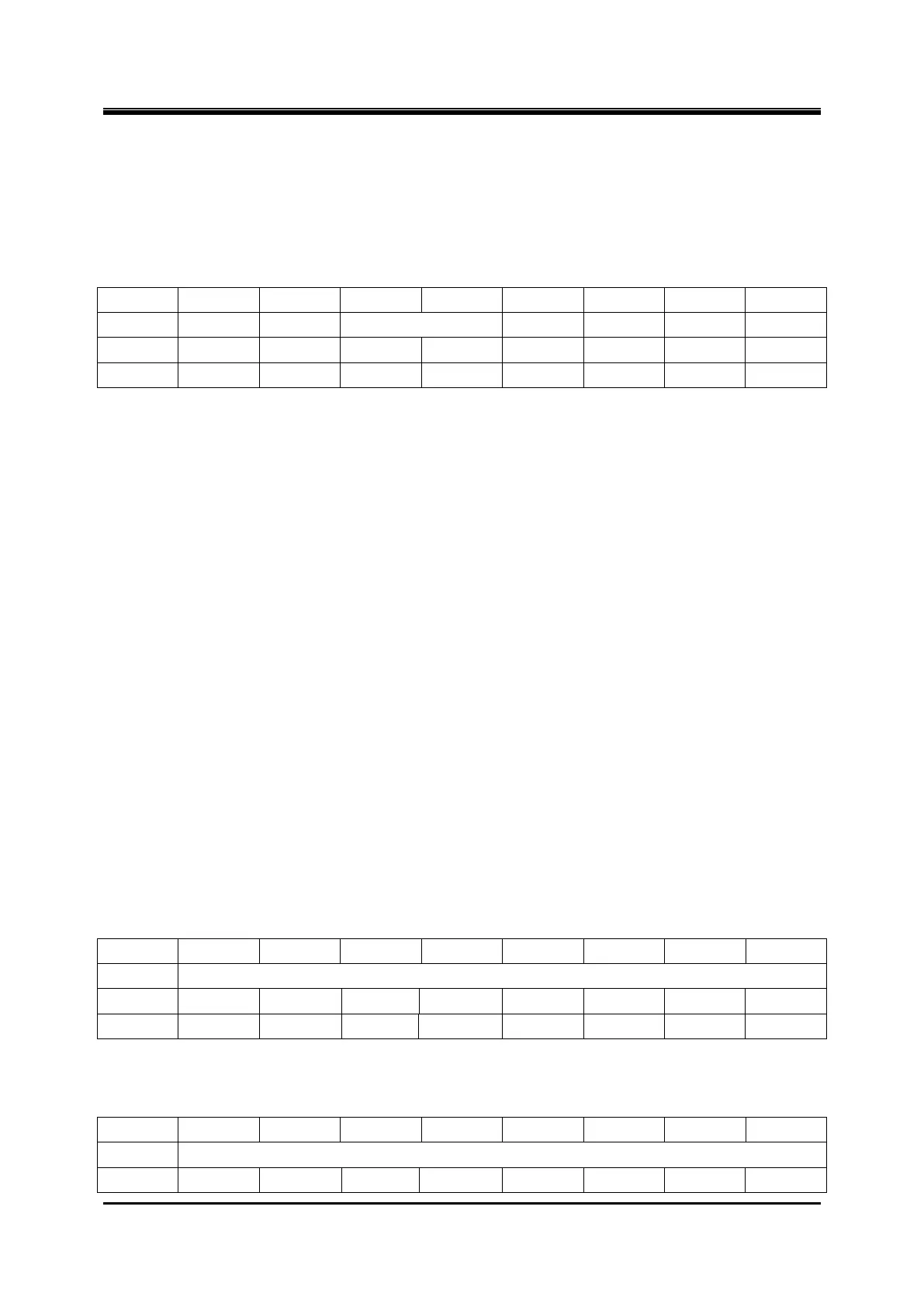

Register 4-11 PLL1DIV – PLL1 clock div for PLL2

PLL1IDV Clock = 48MH/PLL1DIV;

Register 4-12 PLL1INT – PLL1 integer low

Loading...

Loading...