36 4.3 Clock System

CW6632B Bluetooth 3.0 Audio Player SOC Version 1.0.0

Copyright ©2015, www.appotech.com. All Rights Reserved.

PLL1INT = int(60MHz/pll1_refclock)

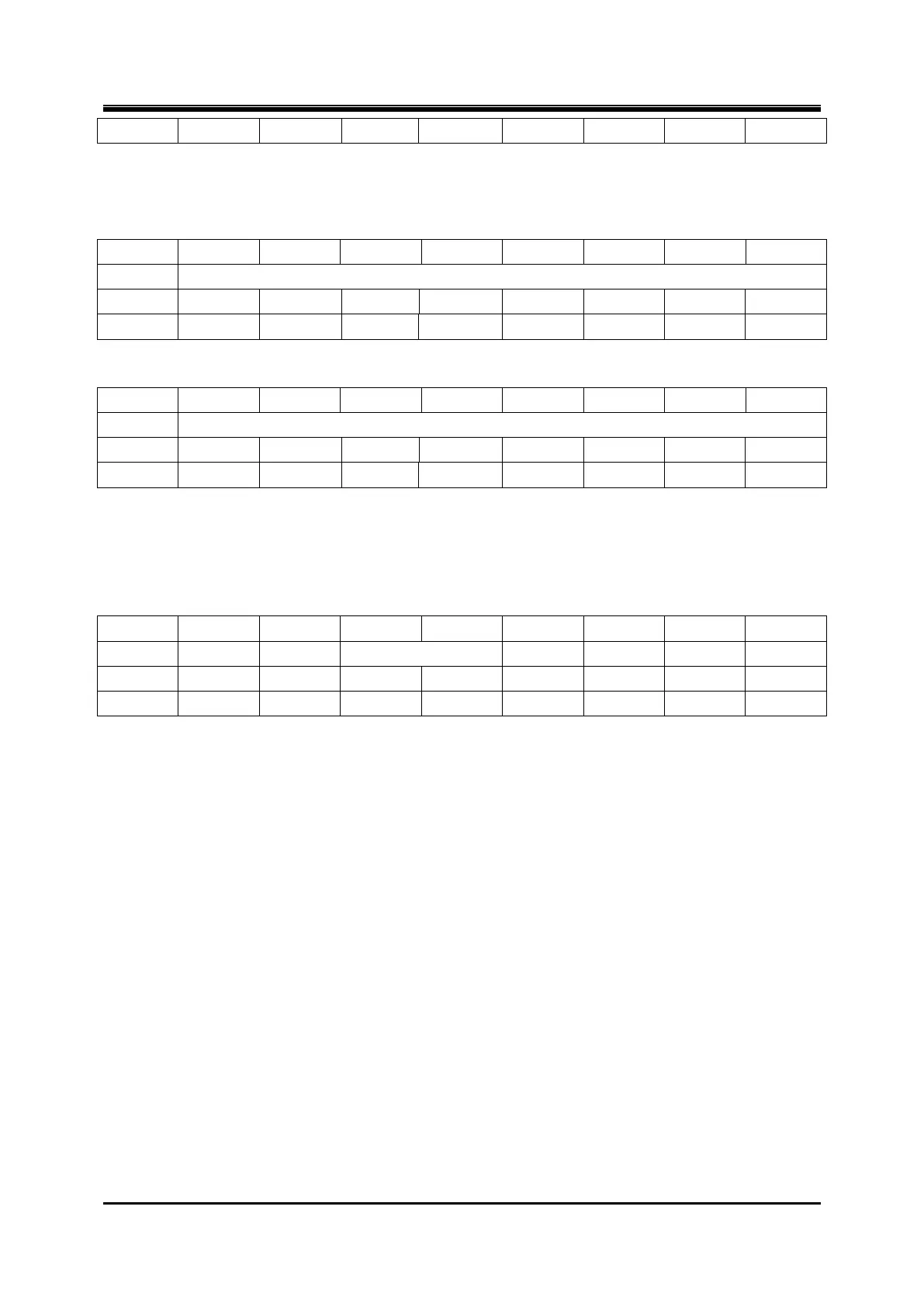

Register 4-13 PLL1FRACH – PLL1 fraction high

Register 4-14 PLL1FRACL – PLL1 fraction low

When the fraction is less than 0.25, set FOVER=1, and fraction = (fraction+1)/2, integer = (integer-1)

When the fraction is more than 0.80, set FOVER=1, and fraction = fraction/2, integer = integer

FRAC = fraction*65535;

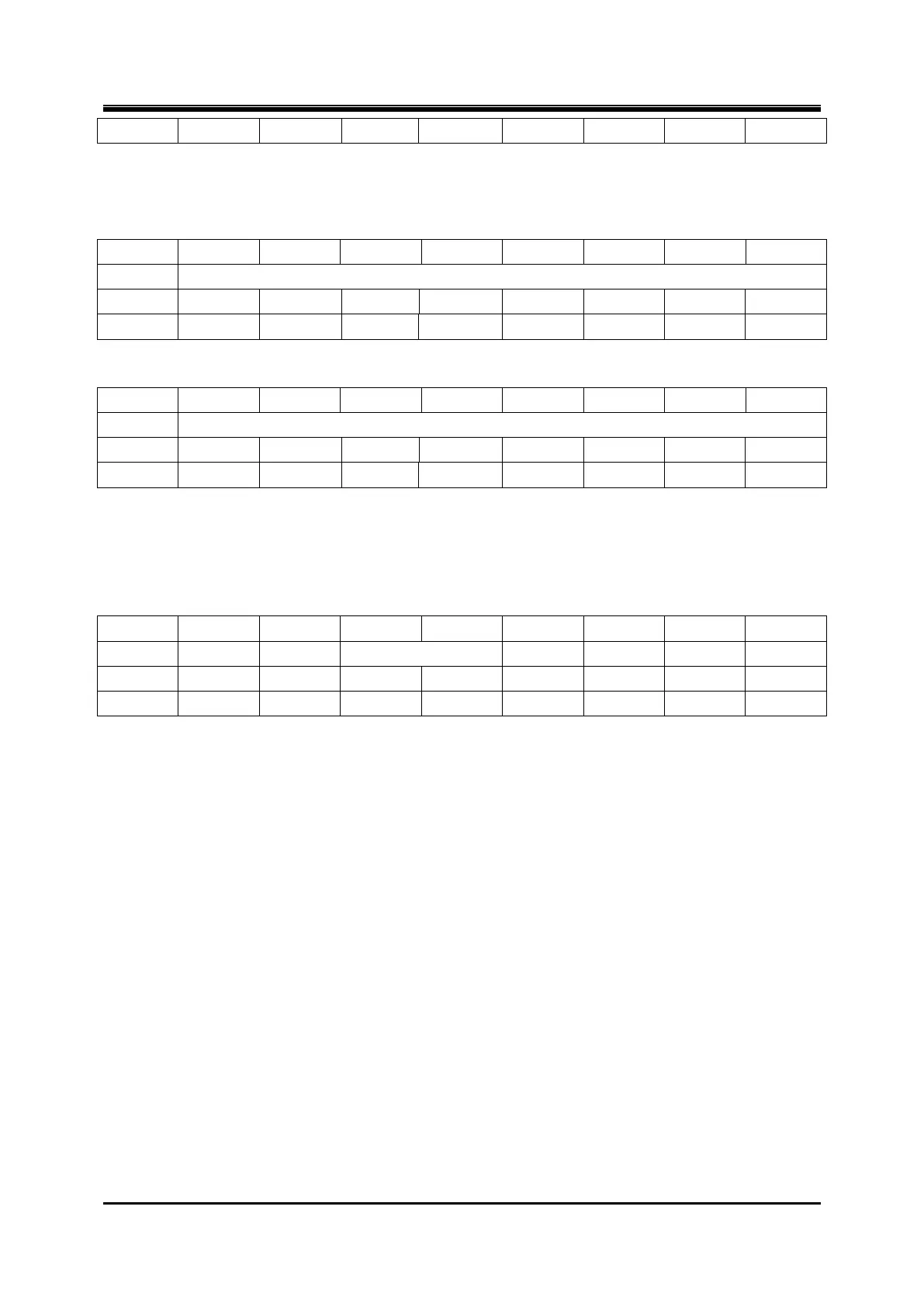

Register 4-15 PLL2CON – PLL2 Configuration

PLL2AEN: PLL2 analog module enables

0 = Disable

1 = Enable

PLL2DEN: PLL2 digital module enables

0 = Disable

1 = Enable

When change the divider, also need write 1 to PLL2DEN

PLL2DEN32K: PLL2 digital 32K enable

0 = disable

1 = enable

PLL1_DIVEN: PLL1 divide enable

0 = disable

1 = enable

PLL2AREF_SEL: PLL2 input reference clock analog select

00 = 12M XOSC

01 = 4M XOSC

Loading...

Loading...