3 CPU Core Information 19

CW6632B Bluetooth 3.0 Audio Player SOC Version 1.0.0

Copyright ©2015, www.appotech.com. All Rights Reserved.

SDADCADOUTEN: SDADC analog data out enable

0 = disable

1 = enable

SDADCDIEN: SDADC digital data input enable

0 = disable

1 = enable

SPI1_MAP: SPI1 port mapping

0 = Select P04, P05, P06

1 = Select P30, P31, P32

INTADR_SEL: interrupt address select

0 = depend on DPCON IA

1 = 0x2000

PAPAMODE : papa mode

0 = normal mode

1 = Parallel mode

SPIINITMODE : SPI Flash initial mode

0 = normal mode

1 = SPI initial mode

SBCDEC_MEN: SBC decoder module enables

0 = Disable

1 = Enable

MP3DEC_MEN: MP3 decoder module enables

0 = Disable

1 = Enable

Note: SPMODE1[1:0] register can be write to “0”, but can‟t be write to “1” after writing “0”.

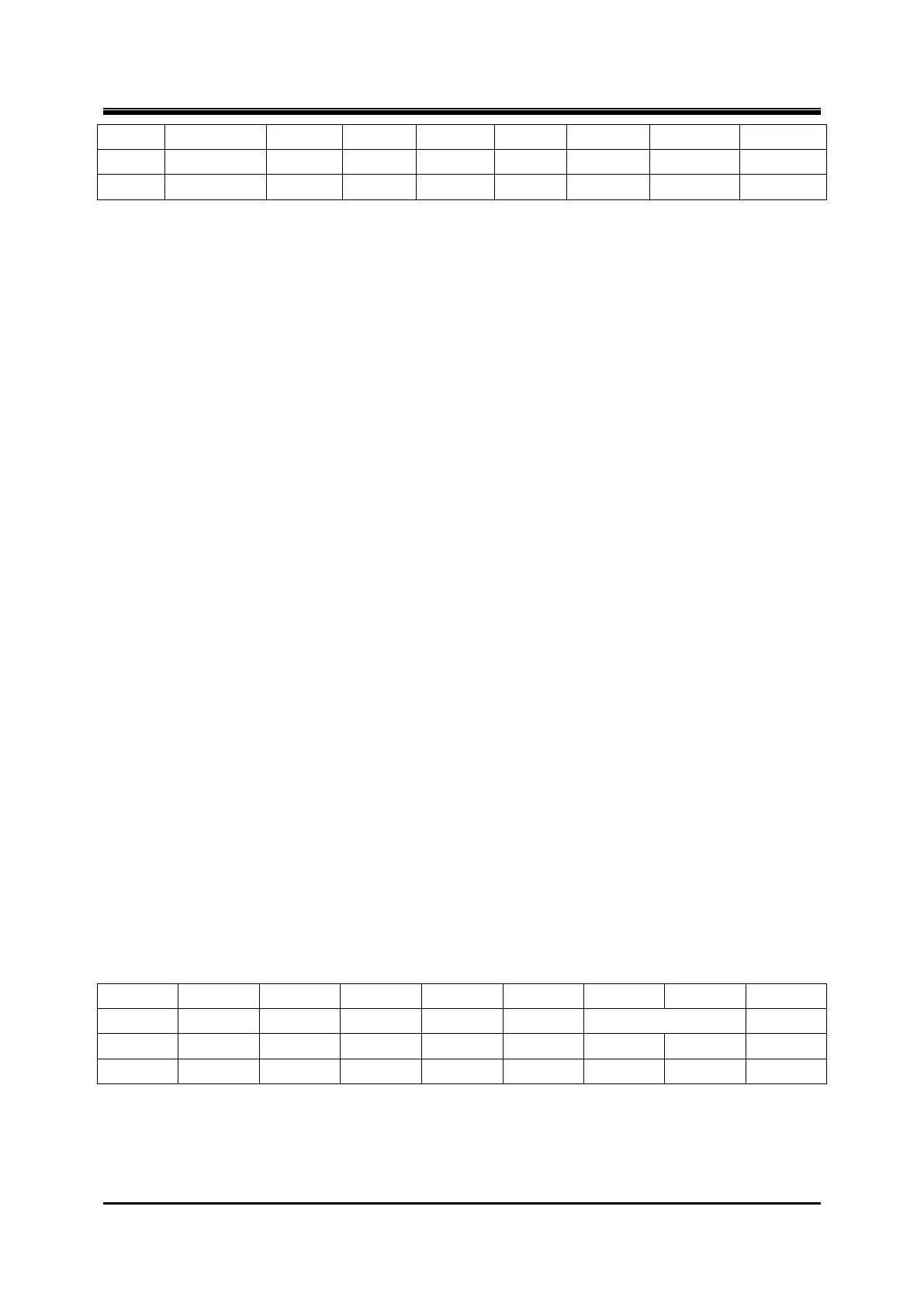

Register 3-11 MEMCON – Memory Mapping Configure

CC0: MIX_CODE2 mapping

0 = IROM32 map to address 0x4000~0x6fff

1 = SRAM2 map to address 0x4000~0x6fff

CC1: MIX_CODE3 mapping

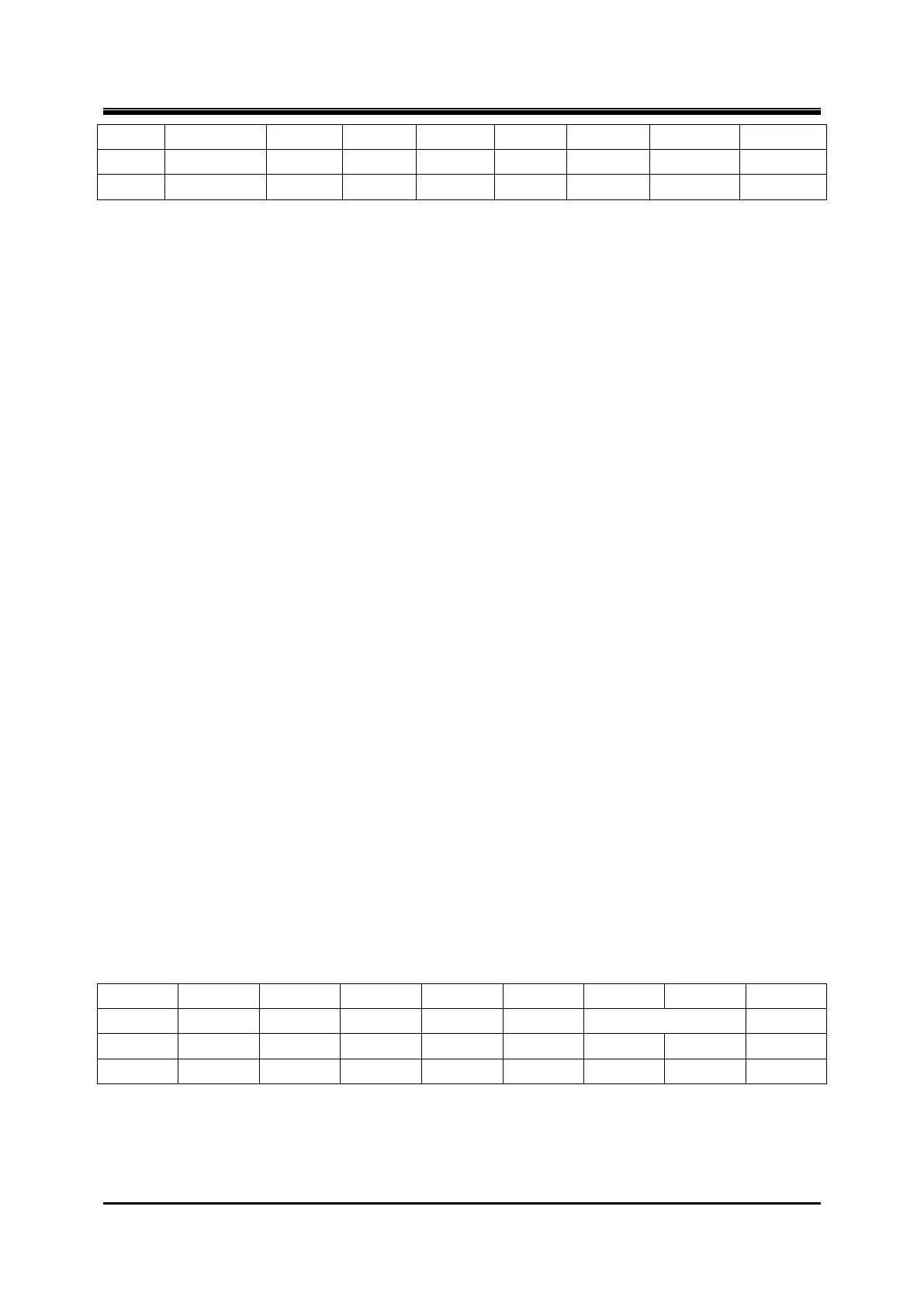

Loading...

Loading...