5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

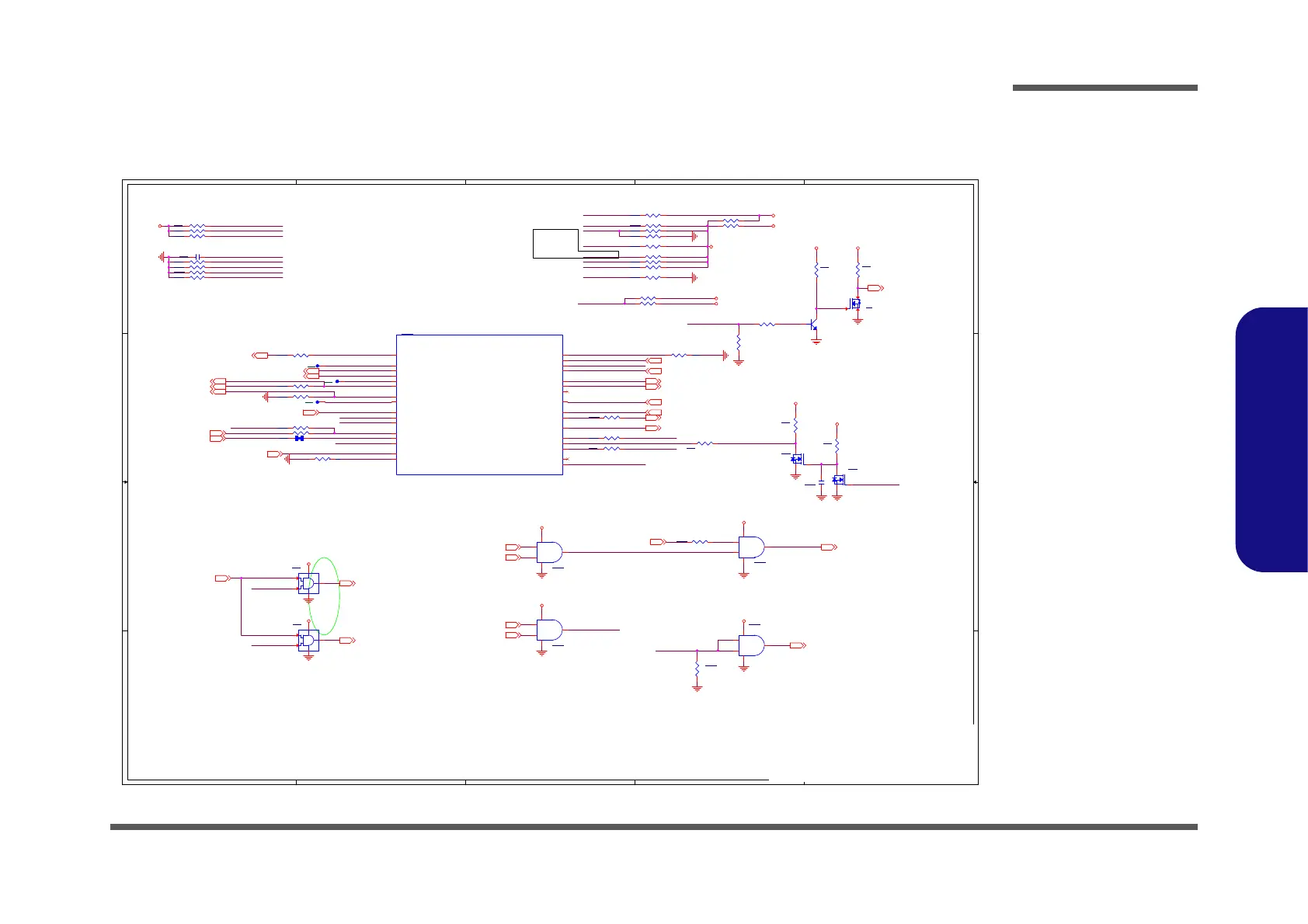

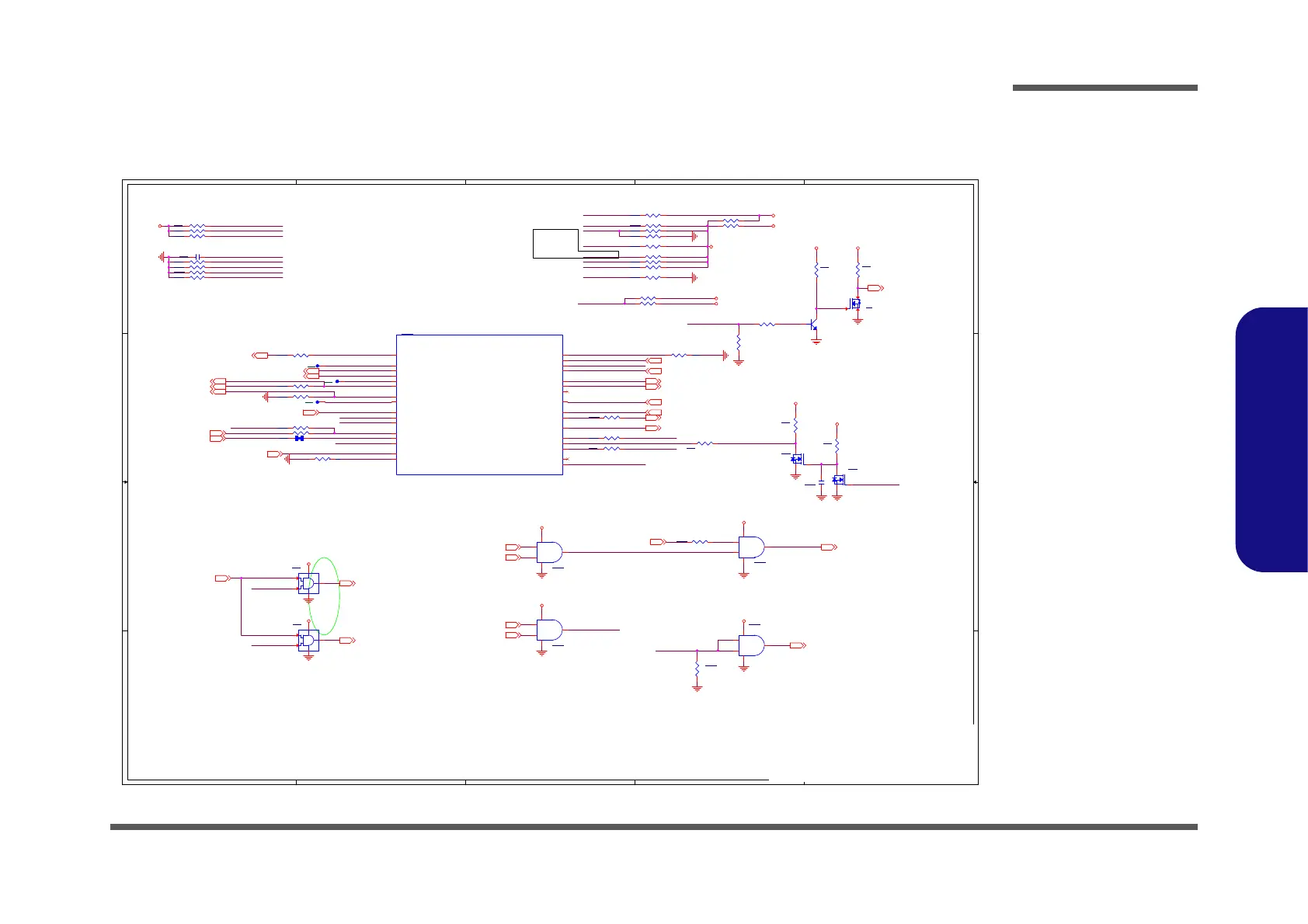

Tiger Lake U K/20 POWER CONTROL

PLT_RST# to Buffer

1125

LOW-> 3.3 V

HIGH-> 1.8 V

NO TERMINATION

NOT SAMPLED

DEFAULT 3.3V

3.3V

update value6/17

VCCIO_EN

AC_PRESENT

PM_BATLOW#

PWR_BTN#

RSMRST#

SYS_PWROK

PCH_PWROK

PCH_DPWROK

PCH_PWROK_EC

PCH_PWROK

SYS_RESET#

SYS_PWROK

PLT_RST#

ALL_SYS_PWRGD

SUSBC_EC

SUSC#_PCH

SUSB#_PCH

RSMRST#

SYS_RESET#

PLT_RST#

SLP_S5#

SLP_S0#

SLP_SUS#_R

PCH_PWROK_EC SYS_PWROK

PCH_PWROK

RSMRST#

PCH_DPWROK

SPIVCCIOSEL

PM_SLP_LAN#

PCH_PWROK

SLP_A#

CPU_C10_GATE#

PROCPWRGD

PWR_BTN#

PM_BATLOW#

VCCST_PWRGD H_VCCST_PWRGD

ALL_SYS_PWRGD

PCIE_WAKE#

AC_PRESENT

EXT_PWR_GATE#

LAN_WAKEUP#

PCIE_WAKE#

LAN_WAKEUP#

EXT_PWR_GATE#

VCCST_OVERRIDE

VCCST_OVERRIDE

GPD7_REST

TBTA-PCH_I2C_INT

TBTA-PCH_I2C_INT

PCH_SLP_WLAN#_R GPD9_RTD3

PCH_DPWROK_EC

EXT_PWR_GATE#

GPD7_REST

VCCST_OVERRIDE

VDD33.3VS

VDD3

VDD3

VDD3

VDD3

VDD3

VDD3

3.3V

VCCST

3.3VA 3.3VA

3.3VA

VDD3

3.3VA

PCH_DSW3.3

SUSB#10,31,46,47,48,51

RSMRST#10,33

BUF_PLT_RST# 21,30,31,33,34,35,36,39

VDDQ_PWRGD50

ALL_SYS_PWRGD 27,33,44

PM_PWROK33

H_VR_READY44

SUSBC_EC33

SUSC# 51,53

SUSB# 10,31,46,47,48,51

RSMRST#10,33

SUSC#_PCH33

SLP_S0#33,51

SUSB#_PCH33

SLP_SUS#33,38,46

PCH_PWROK_EC33

SM_INTRUDER_N9

CPU_C10_GATE# 33,51

PWR_BTN# 33

PCIE_WAKE# 30,33,34,36

AC_PRESENT 33,52

LAN_WAKEUP# 34

LAN_DISABLE# 34

3.3_VCCST_OVERRIDE 51

GPD7_REST 39

TBTA-PCH_I2C_INT 40

PCH_SLP_WLAN#_R33

GPD9_RTD335

PCH_DPWROK_EC33

Title

Size Document Number R e v

Date: Sheet

of

6-71-NV400-D02A

D02A

[10] CML U L POWER CONTROL

A3

10 61Thursday, August 06, 2020

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Title

Size Document Number R e v

Date: Sheet

of

6-71-NV400-D02A

D02A

[10] CML U L POWER CONTROL

A3

10 61Thursday, August 06, 2020

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Title

Size Document Number R e v

Date: Sheet

of

6-71-NV400-D02A

D02A

[10] CML U L POWER CONTROL

A3

10 61Thursday, August 06, 2020

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

R1724.7K_04

R81 0_04

U30

74AHC1G08GW

1

2

5

4

3

R155 *0_04

R173 8.2K_04

R853 *0_04

R199 100K_04

R12

100K_1%_04

R820

61.9K_1%_04

R201 *0_04

R858 100K_04

R163 *100K_04

R179 100K_04

R563 *100K_04

PQ27

MMBT3904H

B

E C

C52 0.1u_6.3V_X5R_02

R36 *14mil_02

R564 100K_04

R851 *100K_04

R15

1M_04

R10

100K_1%_04

R55*1K_04

C583

*0.01u_50V_X7R_04

R37 *100K_04

R835 0_04

U49D

74LVC08APW

12

13

11

147

R31 *3.3K_1%_04

R821 100K_04

R23 10K_04

U18L

TGL_U_IP_EXT

DK35

DSW_PW ROK

DF10

SYS_PWROK

DN35

PCH_PWROK

DT49

SPIVCCIOSEL

CE5

VCCSTPWRGOOD_TCSS

BP8

VCCST_PWRGD

BP9

VCCST_OVERRIDE

DM37

INTRUDER#

DG31

GPP_H3/SX_EXIT_HOLDOFF#

DM41

GPD2/LAN_WAKE#

DK39

WAKE#

DK41

GPD3/PWRBTN#

DV49

SLP_SUS#

DD42

GPP_B12/SLP_S0#

DT44

GPD9/SPL_WLAN#

DJ43

GPD4/SLP_S3#

DW12

GPP_F21/EXT_PWR_GATE2#

DR41

GPD6/SLP_A#

DJ41

GPD5/SLP_S4#

DN43

GPD7

CW40

GPP_B11/PMCALERT#

DN39

SLP_LAN#

DT41

GPD11/LANPHYPC/DSW LDO_MON

DD41

GPP_B13/PLTRST#

DN27

GPP_H18/CPU_C10_GATE#

BM9

PROCPWRGD

DM35

RSMRST#

DR12

GPP_F20/EXT_PWR_GATE#

DK43

GPD1/ACPRESENT

DD10

SYS_RESET#

DN41

GPD0/BATLOW#

DM43

GPD10/SLP_S5#

R200 100K_04

U49C

74LVC08APW

9

10

8

147

T14

R181 *4.7K_04

S

D

G

Q3A

SM2004KDWH

2

61

U49A

74LVC08APW

1

2

3

147

R34 60.4_1%_04

R35

1K_04

R193

0_04

R328 *100K_04

R180 *100K_04

T41

U49B

74LVC08APW

4

5

6

147

R158 *10K_04

R823 0_04

R817 *10K_04

T12

S

D

G

Q3B

SM2004KDWH

5

34

R11

100K_04

Q2

2SK3018S3

G

DS

R562 0_04

R182 10K_04

R852 0_04

R174 10K_04

R191 *0_04

U36

74AHC1G08GW

1

2

5

4

3

Loading...

Loading...