R35

49.9_1%_04

R1 4 1K _0 4

C25 1

*0.1 u_1 0V_X 7R_0 4

R 1 86 51_ 04

R34

2 . 2K _04

R9*1K_04

H_RSVD_K28

R30 *51_04

R6 51_ 04

C252

* 0. 1 u _10 V_ X7 R _04

R37

* 220 _04

R12 *1K_04

R7*1K_04

Q1 6

*G71 1ST9U

OUT

1

VC C

2

GND

3

R5 51_ 04

C22 6

*0 .1 u_ 16V _Y 5 V_ 04

R2 5 51 _04

R13 *1K_04

R28

2.2K_04

R36

49 .9_1%_04

R1 95 10 0_0 4

R196 *1K_04

R 1 0 51_ 04

R29

* 2 20_ 04

R 198 75 _1 % _0 4

R8*1K_04

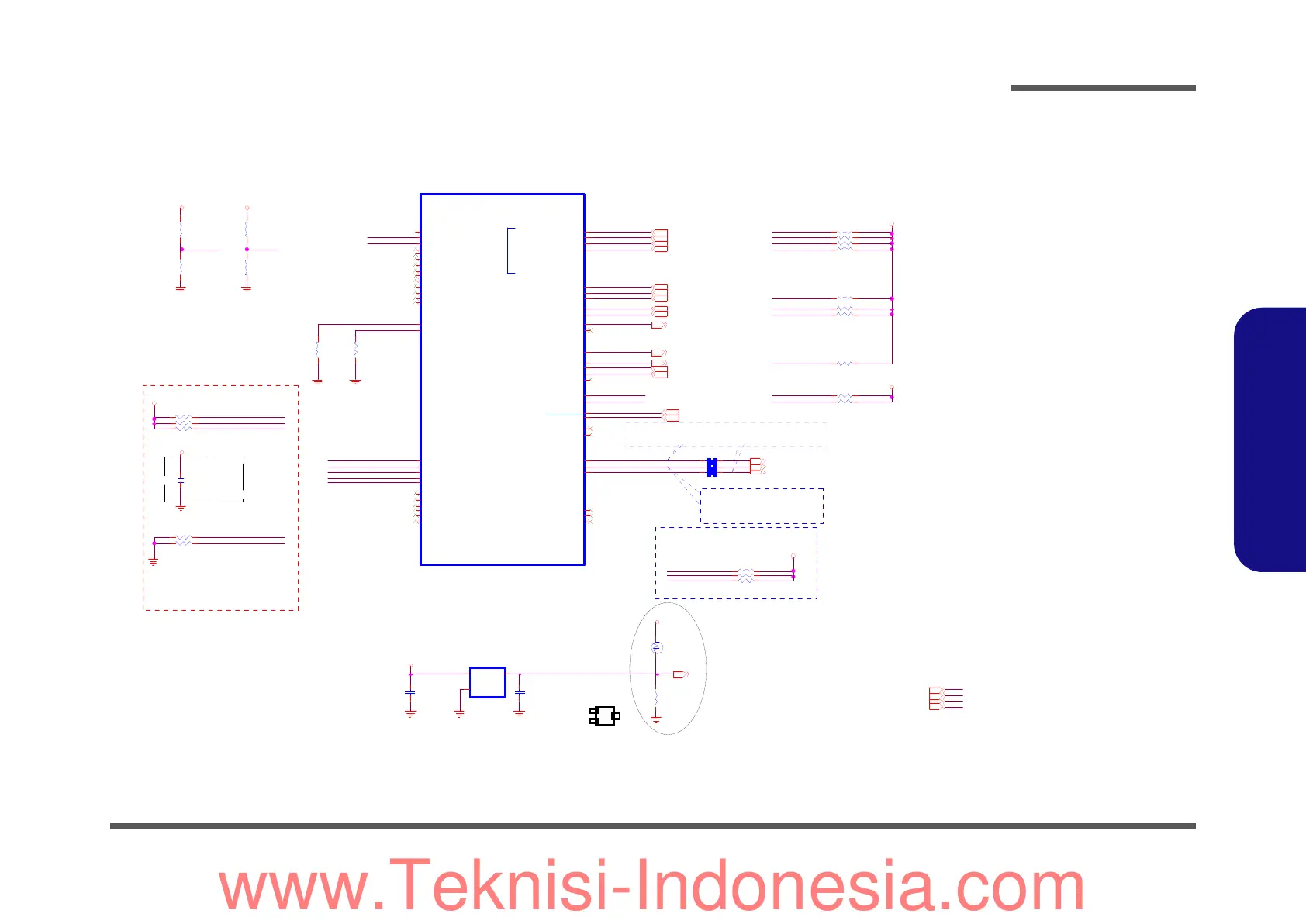

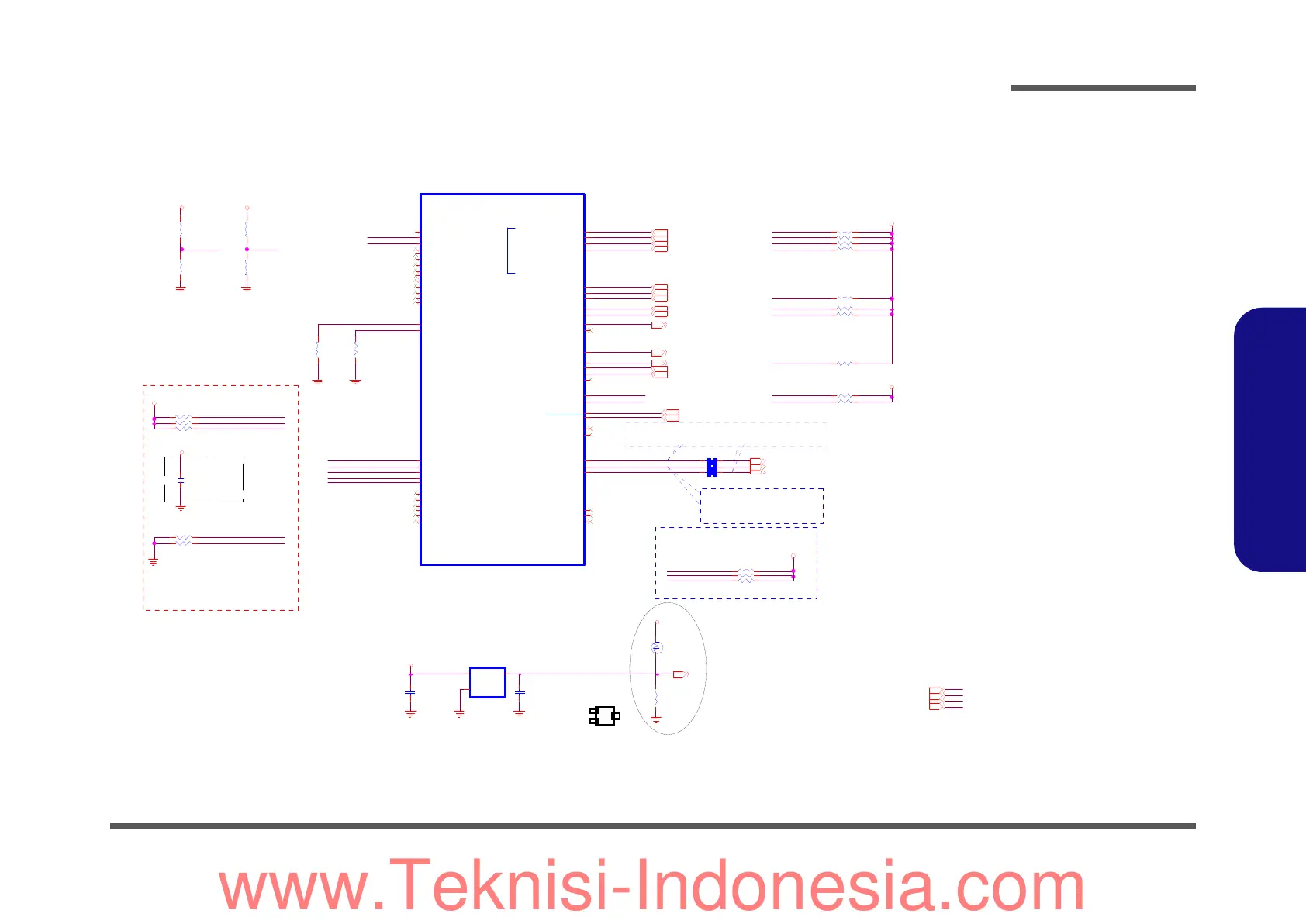

CPU

C EDARVIEW

ICH

4 O F 6

REV = 1.10

U12 D

C D V _22 M M _R E V1 P1 0_5

CPUSLP#

B22

RSVD_N25

N25

RSVD_N24

N24

R SV D _W 26

W26

R SV D _W 25

W25

RSVD_R6

R6

RSVD_R5

R5

TR S T#

B24

TM S

D24

TD O

B25

TD I

C24

TC LK

C25

MV_ GPIO_RCOMP

K23

HV_GPIO_RCOMP

K24

RSVD_H30

H30

R SV D _J 31

J31

R SV D _K 29

K29

R SV D _L 30

L30

R SV D _L 29

L29

R SV D _K 30

K30

RSVD_H27

H27

R SV D _K 27

K27

R SV D _K 26

K26

R SV D _J 28

J28

R SV D _K 25

K25

ST R AP _K 2 8

K28

ST R AP _L 2 7

L27

R SV D _L 26

L26

RSVD_L24

L24

RSVD_L22

L22

RSVD_K21

K21

SVID_DATA

C16

SV I D _C LK

D18

SVID_ALERT#

B16

RSVD_F19

F19

RSVD_E19

E19

HPLL_ REFCLK

K19

H P LL_ R EF C LK _P

J19

PREQ#

G2 9

PRDY#

H29

DBR#

E30

RESET#

G3 0

PWRGOOD

D23

PROCHOT #

A19

PB E #

C20

RSVD_L11

L11

THERMTRIP#

B20

INTR/LINT0 0

D20

INIT #

A23

DPLSLP#

B21

DPRSTP#

C21

STPCLK#

D22

RSVD_C18

C18

NMI/LINT10

C22

SMI#

B18

R 197 11 0_ 1% _ 04

R 1 1 51_ 04

R 188 54 . 9_1 %_0 4

1. 05 VS

1. 05 VS

1. 0 5V S

1. 8V S1. 8V S

1. 05 VS

3. 3V

1. 8V S

H_DPRSTP# 10

H_INTR 9

H_A2 0M# 9

H_SMI# 9

H_PW RGD 1 0

H_STPCLK# 9

H_DPSLP# 10

H_INIT# 9

H_NMI 9

H_FERR# 9

H_THERMTRIP# 9

3. 3 V8, 1 0, 11 ,1 2, 13 , 15, 1 7, 19 ,20,21,22

3. 3 VS3,6,7,8,9,1 0, 1 1 , 12, 1 3, 14 ,15,16,21

1. 0 5V S5,7 , 9, 10 ,11,20,22

H_CPU_ S VI D C LK 22

H_CPU_SVIDALRT# 22

H_CPU_SVIDDAT 22

CLK_CPU_HPL# 7

PLTRST# 10

CLK_CPU_HPL 7

H_PROCHOT# 2 2

H_CPUSLP# 9

TH E R M_VOLT 15

1. 8 VS5, 15 , 21

LAYOUT NOTE:

H_CPUSL P#

Place term ination near CPU

H_INIT#

H_PROCHOT#

H_INT R

H_NMI

H_SMI#

H_A20 M#

H_STPCLK#

H_RSVD_H29

H_T CK

H_T RST#

H_T MS

H_T DI

Thermal IC

H_RSVD_G29

H_RSVD_L27

HV_GPIO_RCOMP

H_RSVD_H29

H_RSVD_K28

MV_GP I O_RCOMP

H_STPCLK#

CAD N ote: H_CP U_SVI DALR T#_R, H_CPU _SVI DDAT_ R

Place the PU r esist ors close to C PU

H_CPU_SVIDDAT_R

C AD No te: H_CPU _SVID CLK_ R

P lace the PU

r esist ors close to V R

H_CPU_SVIDCL K_ R

H_CPU_SVIDALRT#_ R

PROC HOT# m ust be terminated with a 56-O,

pull-up re sis tor to VCCP e ve n if it is no t us ed.

8/30

1:2 (4mils:8mils)

Loading...

Loading...