A3V56S30FTP

A3V56S40FTP

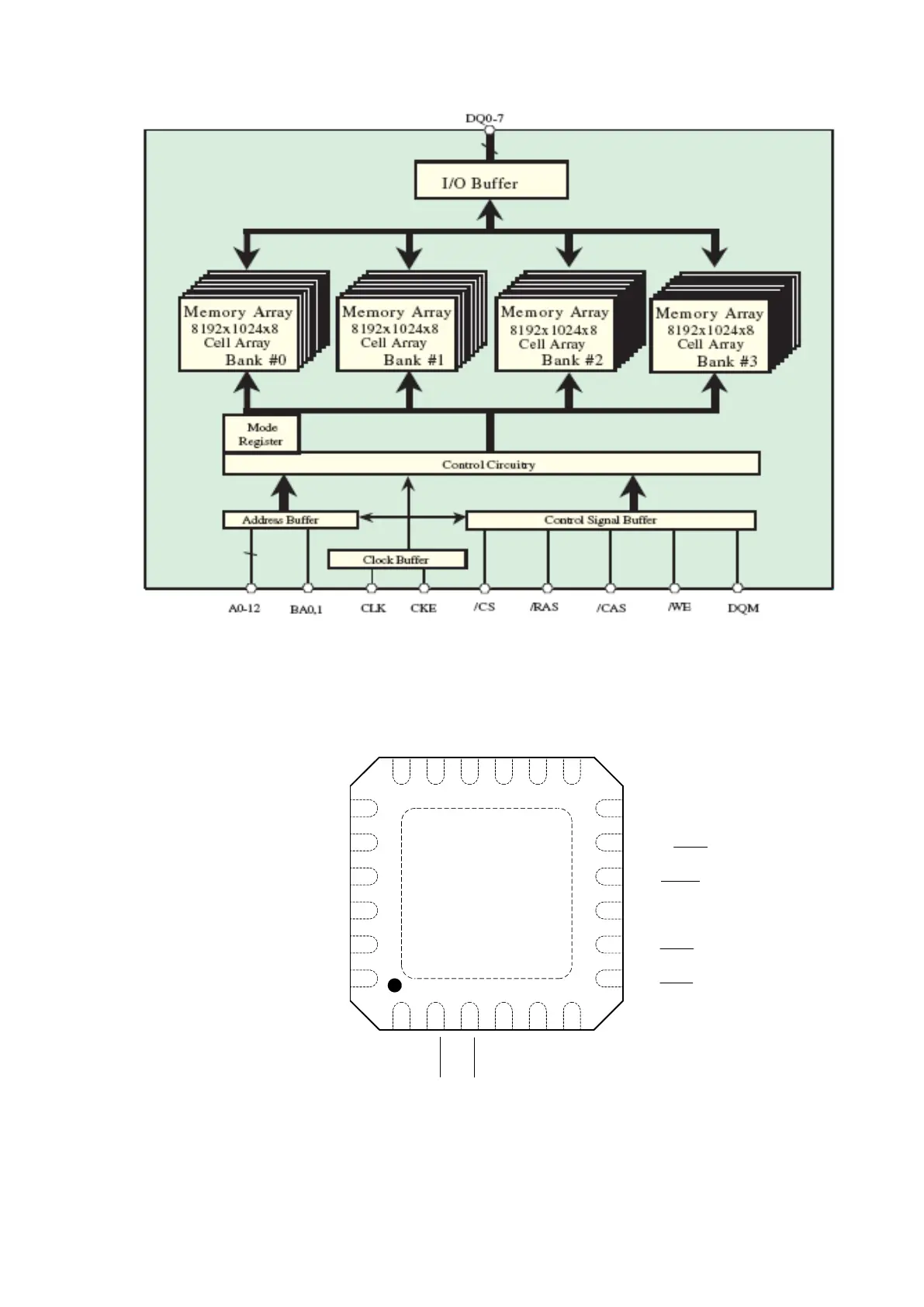

256M Single Data Rate Synchronous DRAM

Revision 1.1 Mar., 2010

Page 3 / 39

Note:This figure shows the A3V56S30FTP

The A3V56S40FTP configuration is 8192x512x16 of cell array and DQ0-15

Type Designation Code

A 3V 56 S40F TP-G6

Speed Grade 75: 133MHz@CL=3

7: 143MHz@CL=3

6: 166MHz@CL=3

G: Green

Package Type TP:TSOP (II)

Process Generation

Function Reserved for Future Use

Organization 2

n

3:x8, 4:x16

SDR Synchronous DRAM

Density 56:256M bits

Interface V:LVTTL

Memory Style (DRAM)

Zentel DRAM

Small Footprint RMII 10/100 Ethernet Transceiver with HP Auto-MDIX Support

Datasheet

SMSC LAN8720A/LAN8720Ai 9 Revision 1.3 (04-20-11)

DATASHEET

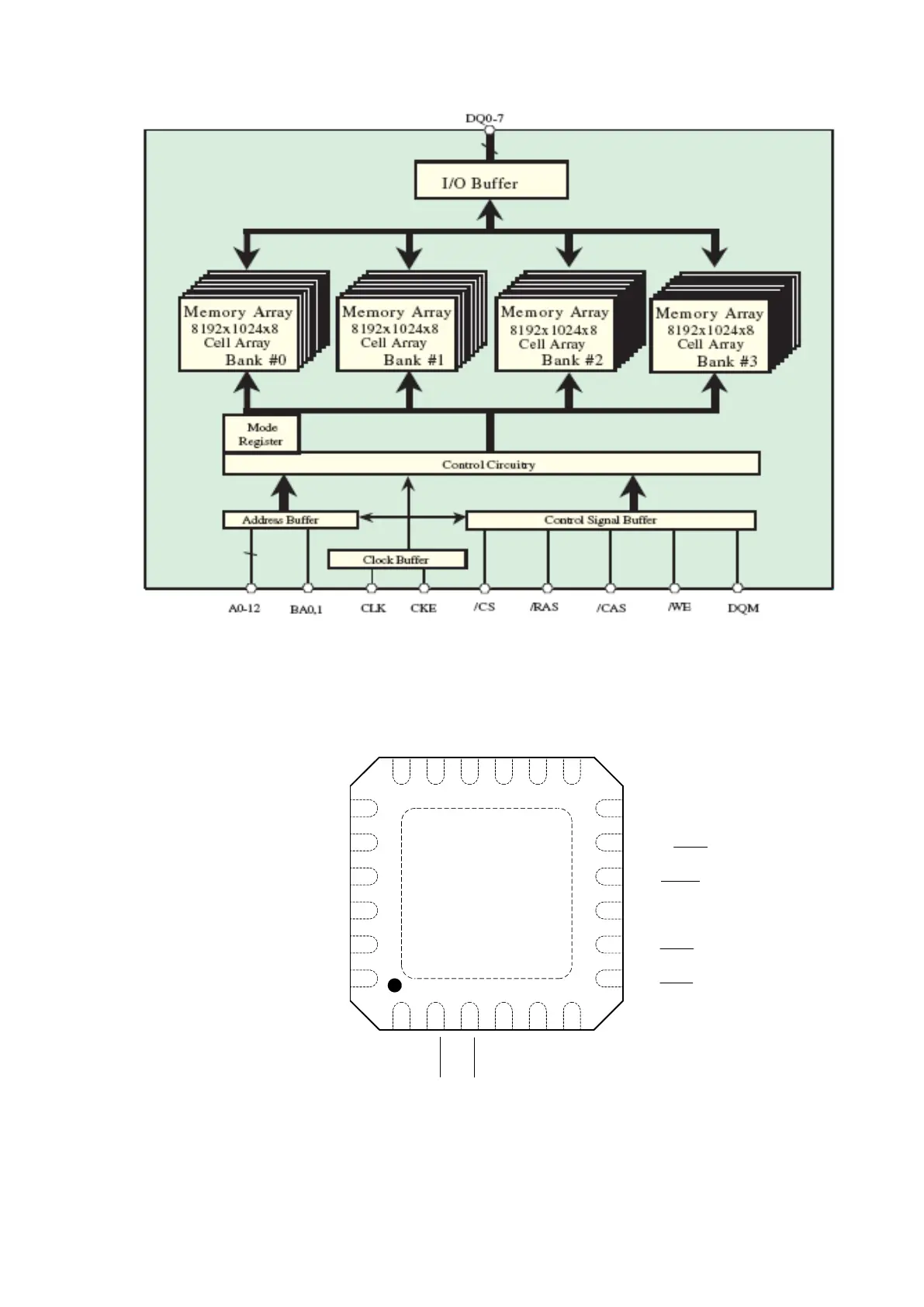

Chapter 2 Pin Description and Configuration

Note: When a lower case “n” is used at the beginning of the signal name, it indicates that the signal

is active low. For example, nRST indicates that the reset signal is active low.

Note: The buffer type for each signal is indicated in the BUFFER TYPE column. A description of the

buffer types is provided in Section 2.2.

Figure 2.1 24-QFN Pin Assignments (TOP VIEW)

Loading...

Loading...