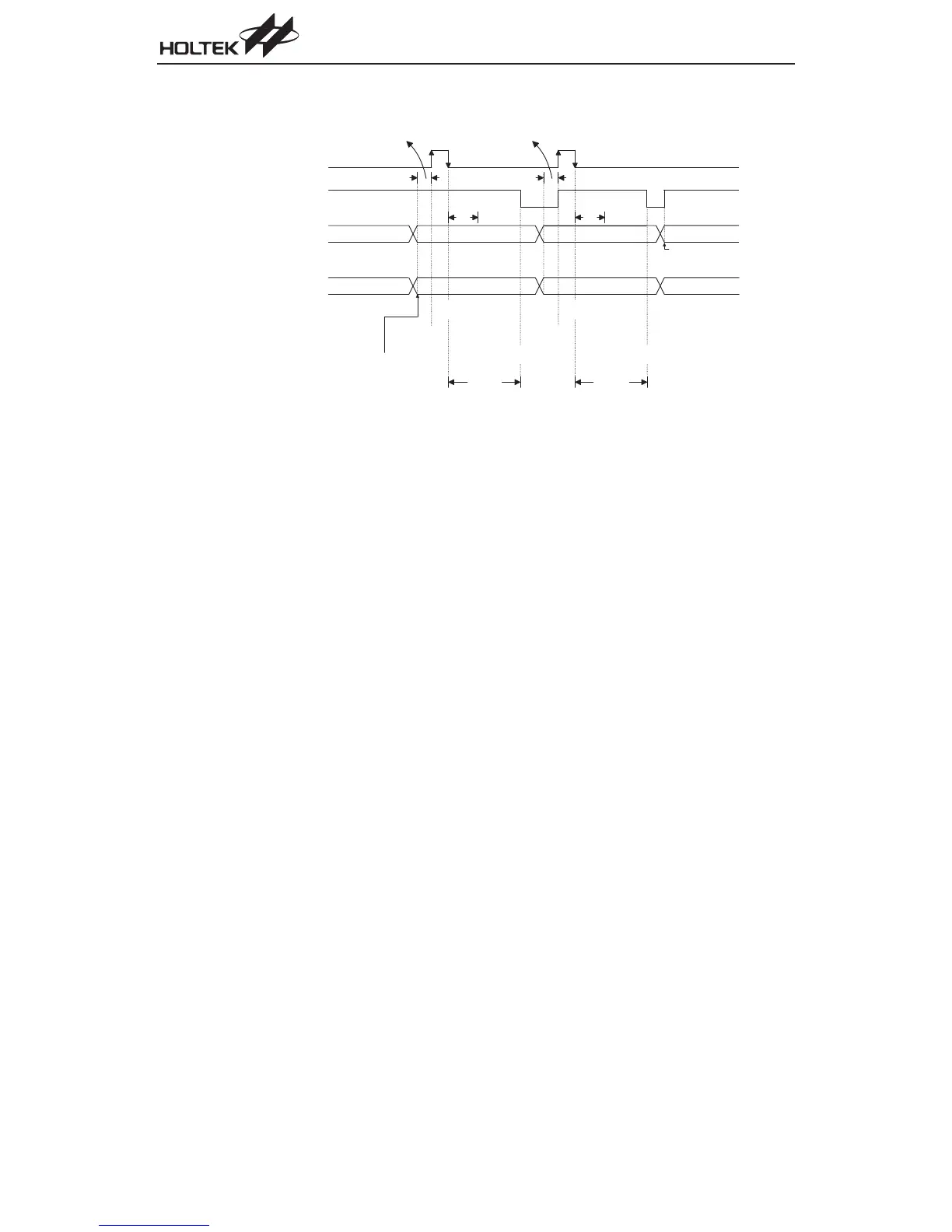

The following timing diagram shows graphically the various stages involved in an analog to digital

conversion process and its associated timing.

The setting up and operation of the A/D converter function is fully under the control of the applica

-

tion program as there are no configuration options associated with the A/D converter. After an A/D

conversion process has been initiated by the application program, the microcontroller internal

hardware will begin to carry out the conversion, during which time the program can continue with

other functions. There are two methods to determine when the A/D conversion process is com-

plete. The first is for the application program to poll the EOCB bit in the ADCR register, while the

second method is to await an A/D internal interrupt to occur. The following two short program ex-

amples illustrate both of these methods. Note that the program is based on the HT46R22/

HT46C22 devices.

Example: using EOCB Polling Method to detect end of conversion

clr INTC0.3 ; disable A/D interrupt in interrupt control

; register

mov a,00100000B

mov ADCR,a ; setup ADCR register to configure Port PB0~PB3

; as A/D inputs and select AN0 to be connected

; to the A/D converter

mov a,00000001B

mov ACSR,a ; setup the ACSR register to select f

SYS

/8 as

; the A/D clock

Start_conversion:

clr ADCR.7

set ADCR.7 ; reset A/D

clr ADCR.7 ; start A/D

Polling_EOC:

sz ADCR.6 ; poll the ADCR register EOCB bit to detect end

; of A/D conversion

jmp polling_EOC ; continue polling

Chapter 1 Hardware Structure

51

7 6 t

A D

A / D c o n v e r s i o n t i m e

7 6 t

A D

A / D c o n v e r s i o n t i m e

0 0 0 B

0 0 0 B

1 0 0 B

0 1 0 B

0 0 0 B

S T A R T

E O C B

P C R 2 ~ P C R 0

A C S 2 ~ A C S 0

P o w e r - o n

R e s e t

E n d o f A / D

c o n v e r s i o n

1 : D e f i n e P B c o n f i g u r a t i o n

2 : S e l e c t a n a l o g c h a n n e l

1 . P B p o r t s e t u p a s I / O s

2 . A / D c o n v e r t e r i s p o w e r e d o f f

t o r e d u c e p o w e r c o n s u m p t i o n

A / D c l o c k m u s t b e f

S Y S

/ 2 , f

S Y S

/ 8 o r f

S Y S

/ 3 2

N o t e :

S t a r t o f A / D

c o n v e r s i o n

R e s e t A / D

c o n v e r t e r

1 0 0 B

0 0 0 B

S t a r t o f A / D

c o n v e r s i o n

R e s e t A / D

c o n v e r t e r

A / D s a m p l i n g t i m e

3 2 t

A D

M i n i m u m o n e i n s t r u c t i o n c y c l e n e e d e d

d o n ' t c a r e

A / D s a m p l i n g t i m e

3 2 t

A D

E n d o f A / D

c o n v e r s i o n

A/D Conversion Timing

Loading...

Loading...