counter to give longer watchdog time-outs. In the case of the HT46R47/HT46C47 devices, this divi

-

sion ratio is fixed by an internal counter which gives a 2

15

fixed division ratio. In the case of the

other devices, the division ratio can be varied by selecting different configuration options to give a

2

12

to 2

15

division ratio range. As the clear instruction only resets the last stage of the counter

chain, for this reason the actual division ratio and corresponding WDT time-out can vary by a fac

-

tor of two. The exact division ratio depends upon the residual value in the WDT counter before the

clear instruction is executed. As an example, if a WDT time out value of 2

12

(4096) is chosen in the

configuration options, the actual time out value can range from f

S

/2

12

to f

S

/2

13

, where f

S

represents

the WDT clock source. As mentioned earlier this clock source can come from either the internal

WDT oscillator or from the system clock divided by four.

If the instruction clock is used as the clock source, it should be noted that when the system enters

the power-down mode, then the instruction clock is stopped and the WDT will lose its protecting

purposes. In such cases, the system can only be restarted via external logic. For systems that op

-

erate in noisy environments, using the internal WDT oscillator is strongly recommended.

Under normal program operation, the WDT time-out will initialize a ²chip reset² and set the status

bit ²TO². However, if the system is in the power-down mode, only a WDT time-out reset from ²HALT²

will be initialized which will only reset the Program Counter and SP. Three methods can be adopted

to clear the contents of the WDT. The first is an external hardware reset (a low level on the RES

pin),

the second is via software instructions and the third is via a ²HALT² instruction. There are two meth

-

ods of using software instructions to clear the Watchdog Timer, one of which must be chosen by con

-

figuration option. The first option is to use the single ²CLR WDT² instruction while the second is to

use the two commands ²CLR WDT1² and ²CLR WDT2². For the first option, a simple execution of

²CLR WDT² will clear the WDT while for the second option, both ²CLR WDT1² and ²CLR WDT2²

must both be executed to successfully clear the WDT. Note that for this second option, if ²CLR

WDT1² is used to clear the WDT, successive executions of this instruction will have no effect, only

the execution of a ²CLR WDT2² instruction will clear the WDT. Similarly after the ²CLR WDT2² in-

struction has been executed, only a successive ²CLR WDT1² instruction can clear the Watchdog

Timer.

Note

1. The 4-to-1 configuration option to select f

S

/2

12

,f

S

/2

13

,f

S

/2

14

or f

S

/2

15

is not applicable in the

HT46R47/HT46C47, which has a fixed f

S

/2

15

division ratio.

2. Because only the last stage of counter chain is cleared by instructions, the WDT time-out period

varies. As an example, the selected value of 2

16

/f

S

may range from 2

16

/f

S

to 2

15

/f

S.

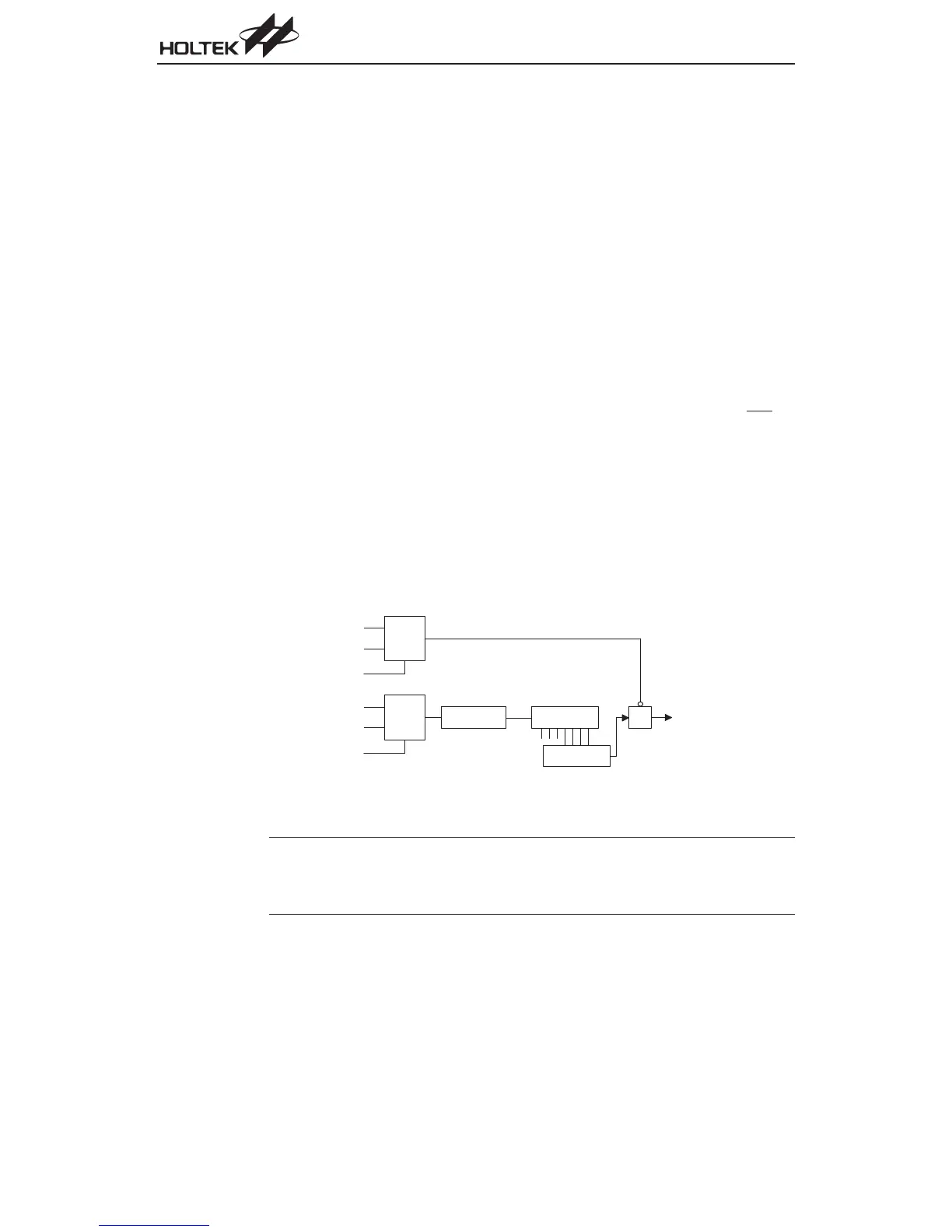

Chapter 1 Hardware Structure

75

C o n f i g .

O p t i o n

S e l e c t

W D T S o u r c e S e l e c t

C o n t r o l

L o g i c

C L R W D T 1 F l a g

C L R W D T 2 F l a g

1 o r 2 I n s t r u c t i o n s

f

S Y S

/ 4

W D T O S C O u t p u t

8 - b i t D i v i d e r

f

S

C L R

W D T T i m e - o u t

( 2

1 3

/ f

S

, 2

1 4

/ f

S

, 2

1 5

/ f

S

o r 2

1 6

/ f

S

)

¸

2

7 - b i t P r e s c a l e r

f

S

/ 2

8

f

S

/ 2

1 2

, f

S

/ 2

1 3

, f

S

/ 2

1 4

o r f

S

/ 2

1 5

C o n f i g O p t i o n

Watchdog Timer

Loading...

Loading...