Rev. 2.50 204 June 22, 2017 Rev. 2.50 205 June 22, 2017

HT66F20/HT66F30/HT66F40/HT66F50/HT66F60

HT66FU30/HT66FU40/HT66FU50/HT66FU60

A/D Flash MCU with EEPROM

HT66F20/HT66F30/HT66F40/HT66F50/HT66F60

HT66FU30/HT66FU40/HT66FU50/HT66FU60

A/D Flash MCU with EEPROM

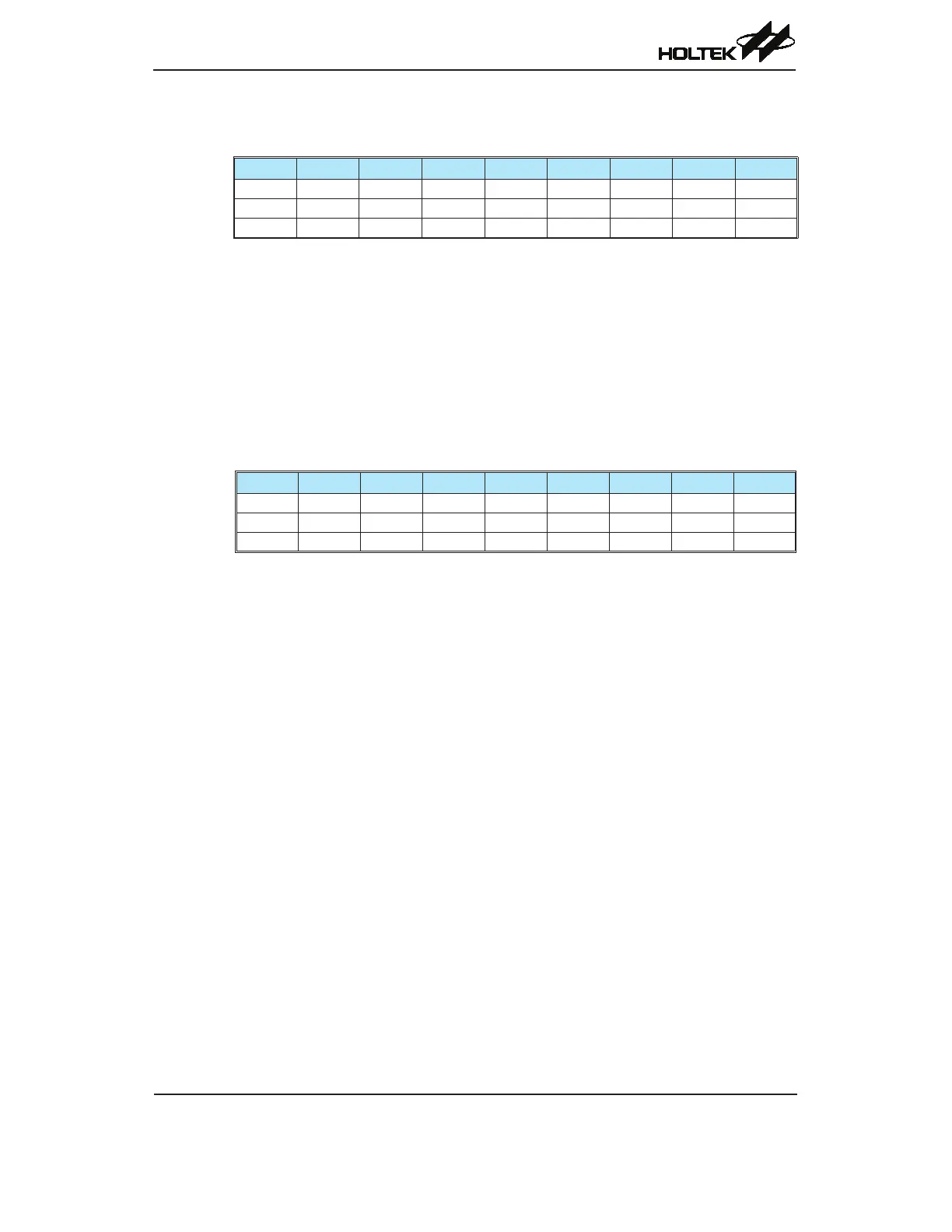

INTEG Register

• HT66F20/HT66F30/HT66F40/HT66F50

Bit 7 6 5 4 3 2 1 0

Name — — — —

INT1S1 INT1S0 INT0S1 INT0S0

R/W — — — — R/W R/W R/W R/W

POR — — — — 0 0 0 0

Bit7~4 Unimplemented,readas“0”

Bit3~2 INT1S1, INT1S0:InterruptedgecontrolforINT1pin

00:Disable

01:Risingedge

10:Fallingedge

11:Risingandfallingedges

Bit1~0 INT0S1, INT0S0:InterruptedgecontrolforINT0pin

00:Disable

01:Risingedge

10:Fallingedge

11:Risingandfallingedges

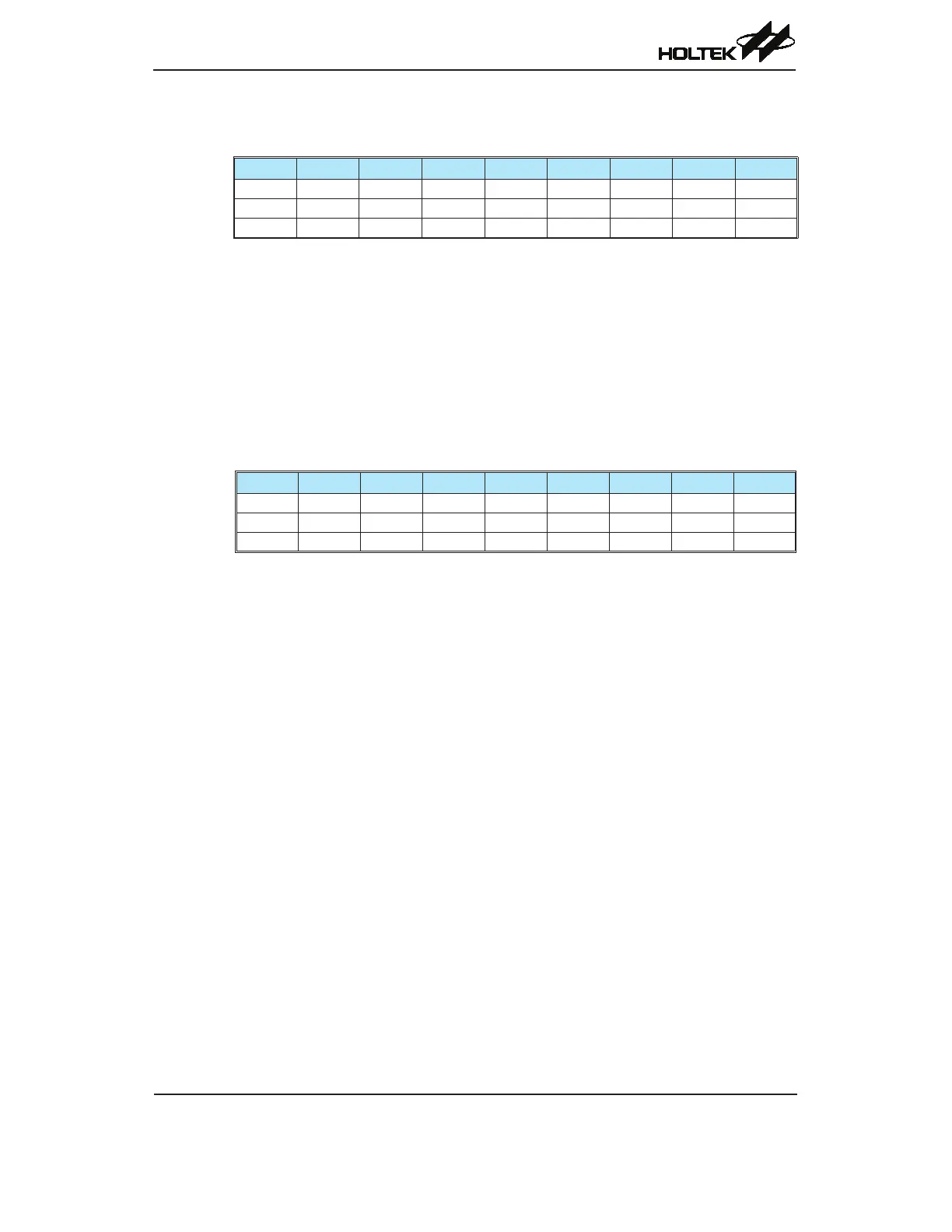

• HT66F60

Bit 7 6 5 4 3 2 1 0

Name

INT3S1 INT3S0 INT2S1 INT2S0 INT1S1 INT1S0 INT0S1 INT0S0

R/W R/W R/W R/W R/W R/W R/W R/W R/W

POR 0 0 0 0 0 0 0 0

Bit7~6 INT3S1, INT3S0:InterruptedgecontrolforINT3pin

00:Disable

01:Risingedge

10:Fallingedge

11:Risingandfallingedges

Bit5~4 INT2S1, INT2S0:InterruptedgecontrolforINT2pin

00:Disable

01:Risingedge

10:Fallingedge

11:Risingandfallingedges

Bit3~2 INT1S1, INT1S0:InterruptedgecontrolforINT1pin

00:Disable

01:Risingedge

10:Fallingedge

11:Risingandfallingedges

Bit1~0 INT0S1, INT0S0:InterruptedgecontrolforINT0pin

00:Disable

01:Risingedge

10:Fallingedge

11:Risingandfallingedges

Loading...

Loading...