44

4.7.3 Tracing and Registers

When a debug log has been established, tracing may be configured by specifying one or more of the reporting level

options:

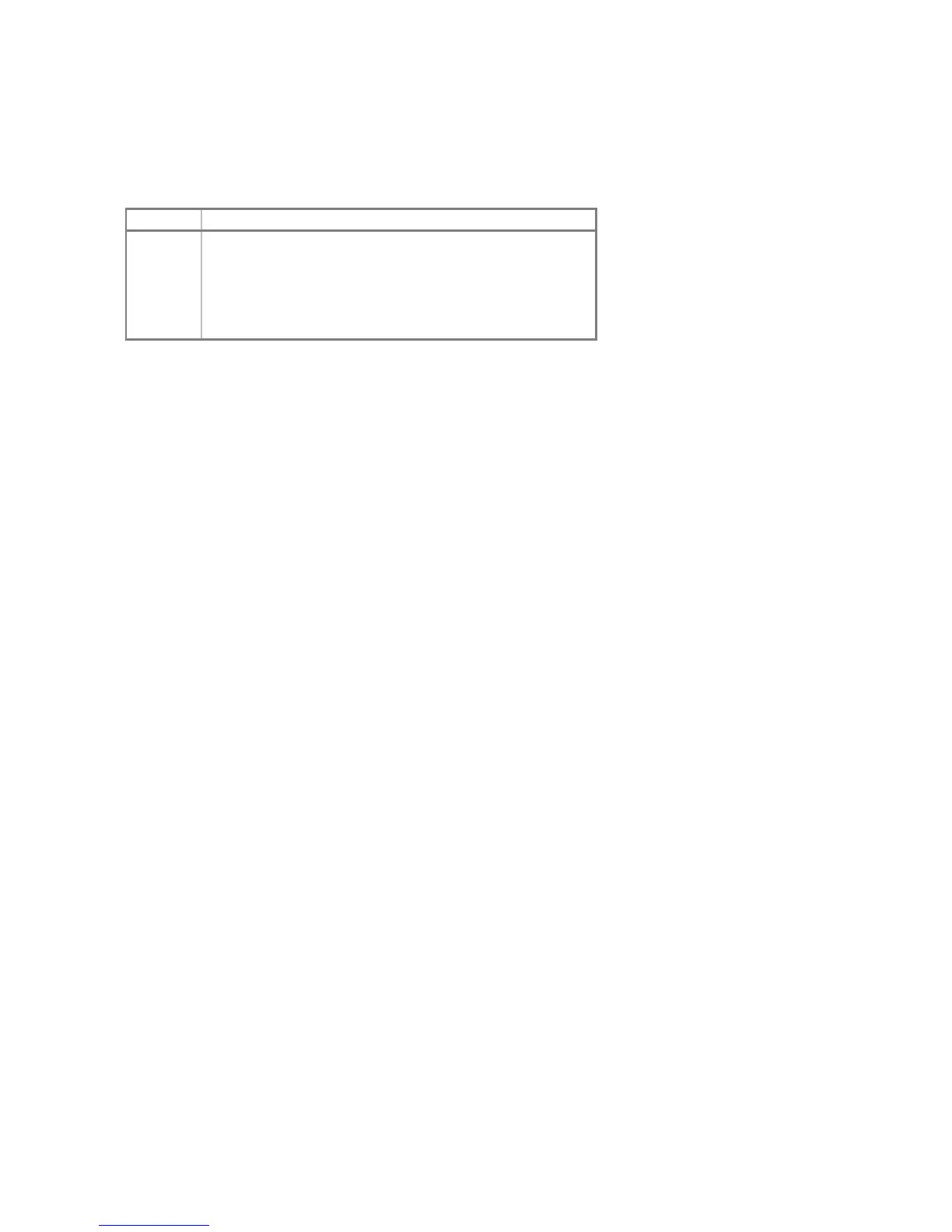

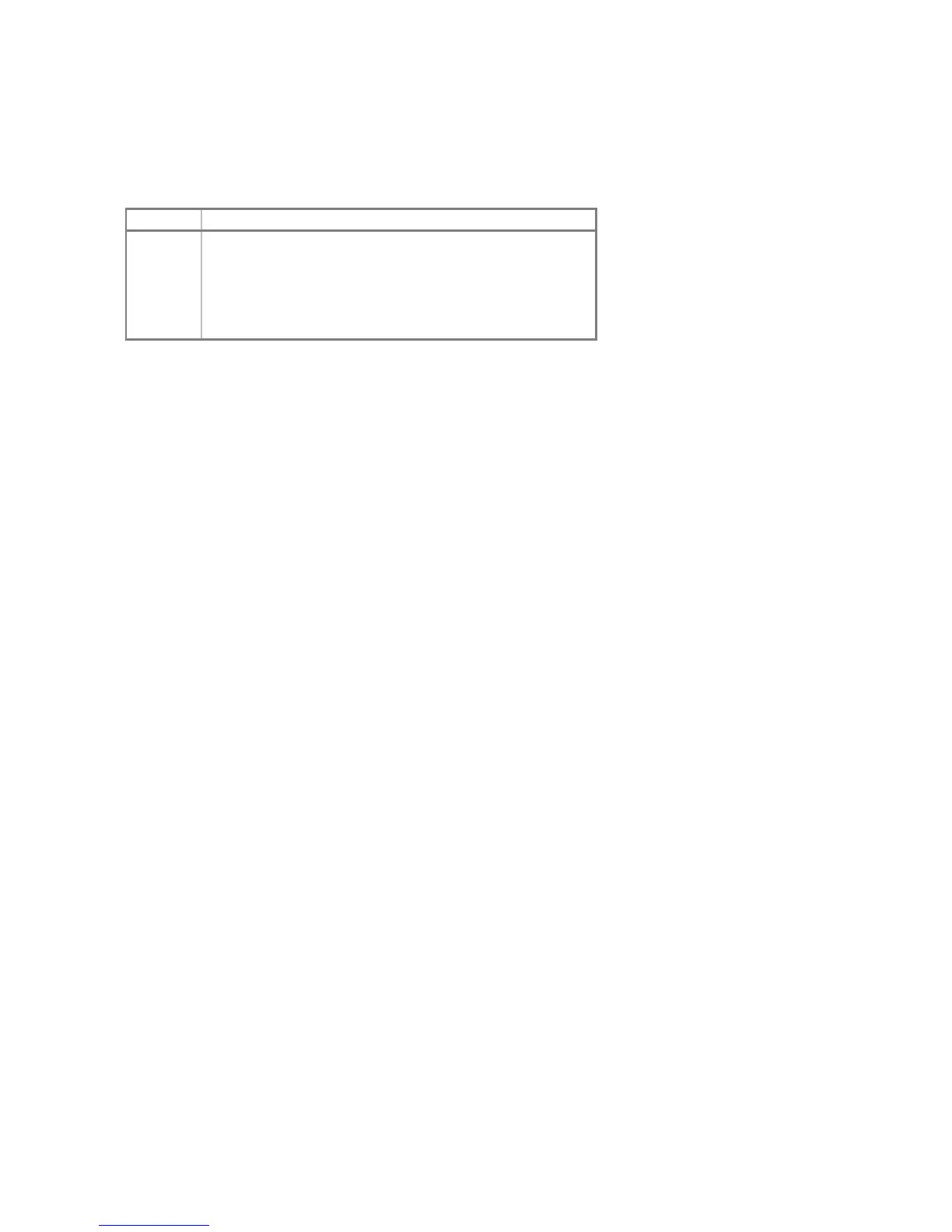

Option Reporting Level

CMDS

Command initiations and completions

CPU

Words received from and sent to the CPU

BUF

Data read from and written to the channel buffers

XFER

Data receptions and transmissions

IOBUS

I/O bus signals and data words received and returned

The CMDS option traces the commands executed by the multiplexer. The CPU option traces words received from

(control and write data) and sent to (status and read data) the CPU. The BUF option traces reads and writes from

the internal channel buffers. The XFER option traces the characters sent and received from the multiplexer

channels. The IOBUS option traces the I/O backplane signals and data received and returned via the interface.

Examples of the trace formats follow:

>>MPX cmds: [OTx] Command 037 parameter 100000 scheduled, time = 1250

>>MPX cpu: [Lix,C] Status = 102000

>>MPX buf: Port 2 character 'A' get from read buffer [73]

>>MPX xfer: Port 0 character LF transmitted

>>MPX iobus: Received data 000000 with signals STF

Loading...

Loading...