5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

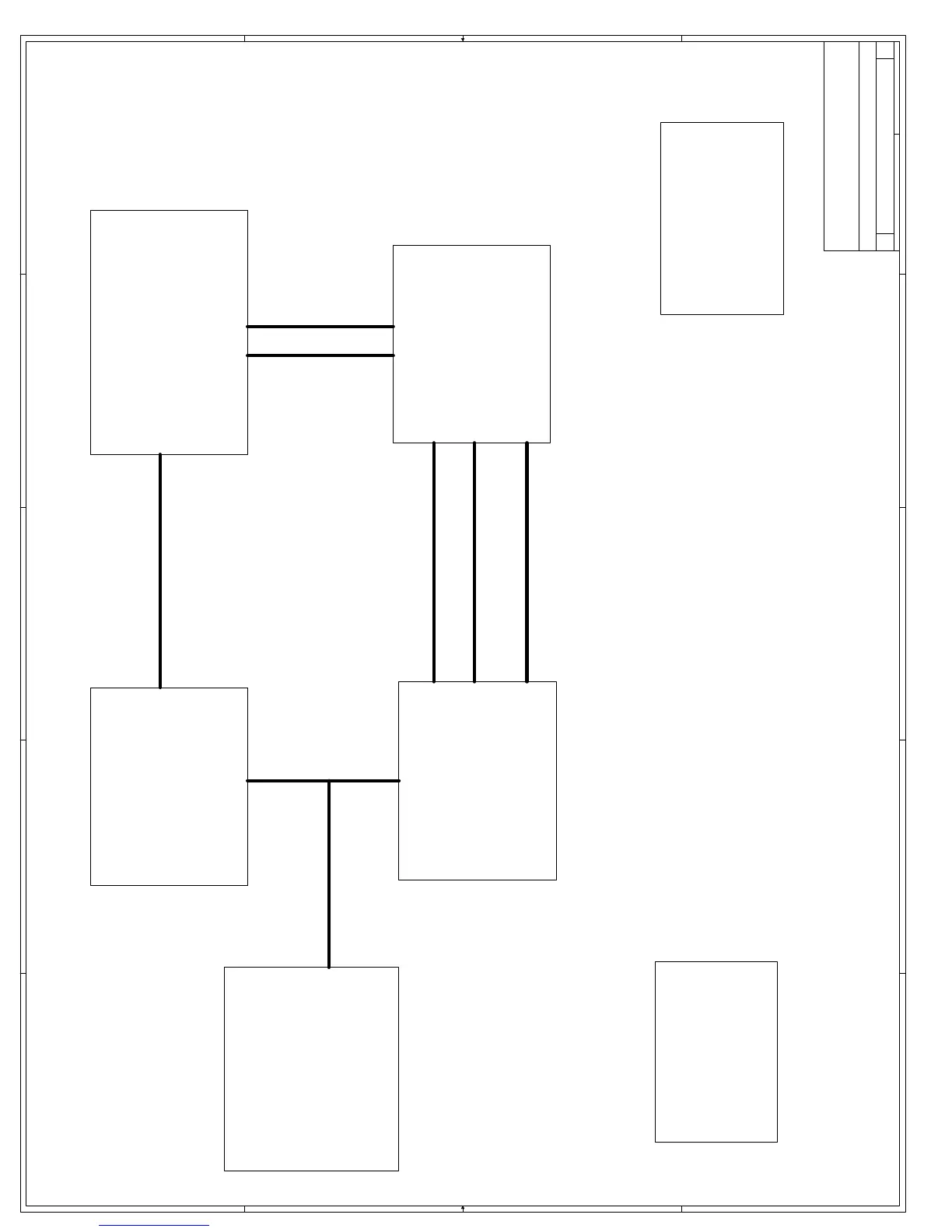

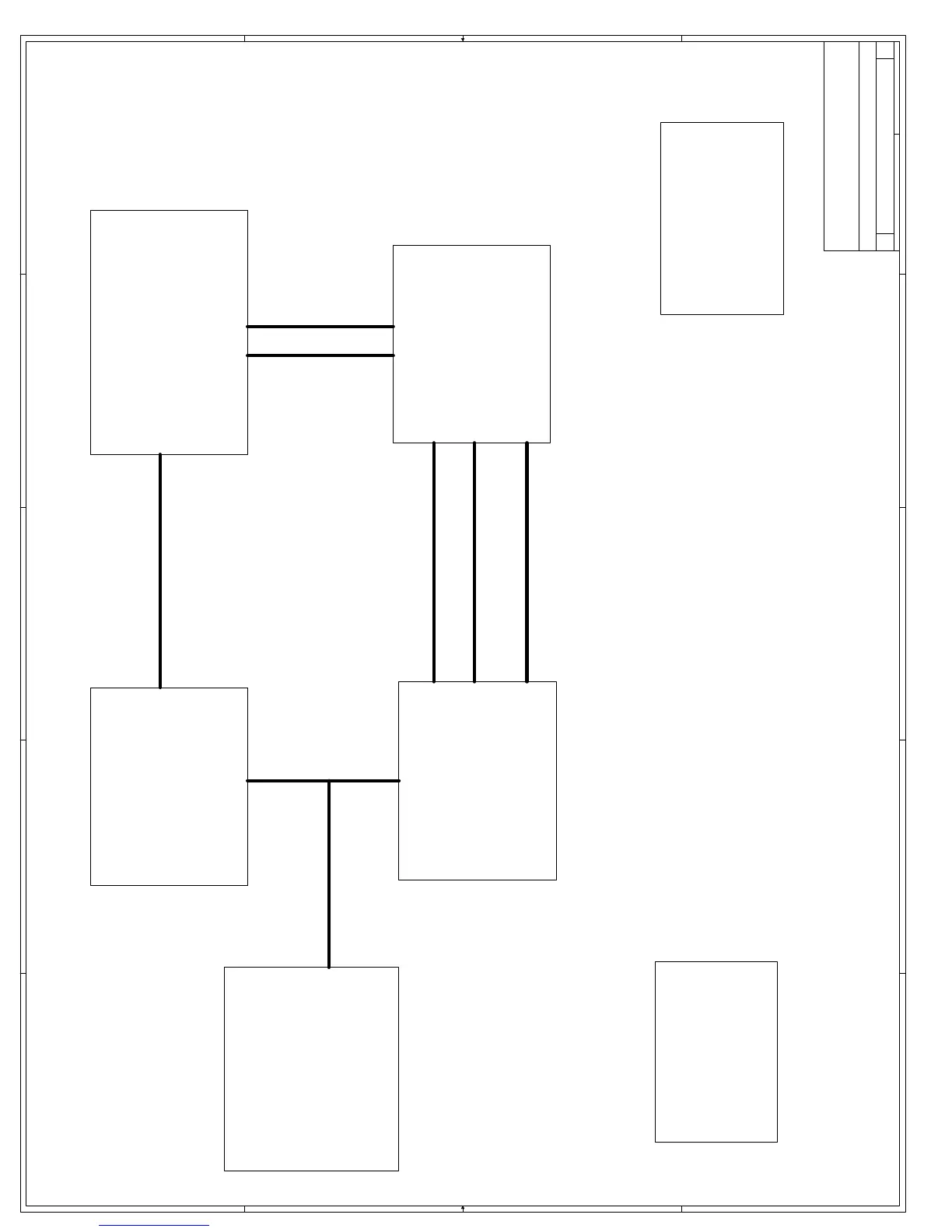

Socket

370-256

Page 3,4,5

440BX

Page

6,7

CPU

Connector

Page 8

GTL+

Termination

Page 9

GTL+

ITP

Bus Ratio

Logic Thermal

Sensor Page

10

Voltage

Regulator

Page 11

THIS SCHEMATIC IS PROVIDED "AS IS" WITH NO

WARRANTIES WHATSOEVER, INCLUDING ANY

WARRANTY OF MERCHANTABILITY, FITNESS FOR

ANY PARTICULAR PURPOSE, OR ANY WARRANTY

OTHERWISE ARISING OUT OF PROPOSAL,

SPECIFICATION OR SAMPLE.

SDRAM

Interface

PCI Bus

AGP Bus

SMBus

Layout

Guidelines

Page 12

Intel(R) 440BX Scalable Performance Board A3

Diagram

Embedded Intel Architecture Division

Intel Corporation

5000 W. Chandler Blvd

Chandler AZ, 85044

C

212Wednesday, April 26, 2000

Title

Size Document Number Rev

Date: Sheet

of

Loading...

Loading...