5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

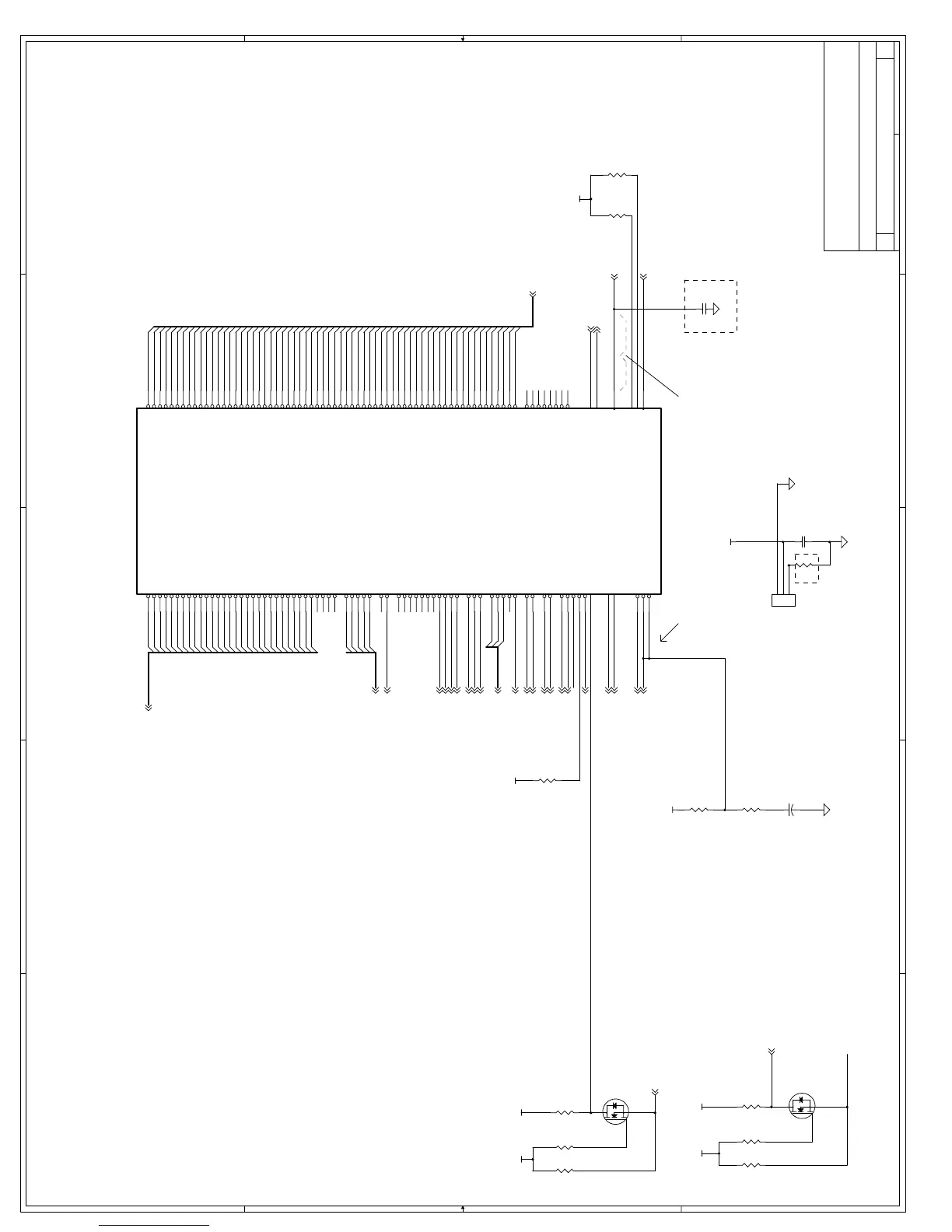

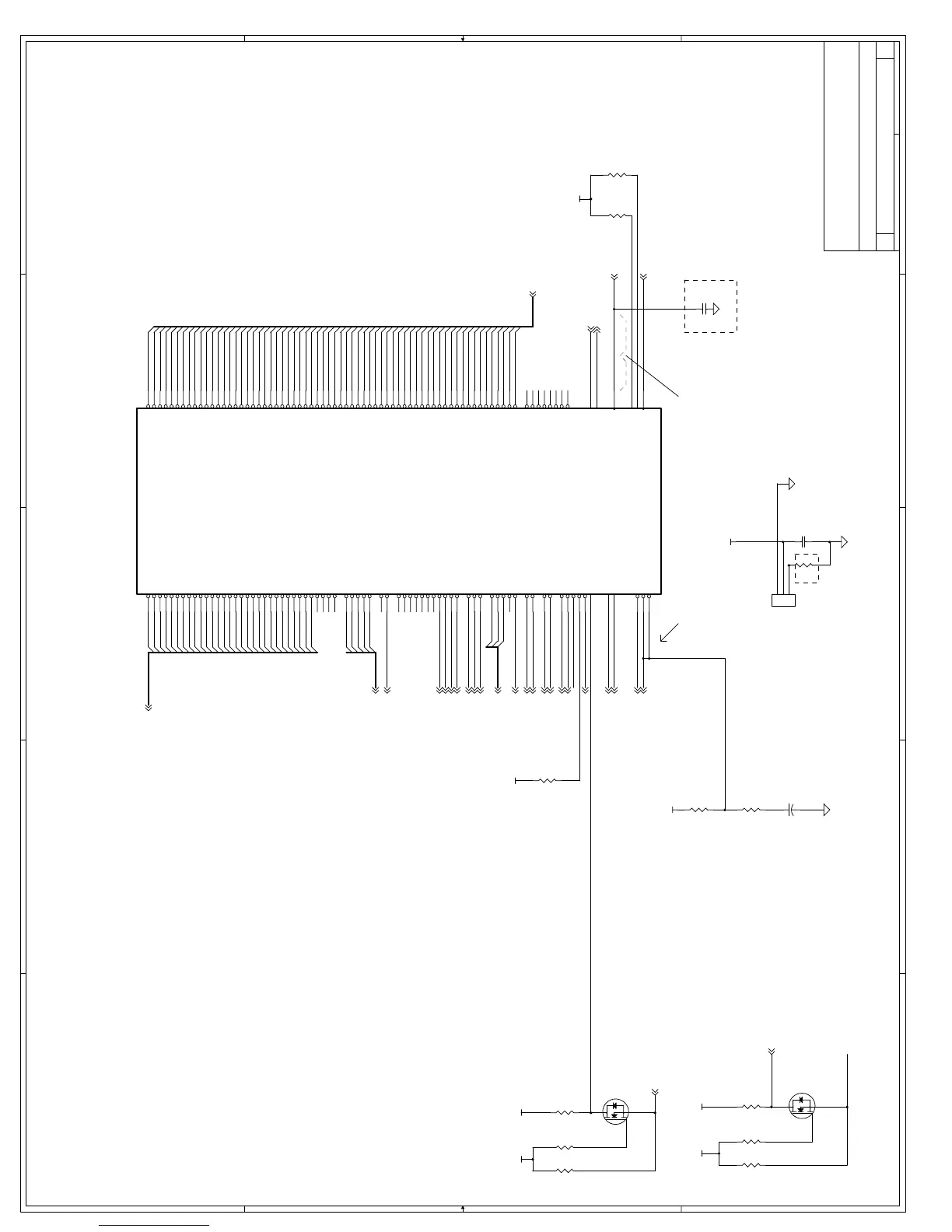

CMOS voltage conversion logic

20 pF necessary to correct

for 443BX Clock loading.

CPU Fan Connector

Do Not Populate

length of trace to 86 ohm must be

between 0.5",1.5"

length of HRESET trace from

CPU to BX/CPU/ITP node must

be between 0.5",1.5"

Pins AH4,X4 must be daisy

chained

convert PWROK signal from 3.3V to 2.5V

capacitor site on BCLK must be

within 0.5" from socket370

Fairchild: 25V, ID=250uA@VGS=0.85V typ, 1.5V max

Fairchild: 25V, ID=250uA@VGS=0.85V typ, 1.5V max

DO NOT POPULATE

>>LAYOUT: Silkscreen. Number

socket-370 on top and bottow

layer.

0 ohm

A3

S370-256 Host Interface

Embedded Intel Architecture Division

Intel Corporation

5000 W. Chandler Blvd

Chandler AZ, 85044

C

312Wednesday, April 26, 2000

Intel(R) 440BX Scalable Performance Board

Title

Size Document Number Rev

Date: Sheet

of

HA#26

HA#8

RS#1

HREQ#2

HA#7

HREQ#3

HA#28

HA#20

HA#9

HA#18

HA#5

HREQ#4

HA#27

HA#23

HA#15

HA#14

HA#4

HA#3

HA#22

HA#24

HA#11

HA#21

HA#17

HA#12

HREQ#1

HA#10

FERR#_CPU

HA#30

HREQ#0

HA#31

HA#25

HA#13

HA#6

RS#2

RS#0

HA#29

HA#19

HA#16

FERR#_CPU

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HA#[31:3]6,9

HREQ#[4:0]6,9

ADS#6,9

BREQ#6,9

BPRI#6,9

BNR#6,9

HLOCK#6,9

HIT#6,9

HITM#6,9

DEFER#6,9

RS#[2:0]6,9

HRESET#6,10

HTRDY#6,9

DBSY#6,9

DRDY#6,9

THERMDN 10

THERMDP 10

HCLK0 8

PICCLK 8

FERR# 8

INIT#8

SMI#8

SLP#8

STPCLK#8

PWROK_GEN 6,8

A20M#_CPU10

INTR_CPU10

NMI_CPU10

IGNNE#_CPU10

HD#[63:0] 6,9

VCC_CMOS

V3_3VCC_CMOS

v12_0

VTT

VCC_CMOS

V3_3 V2_5

J1

CON3

1

2

3

C147

0.1uF

R87

1.5K

R7

270

R6

270

R88

10K

R86

1.5K

R105

280 ohm

R81

330 ohm

R107

1.5K

R106

1.5K

Pentium(r) III

Host Interface

Socket 370

U1A

S370-25 6

W1

T4

N1

M6

U1

S3

T6

J1

S1

P6

Q3

M4

Q1

L1

N3

U3

H4

R4

P4

H6

L3

G1

F8

G3

K6

E3

E1

F12

A5

A3

J3

C5

F6

C1

C7

B2

C9

A9

D8

D10

C15

D14

D12

A7

A11

C11

A21

A15

A17

C13

C25

A13

D16

A23

C21

C19

C27

A19

C23

C17

A25

A27

E25

F16

AK8

AH12

AH8

AN9

AL15

AH10

AL9

AH6

AK10

AN5

AL7

AK14

AL5

AN7

AE1

Z6

AG3

AC3

AJ1

AE3

AB6

AB4

AF6

Y3

AA1

AK6

Z4

AA3

AD4

AK18

AH16

AH18

AL19

AL17

AH26

AH22

AK28

AN31

AH14

AN29

AL27

AN27

AL25

AL23

AK20

AN17

AN19

AN25

AH4

AE33

AE37

AG37

AG33

M36

L37

AK26

AJ35

AH30

AG35

AC35

AE35

W37

J33

J35

L35

AL29

AL31

W3

X6

AC1

AF4

C33

C31

A33

A31

E31

C29

E29

A29

AN23

AK24

AL11

AN13

V4

B36

AC37

X2

X4

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

RS#0

RS#1

RS#2

ADS#

BNR#

BR0#

DBSY#

DRDY#

HIT#

HITM#

LOCK#

BPRI#

DEFER#

TRDY#

RESET#

A20M#

FLUSH#

IGNNE#

INIT#

LINT0/INTR

LINT1/NMI

PWRGOOD

SMI#

SLP#

STPCLK#

FERR#

IERR#

BCLK

PICCLK

PICD0

PICD1

THERMDN

THERMDP

A#34

A#32

A#33

A#35

DEP0#

DEP1#

DEP2#

DEP3#

DEP4#

DEP5#

DEP6#

DEP7#

RP#

AERR#

AP0#

AP1#

BERR#

BINIT#

RSP#

BR1#

RESET2#

C150

10 pf

R103 22 ohm

R102

86 ohm 1%

R89

EMPTY

Q1

FDV301N

1

32

Q2

FDV301N

1

32

C1

EMPTY

Loading...

Loading...