XV-N5SL

37

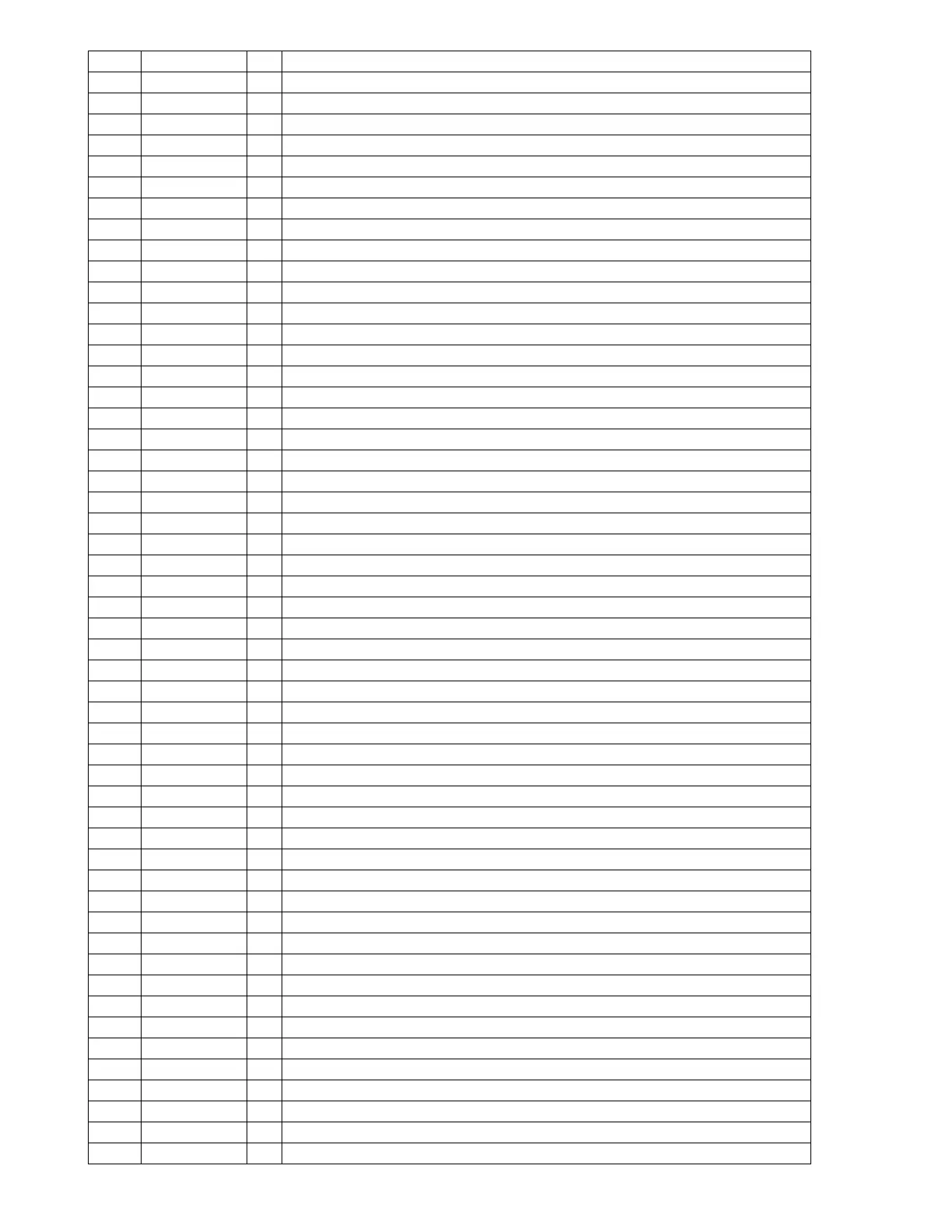

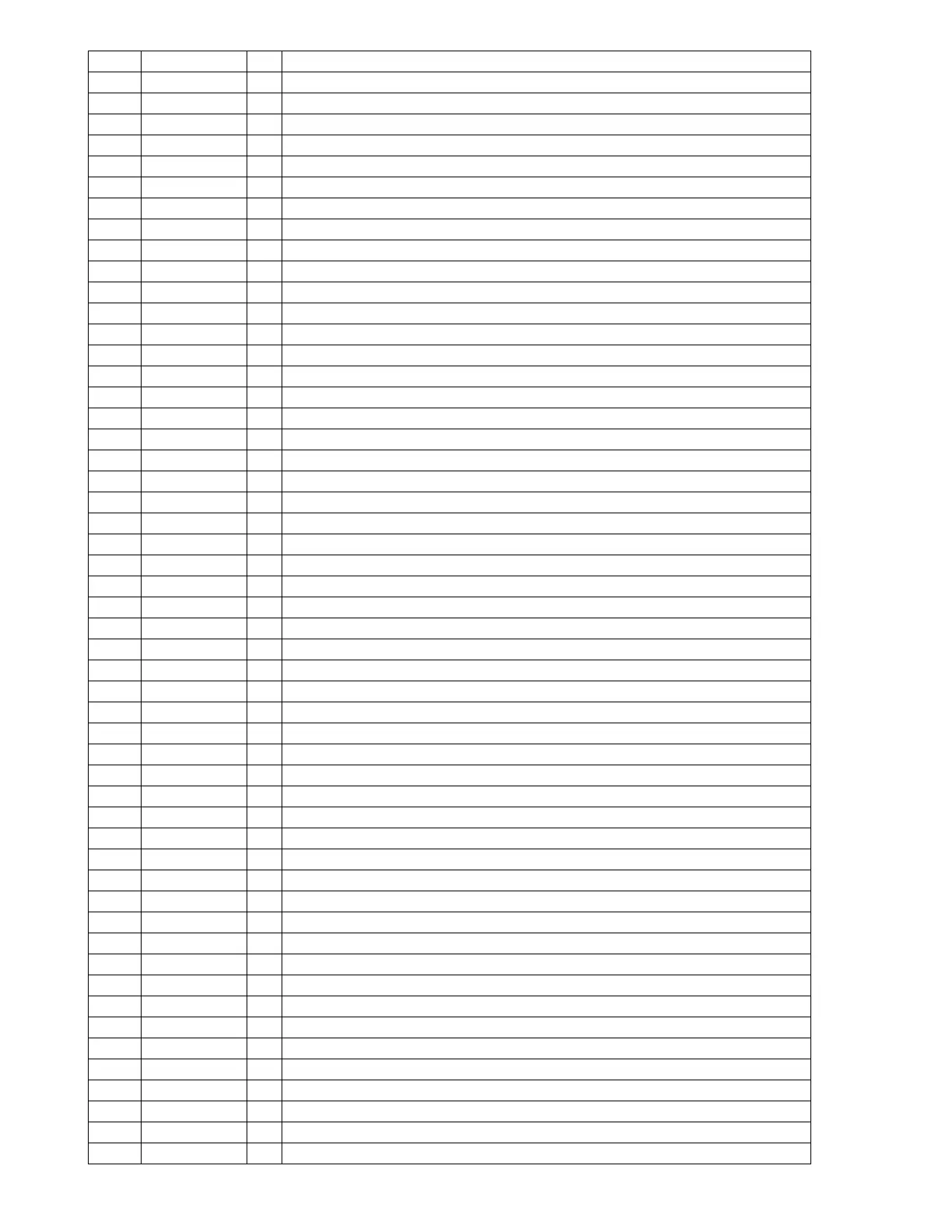

5.9.4 Pin function (MN103S28EGA : 2/4)

Pin No. Symbol I/O Description

36 NRD I Read signal input from system controller

37~44 CPUDT7~0 I/O System control data

45 CLKOUT1 - Non connect

46 MMOD I Test mode switch signal

47 NRST I System reset

48 MSTPOL I Master terminal polarity switch input

49 SCLOCK - Non connect

50 SDATA - Non connect

51 OFTR I Off track signal input

52 BDO I Drop out signal input

53~56 PWM1~4 - Non connect

57 VDD3 - Power supply terminal for I/O (3.3V)

58 DRAMVDD18 - Power supply terminal for DRAM (1.8V)

59 DRAMVSS - Connect to ground for DRAM

60 VSS - Connect to ground

61~64 PWM5~8 - Non connect

65 TBAL O Tracking balance adjustment output

66 FBAL O Focus balance adjustment output

67 TRSDRV O Traverse drive output

68 SPDRV O Spindle drive output

69 FG I Motor FG input

70 TILTP - Non connect

71 TILT - Non connect

72 TILTN - Non connect

73 TX O Digital output signal

74 DTRD - Non connect

75 IDGT - Non connect

76 VDD18 - Power supply terminal for I/O (1.8V)

77 VSS - Connect to ground

78 VDD3 - Power supply terminal for I/O (3.3V)

79 OSCI1 I Oscillation input 16.9MHz

80 OSCO1 O Oscillation output 16.9MHz

81 VSS - Connect to ground

82 TSTSG O Calibration signal

83 VFOSHORT O VFO short output

84 JLINE O J-line setting output

85 AVSSD - Connect to ground for analog circuit

86 ROUT - Non connect

87 LOUT - Non connect

88 AVDD - Power supply terminal for analog circuit (3.3V)

89 VCOF I JFVCO control voltage

90 TRCRS I Input signal for track cross formation

91 CMPIN - Non connect

92 LPFOUT - Non connect

93 LPFIN I Pull-up to VHALF

94 AVSS - Connect to ground for analog circuit

95 HPFOUT - Non connect

96 FPFIN I HPF input

97 CSLFLT I Pull-up to VHALF

98 RFDIF - Non connect

99 AVDDC - Power supply terminal for analog circuit (3.3V)

100 PLFLT2 I Connect to capacitor 2 for PLL

Loading...

Loading...