MELSEC-

10. PROGRAMMING

10 - 33

*

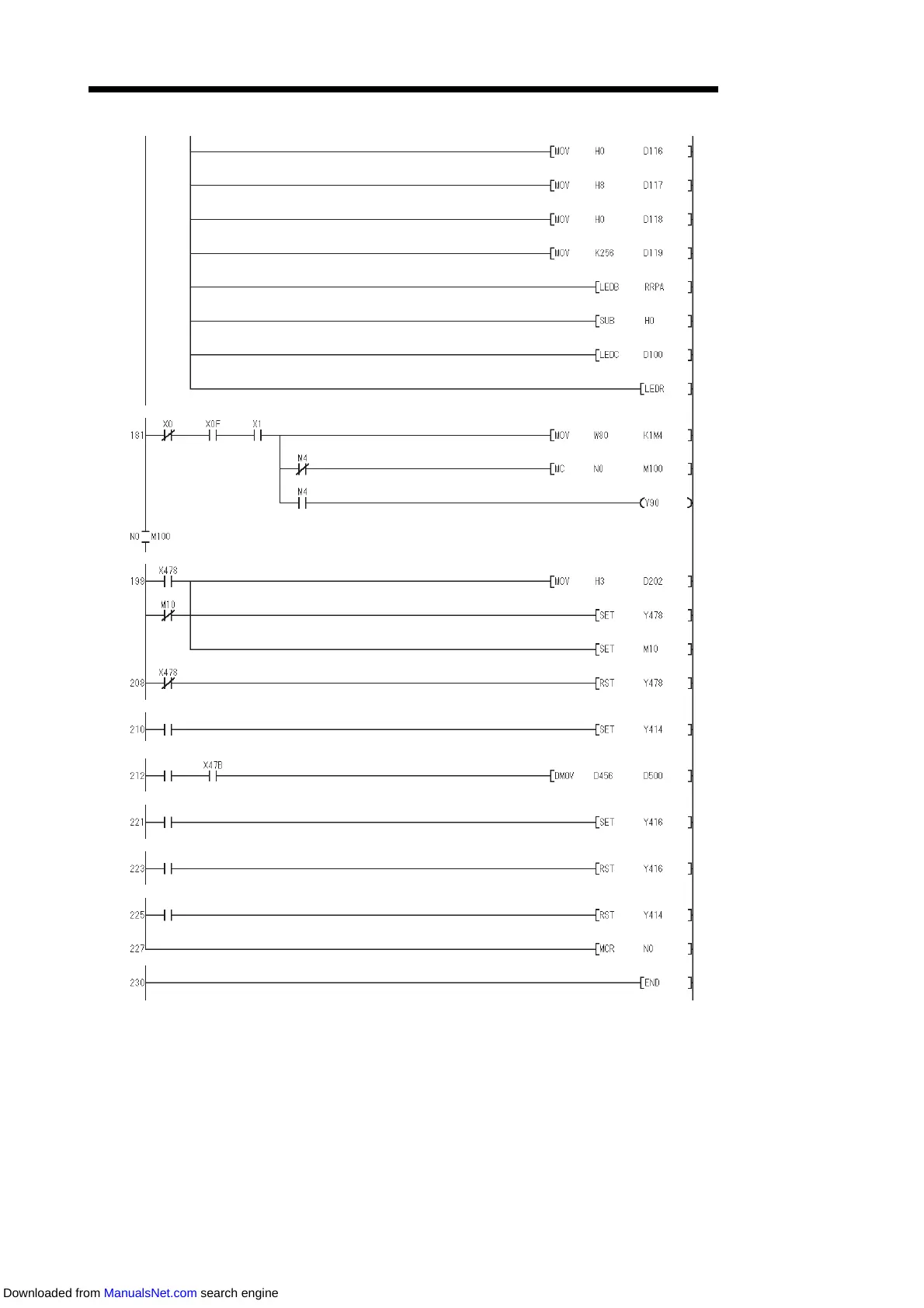

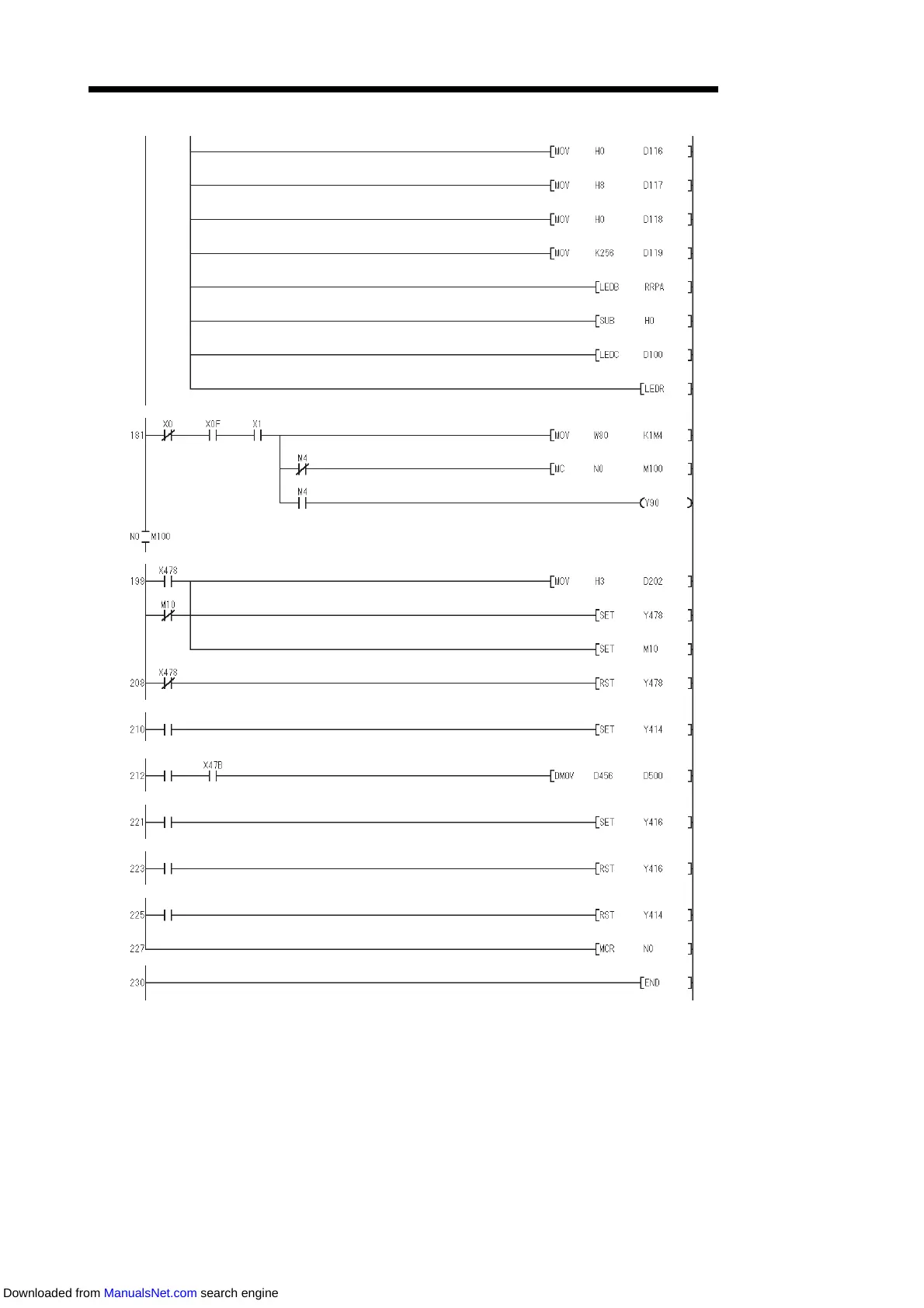

* When the programmable controller CPU is reset, the pulse input mode/function selection register/external output hold-clear settings are reset.

Start of counting

Execution of count disable

Stop of count disable

Stop of counting

SW head number is set.

"W" is set.

W0 is set.

256 points is set.

Dedicated command

(RRPA)

Data link status is read.

Head I/O number of

master module

Parameter storage

head device

High-speed counter

module data link

is normal.

High-speed counter

module data link

is abnormal.

CH.1 pulse input mode/

function selection register/

hold-clear settings (RWw2)

Initial data processing

completion flag (RY78)

is ON.

Initial data processing

completion flag (RY78)

is OFF.

CH.1 count enable

(RY14) is ON.

CH.1 counter function

selection start command

(RY16) is ON.

CH.1 current value

(RWr0, RWr1) is read.

CH.1 counter function

selection start command

(RY16) is OFF.

CH.1 count enable

(RY14) is OFF.

* High-speed counter module status check

* Pulse input mode/function selection register/external output hold-clear settings

* Pulse count start

* Current value reading

Current value

reading

* Execution of count disable

* Stop of count disable

* Pulse count stop

Downloaded from ManualsNet.com search engine

Loading...

Loading...